如何加速PCIe仿真

电子说

描述

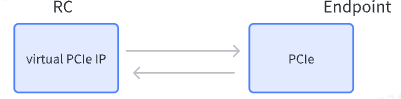

我们在进行PCIe RTL仿真时,由于PCIe ltssm协商过程比较复杂,导致PCIe ltssm进入L0状态所花费的时间比较长(大概在20~60分钟,因代码复杂度、服务器性能、PCIe速率不同而所有差异),而如果进行网表级别的仿真一般需要1周以上的时间。此时加速PCIe仿真,提高效率是我们必须考虑的问题。常见的加速模式有如下三种。我们以VIP PCIe(Verification IP,一种PCIe验证虚拟IP)对接Endpoint的仿真环境进行说明。  1、选择低速模式加速仿真 在测试某些与速率不相关的功能时,为了减少仿真时间,可以选择低速率模式,如选择gen1,gen2。特别是gen1(2.5Gbps)速率下,ltssm协商所需要的时间最短。适用于测试跟速率无关的功能,比如说用户逻辑功能的正确性。Gen3以及以上速率跟gen1/gen2比起来,多了均衡协商过程,此阶段耗时最多。 2、使用PIPE口仿真加速 在完整的PCIe协商过程中,PHY的link协商时间较长。如果对接VIP支持PIPE(phy-interface-pci-express)互连的话,可以bypass PHY,直接使用PIPE接口连接,即Endpoint PCIe PIPE口对接VIP PIPE,能够有效减少PCIe上电协商所需要的时间。侧重PCIe TL层功能点以及用户逻辑的测试用例,可以bypass PHY,使用PIPE口互连,测试PHY相关功能的用例不能使用此方法。 3、使用加速宏定义或者配置加速

1、选择低速模式加速仿真 在测试某些与速率不相关的功能时,为了减少仿真时间,可以选择低速率模式,如选择gen1,gen2。特别是gen1(2.5Gbps)速率下,ltssm协商所需要的时间最短。适用于测试跟速率无关的功能,比如说用户逻辑功能的正确性。Gen3以及以上速率跟gen1/gen2比起来,多了均衡协商过程,此阶段耗时最多。 2、使用PIPE口仿真加速 在完整的PCIe协商过程中,PHY的link协商时间较长。如果对接VIP支持PIPE(phy-interface-pci-express)互连的话,可以bypass PHY,直接使用PIPE接口连接,即Endpoint PCIe PIPE口对接VIP PIPE,能够有效减少PCIe上电协商所需要的时间。侧重PCIe TL层功能点以及用户逻辑的测试用例,可以bypass PHY,使用PIPE口互连,测试PHY相关功能的用例不能使用此方法。 3、使用加速宏定义或者配置加速

PCIe ctrl(TL层和DL层)和PHY在设计时为了方便用户测试,一般都添加了加速的手段,通常有2种手段:

1)代码顶层或者内部的部分的寄存器决定是否加速:

如果在顶层,可以通过配置寄存器 or 改变例化值的方式实现; 如果在内部,可以通过force的方式实现

2)通过宏定义实现:

例如VCS仿真时加上+define+AUTO_FAST_SIMULIATION,具体宏定义名称由IP确定。

加速原理 A)大幅减少链路状态机在各状态下的timeout时间,相对于正常模式,仿真模式下timeout时间可以减少至正常模式的千分之一或百分之一; B)大幅度减少训练成功所需序列的数量,例如连续接收到1000个序列表示当前状态训练成功,加速模式下可以只需要10个序列就能训练成功

审核编辑:彭菁

-

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计2025-08-07 1299

-

PCIe加速卡在数据中心的应用2024-11-06 2927

-

是德科技推出PCIe和UCIe仿真解决方案2024-07-30 1987

-

PCIe载板设计原理图:636-基于FMC的Kintex XCKU060高性能PCIe AD采集板卡 AI加速计卡2024-06-17 2125

-

PCIe 5.0设计面临的挑战以及仿真案例2023-02-03 8330

-

PCIe 5.0:加速云中的数据移动2022-11-21 1495

-

求一种基于Xilinx XCKU115的半高PCIe x8 硬件加速卡2021-06-25 1511

-

PCIe的SmartNIC如何改变方案加速规则2021-01-07 1915

-

加速FPGA的仿真方式之——脚本命令2020-05-14 4591

-

讲真,这绝对是加速FPGA的仿真过程的最佳方法2020-04-25 3333

-

PCIe加速卡的发展2019-06-24 4869

-

用于加速c代码的PCIe FPGA如何开始2019-01-24 2415

-

英特尔Optane On Secondary HDD无法加速PCIe驱动器2018-10-17 5897

-

基于Xilinx XCKU115的半高PCIe x8硬件加速卡2018-08-22 5050

全部0条评论

快来发表一下你的评论吧 !