具有铜互连的IC芯片设计

EDA/IC设计

描述

铜互连是一种比较新的技术。在经过深入的研究和开发后,具有铜互连的IC芯片产品第一次在1999年出现。而且铜互连这项技术已经应用于最小特征尺寸小于0.18um的IC芯片设计当中,也可以用于尺寸小于0.13um技术节点的更小的芯片,并已用于逻辑IC芯片制造。

由于双镶嵌工艺通过减少工艺流程而简化了铜互连工艺,所以铜互连的成本低于传统的钨/铝铜合金互连。铜互连已经成为先进IC芯片制造的主流互连技术。

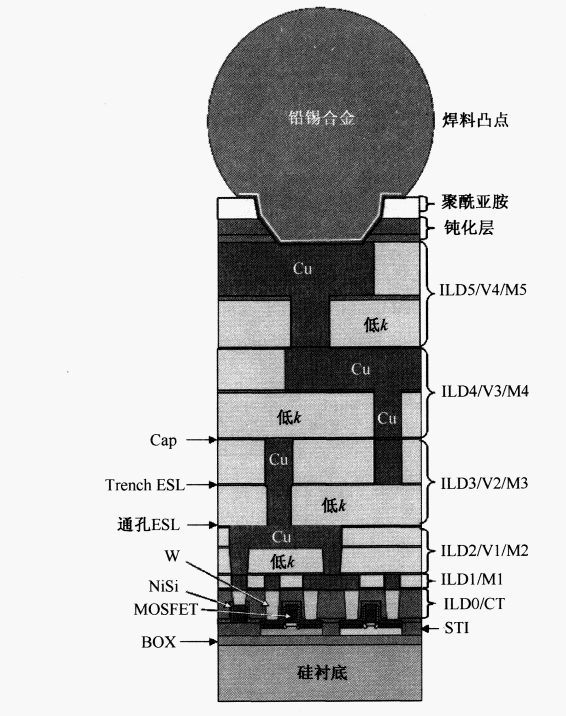

使用SOI衬底和铜/低k互连技术,设计者可以制造具有较高抗干扰和低功耗的快速、强大功能和可靠性高的IC芯片。下图显示了一个具有SOI衬底、铜和低k电介质互连的CMOS集成电路横截面示意图。

20世纪10年代CMOS工艺流程

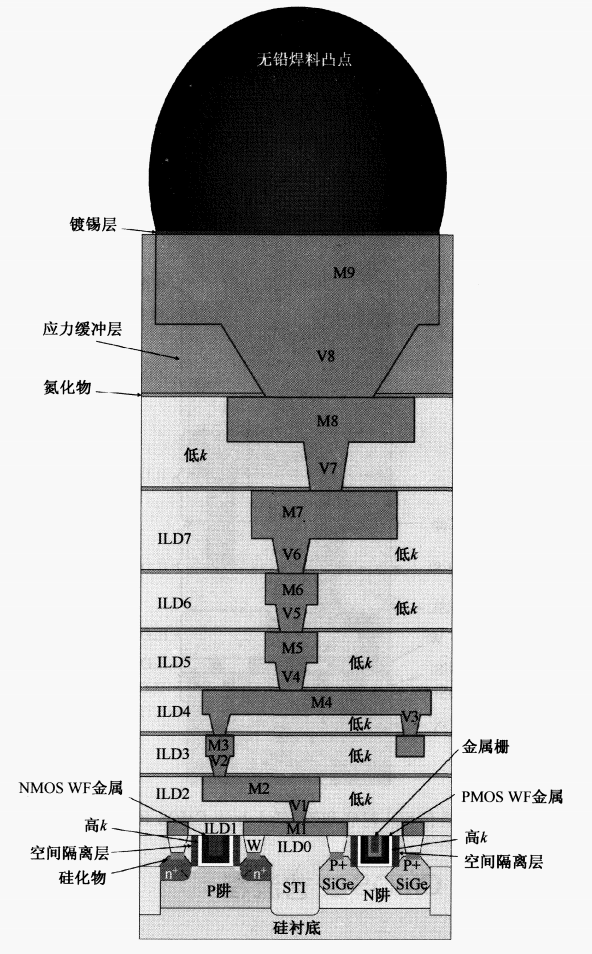

当就加工的半导体器件的尺寸不断缩小到45nm及更小的尺寸时候,如40nm、32nm/28nm和22nm/20nm后,栅氧化层的厚度已经达到极限,也就是说由于严重的漏电问题而不能再减小。高充栅介质已经被开发并取代了常用的二氧化硅和氮化氧化物(SiON)。

为了进一步提高器件的性能,金属栅取代了常用的多晶硅栅。应变工程广泛用于增强电子和空穴的迁移率提高器件的速度。硅错(SiGe)和碳化硅(SiC)选择性外延生长用于CMOS制造获得理想的沟道应变。自对准CoWP化学电镀技术被发展用于铜CMP后覆盖铜表面以防止铜扩散导致降低电迁移,从而可以提高铜互连的可靠性。金属(TiN)硬掩膜用于低为电介质刻蚀。

193nm浸入式光刻技术和双重图形化工艺用于图形化线间距,源光刻版优化(SMO)技术用于图形化接触窗和通孔。设计者必须与光刻技术人员和工艺团队紧密合作进行优化设计以实现高的成品率,这称为制造性设计。

下图显示了一个32nm/28nm的CMOS横截面图,这种结构具有后栅HKMG.SEGSiGe、应力记忆技术(SMT)、铜超低k互连,以及无铅焊料凸点。

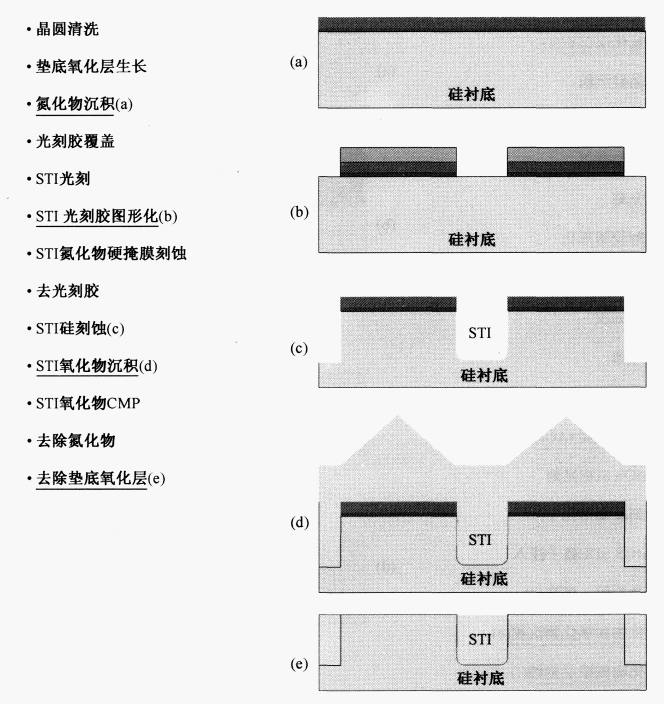

下图显示了STI的工艺过程,这与下图所示的STI过程看起来几乎相同,然而,由于器件尺寸的缩小,很多细节是不同的。例如,之前的介绍当中所演示的器件需要无应力STI填充,而下图所示的器件需要从STI氧化层获得额外应力帮助进一步提高沟道的应变。

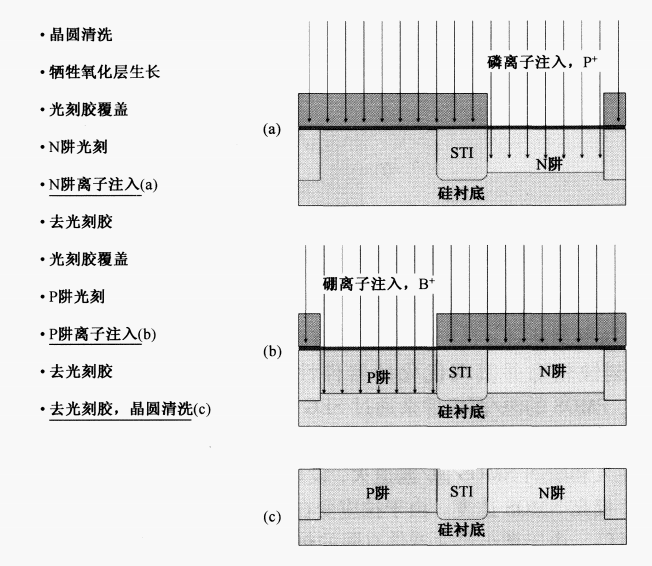

下图显示了阱区注入和片调整注入形成双阱CM0S。由于器件尺寸的缩小,结的深度比之前介绍内容中所演示的阱区注入的浅。

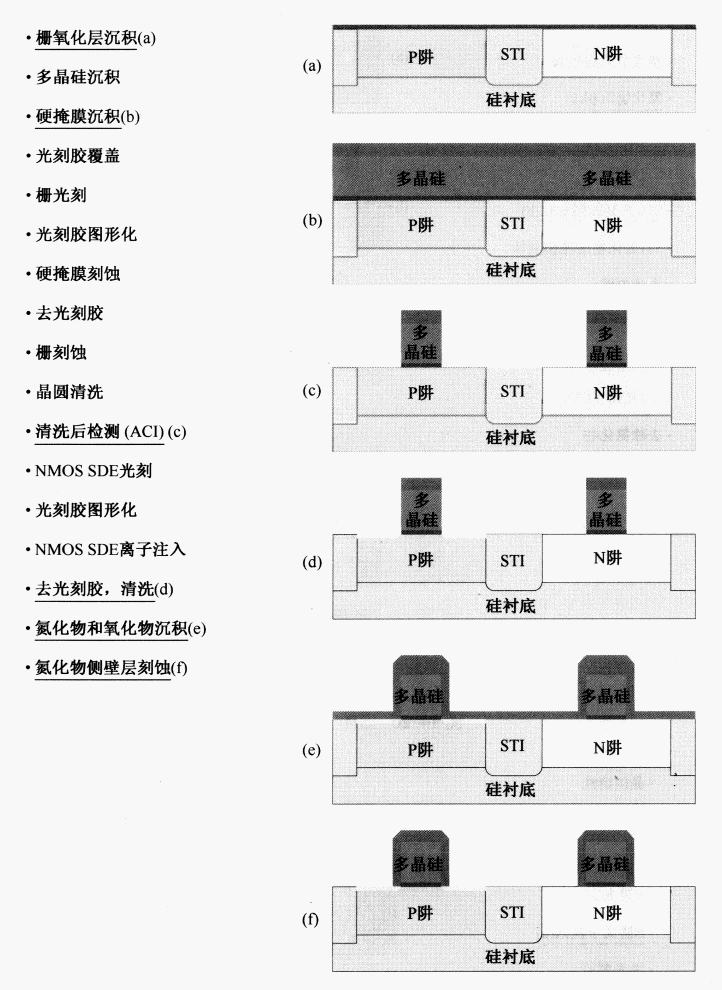

下图显示了栅极、NMOS源/漏极扩展(SDE)和侧壁间隔层的形成过程。由于PMOS的源/漏极利用选择性外延生长(SEG)SiGe形成,这种工艺通过SEG过程中重掺杂P型而形成,所以PMOS并不需要SDE或SD注入。不同于之前的工艺,这种多晶硅栅只是一种过渡栅,将用高k和金属栅在后续的工艺中取代。这种工艺不需要多晶硅注入,栅的功函数由PMOS和NMOS的不同金属栅材料控制。

审核编辑:刘清

-

MACOM公司推出高密度铜互连解决方案2026-03-20 864

-

铜对芯片制造中的重要作用2025-07-09 2710

-

一文详解铜互连工艺2025-06-16 4727

-

铜互连,尚能饭否?2024-07-02 1463

-

将铜互连扩展到2nm的研究2023-11-14 1165

-

先进封装中硅通孔(TSV)铜互连电镀研究进展2023-09-06 2706

-

提高铜互连优势的方法2023-02-17 3289

-

铜互连,还能撑多久?2022-12-19 1939

-

铝/铜互连工艺与双镶嵌法(AL/Cu Interconnect and Dual Damascenes)2022-11-24 11986

-

光互连技术2016-01-29 2844

-

集成电路片内铜互连技术的发展2010-05-04 578

-

新型铜互连方法—电化学机械抛光技术研究进展2009-10-06 7376

-

均衡千兆位铜缆连接的IC2009-04-22 819

全部0条评论

快来发表一下你的评论吧 !