RTL设计规范有哪些?一个RTL用例设计介绍

描述

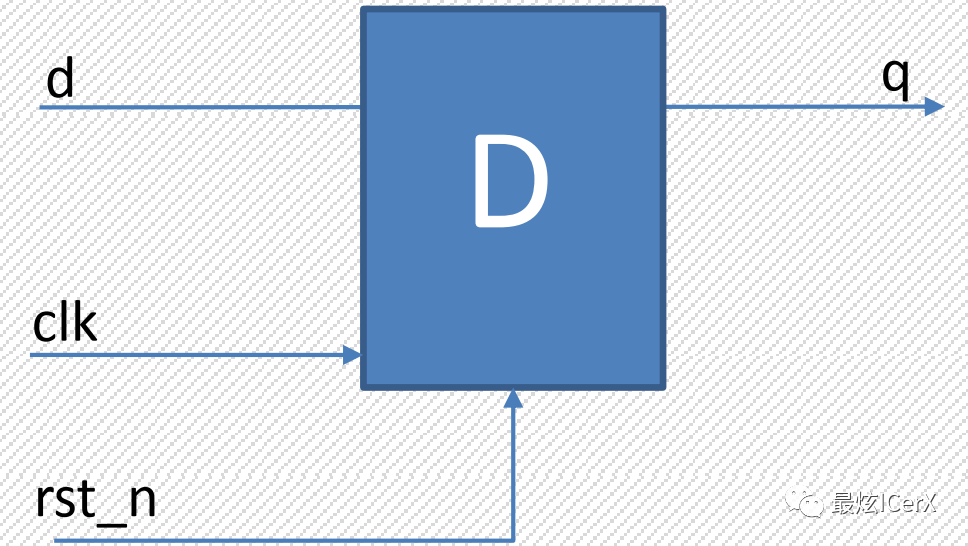

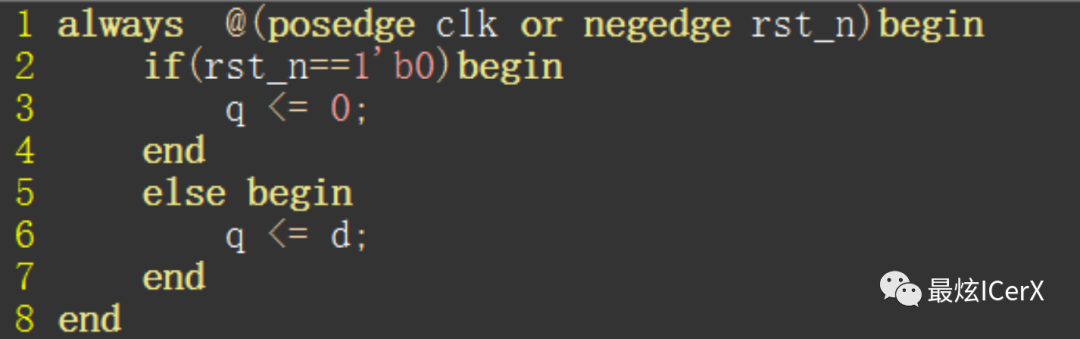

1、D触发器及代码

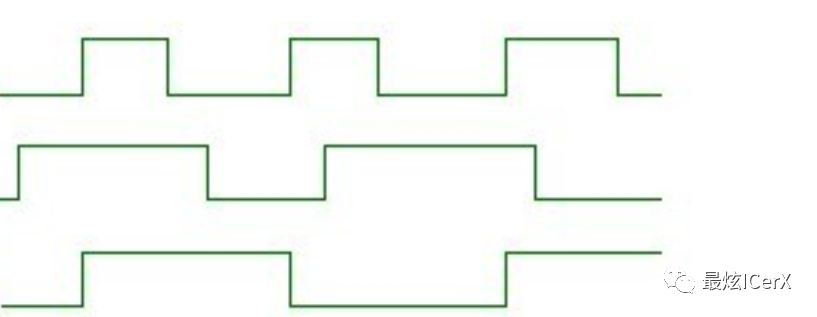

D触发器结构如下图所示,先有时钟上升沿,然后才有D的值赋给Q,没有上升沿Q值保持不变,时序逻辑在时钟上升沿/下降沿后才变化

2、硬件设计思维

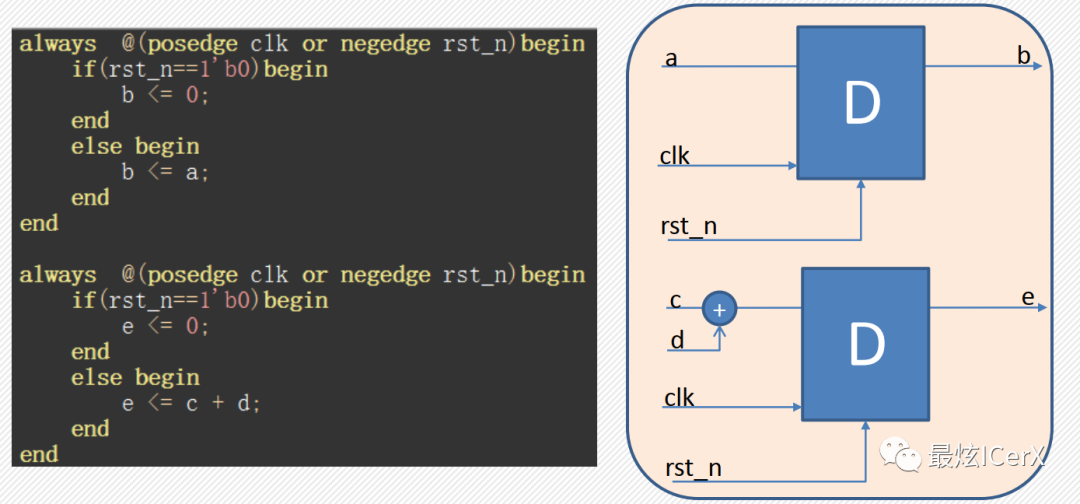

如下图所示,一个always对应一个D触发器,一个信号,always,模块就是一个元器件

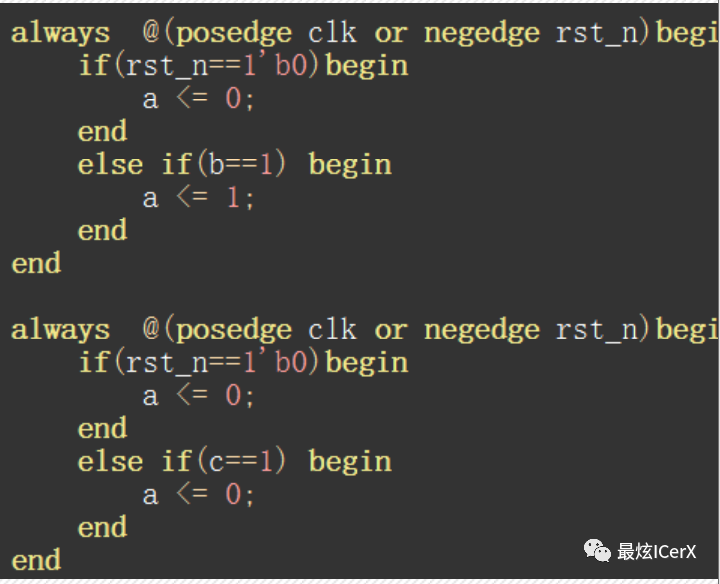

如下图所示,一个信号不能在多个always中设计,一个信号在一个always

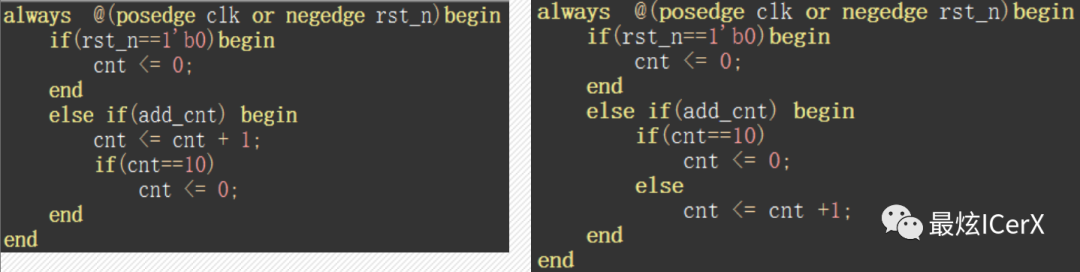

如下图对比,左边为软件思维描述过程,右边是硬件思维是描述功能,

硬件设计思路应逐个定义好每个信号/元器件的功能,然后连接,根据每个信号的功能画波形,来实现最终目标

3、一个RTL用例设计

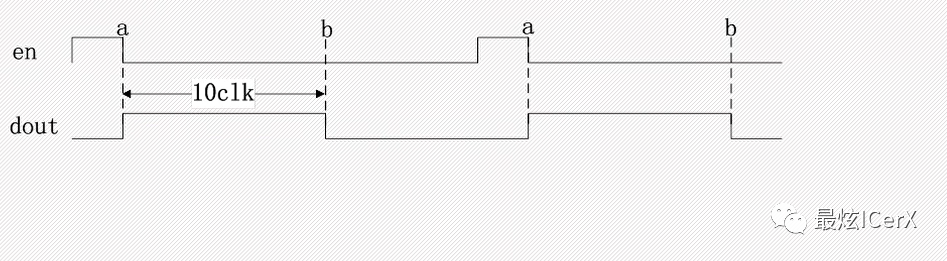

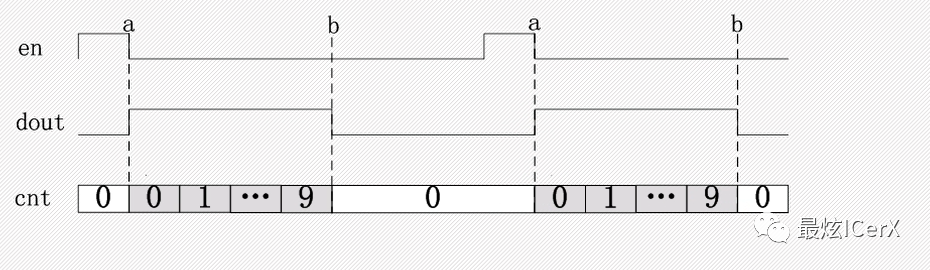

计数器用例,要求:当收到en后,dout产生一个宽度为10个时钟周期的高电平脉冲,信号示意如下,这是一个计数器用例,硬件设计步骤分解如下

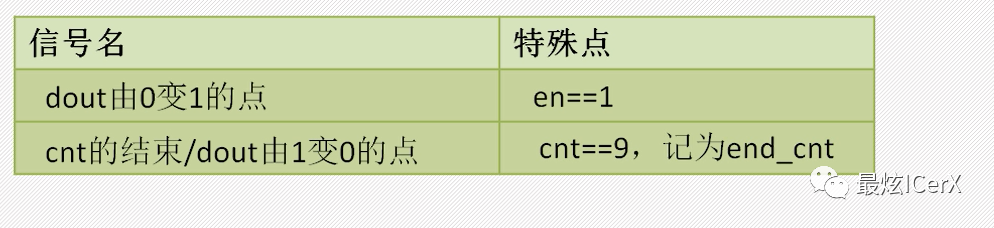

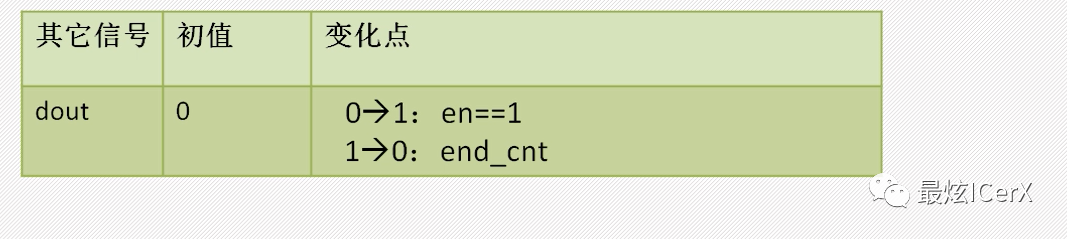

第一步明确功能,确定信号真值表。

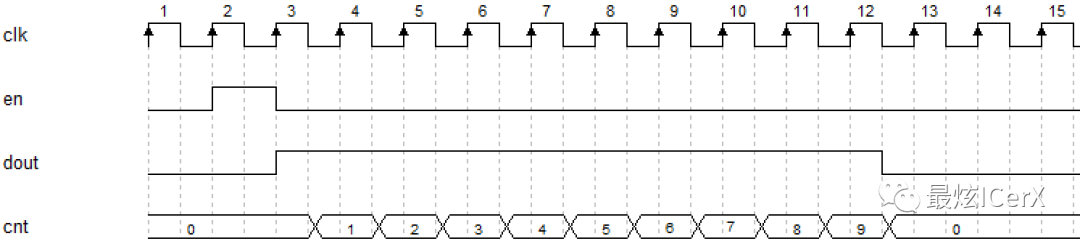

第二步画出功能波形,通过Timegen绘制如下信号波形,详细用法可阅读软件---TimeGen安装与使用,本用例所有信号都是在时钟上升沿过后进行判断的,下图en是在clk第三个上升沿时完成判断,记住先有时钟再有信号。

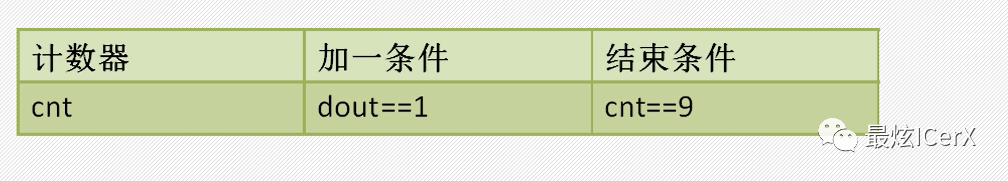

第三步明确计数器结构,本设计计数器默认都是从0开始计数

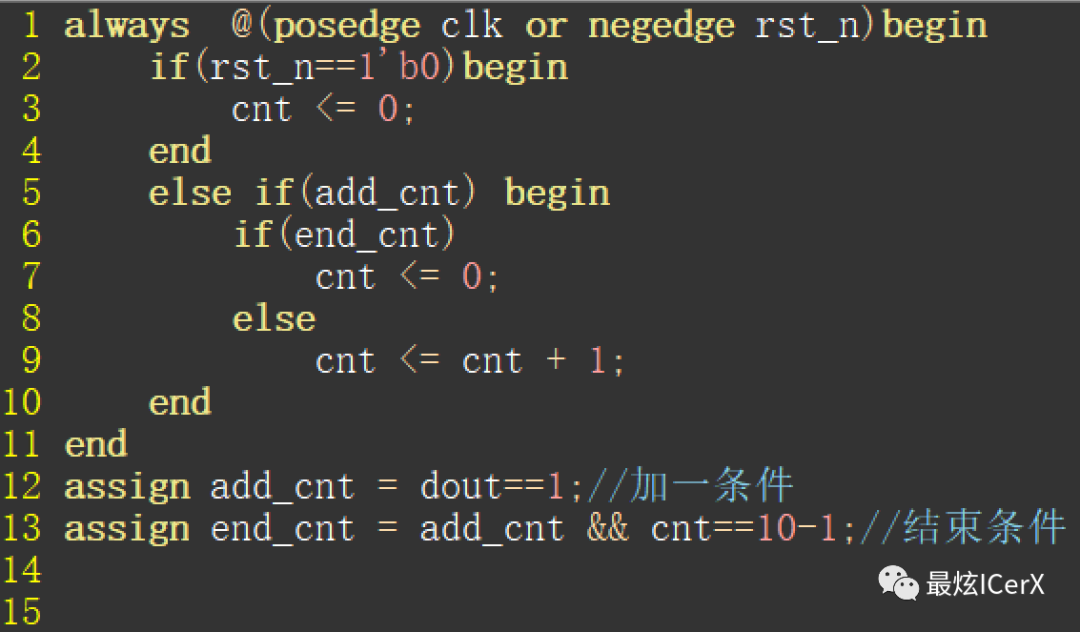

第四步明确计数器结构,确定设计中的加一及结束条件,代码如下,下面代码可作为计数器代码通用模板

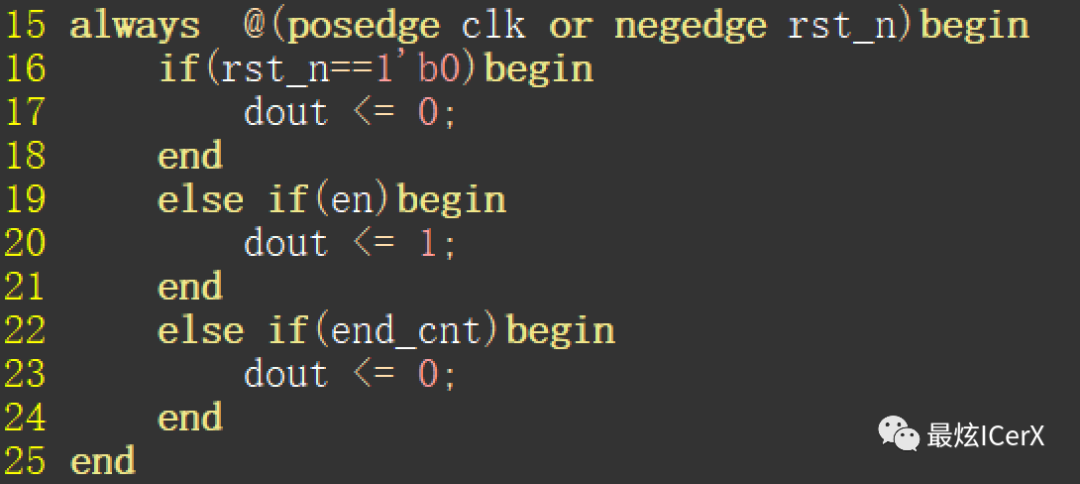

第五步定义特殊点,编写输出信号变化情况,如下代码

第六步完整性检查

第七步编写计数器代码,见上述计数器代码

第八步功能代码,见上述输出信号dout代码,补全其它代码

总结设计,规范硬件设计思路,第一步-->第二步......,按照步骤实现,检查设计过程。本设计中首先画出信号波形,接着确定计数器结构,接着确定计数器加一与结束条件,接着确定输出信号变低,变高时间点及条件,最后写计数器代码,输出信号代码,接口定义。接下来会继续介绍Verilog设计规范及对应用例。

审核编辑:刘清

-

RTL8187和RTL8225USB无线网卡电路图与RTL822电路图2022-09-07 1687

-

在SpinalHDL的设计中集成现有RTL设计(IP)的渠道——BlackBox2022-06-22 1724

-

RTL8188和RTL8192吞吐量网卡驱动的开发工具合集(软件程序介绍)等2018-07-02 2077

-

RTL8306SD和RTL8306SM应用参考电路pdf2018-03-09 2328

-

RTL8196EU_RTL8188ER参考原理图pdf2018-03-07 3304

-

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF2017-10-25 1805

-

RTL8196D+RTL8192ER2016-09-20 9857

-

RTL8308+RTL4204交换机原理图2010-10-18 2604

-

RTL,RTL是什么意思2010-03-08 14815

-

昂达Realtek/RTL8169/ RTL8169S(B)2010-01-26 771

全部0条评论

快来发表一下你的评论吧 !