【华秋干货铺】DDR电路的PCB布局布线要求

电子说

描述

由于RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,DDR模板是经过严格的仿真和测试验证后发布的。

在单板PCB设计空间足够的情况下,优先考虑留出DDR电路模块所需要的布局布线空间,拷贝瑞芯微原厂提供的DDR模板,包含芯片与DDR颗粒相对位置、电源滤波电容位置、铺铜间距等完全保持一致。

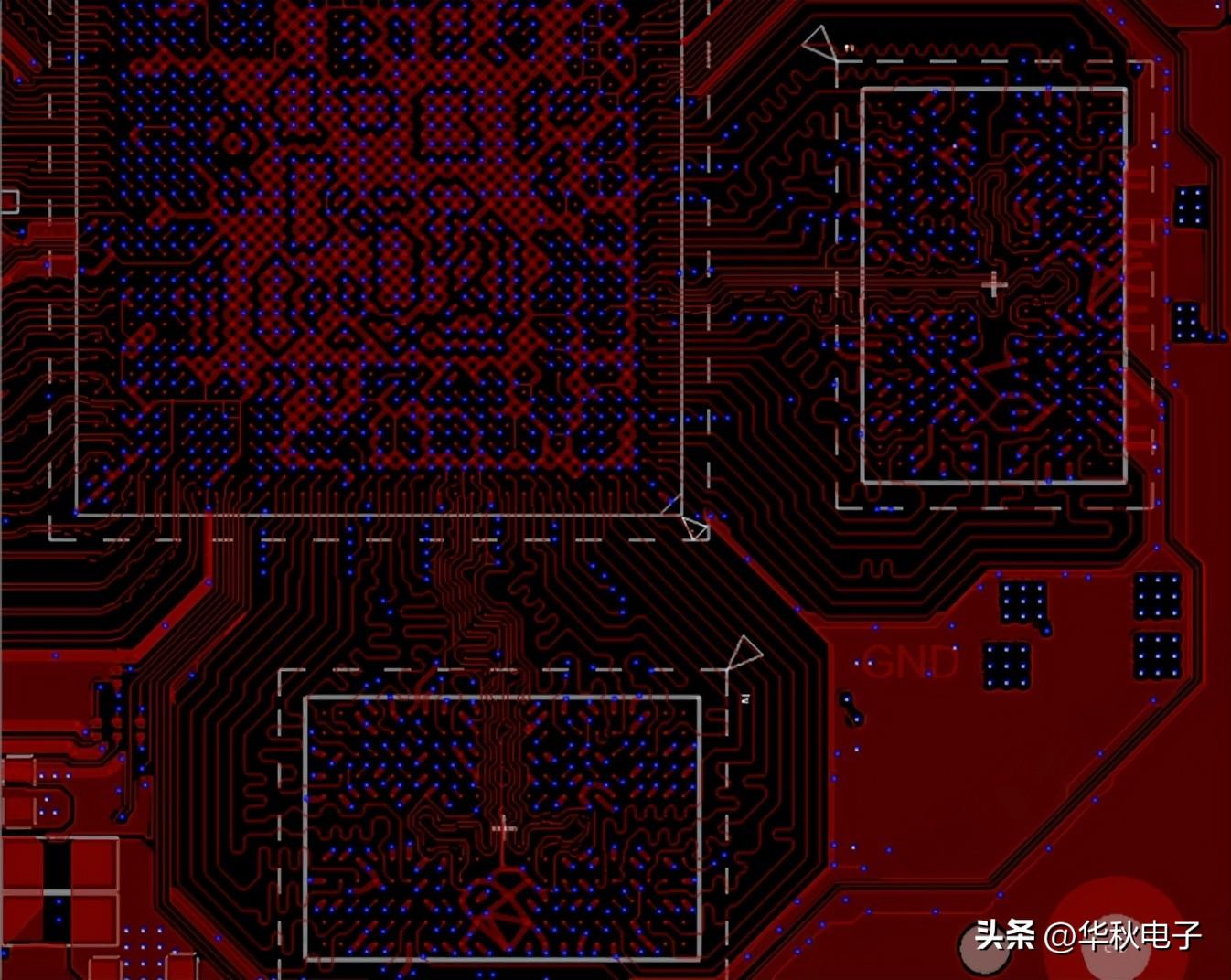

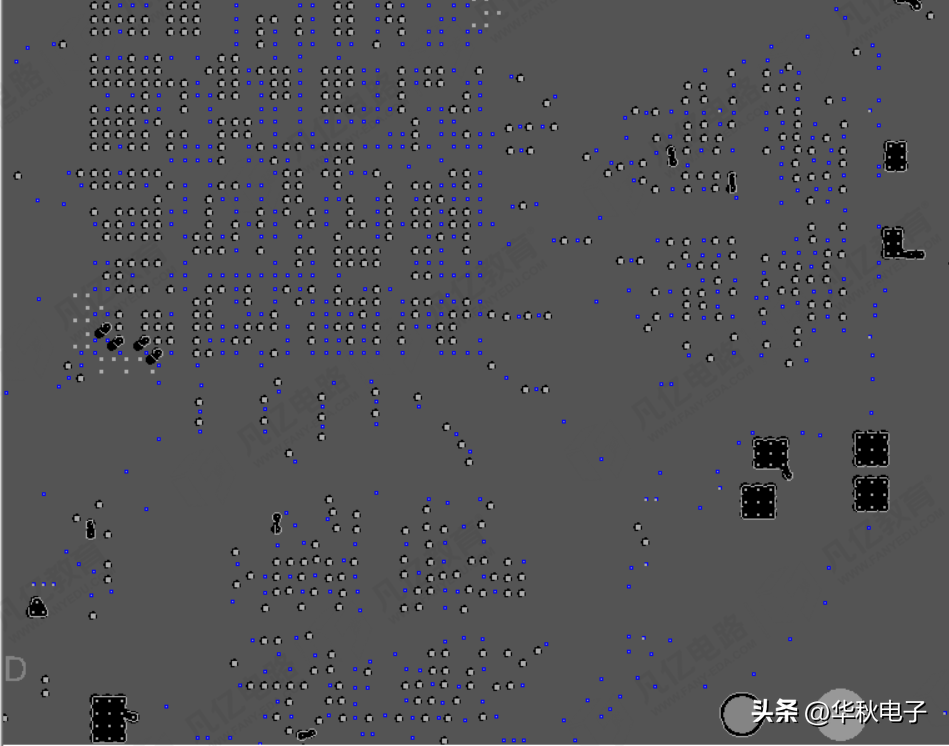

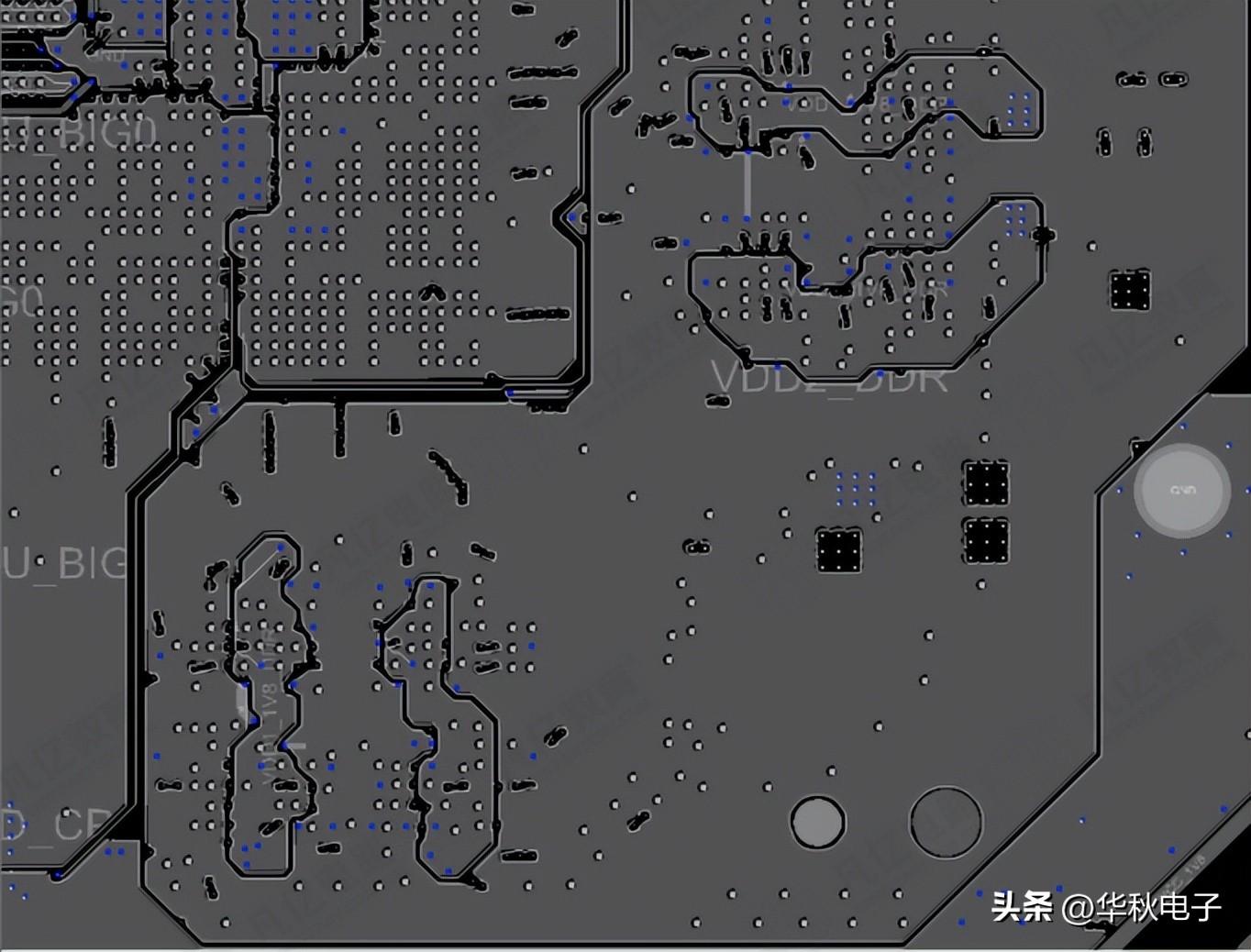

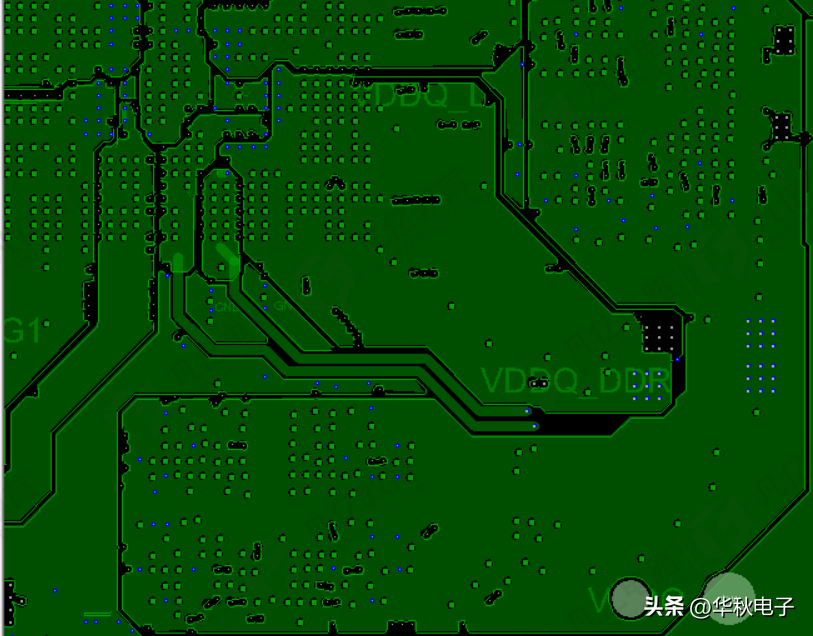

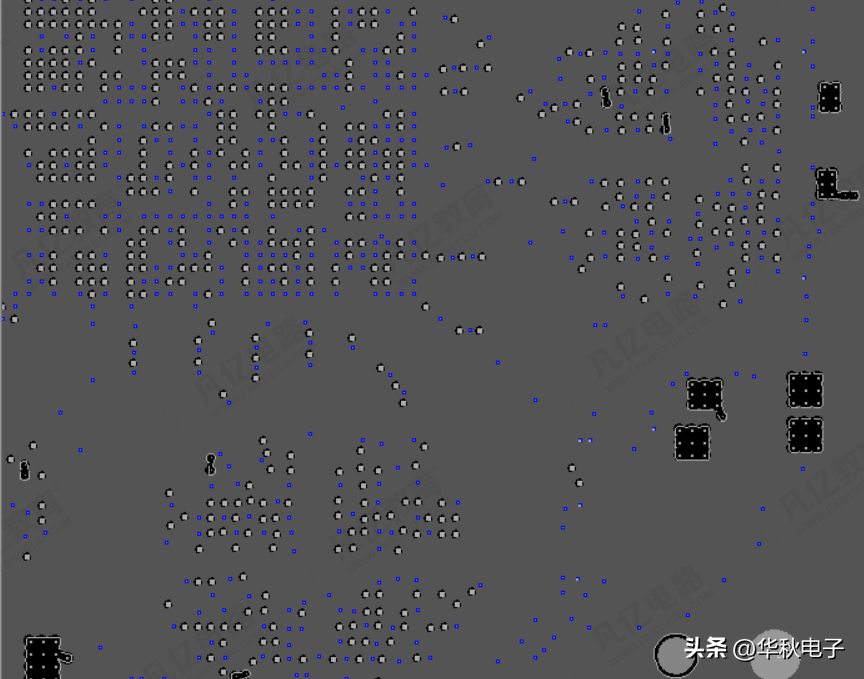

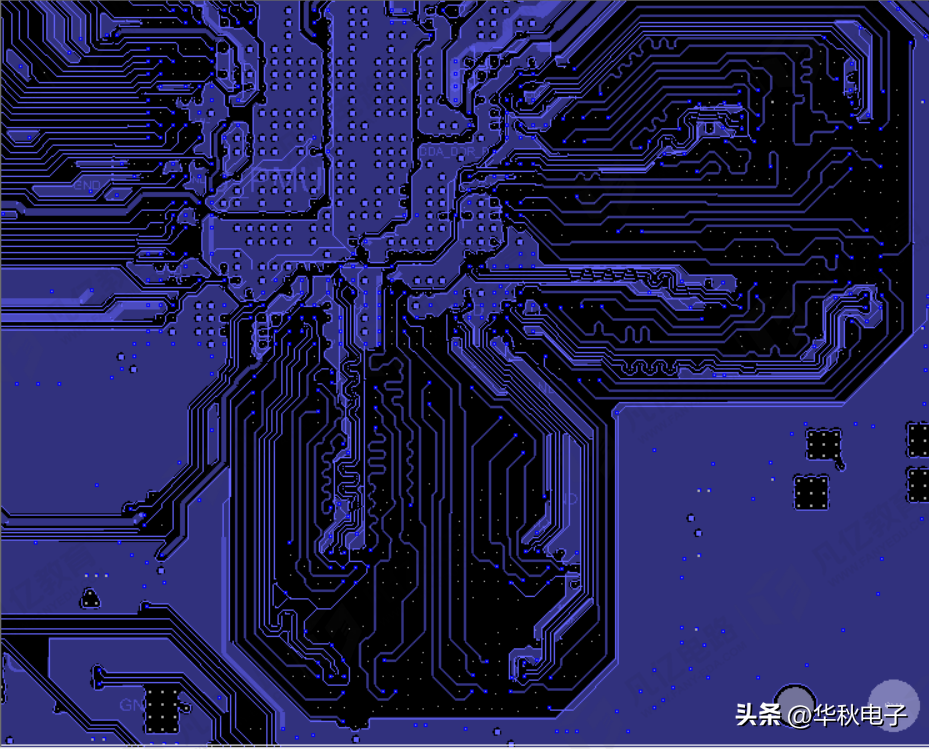

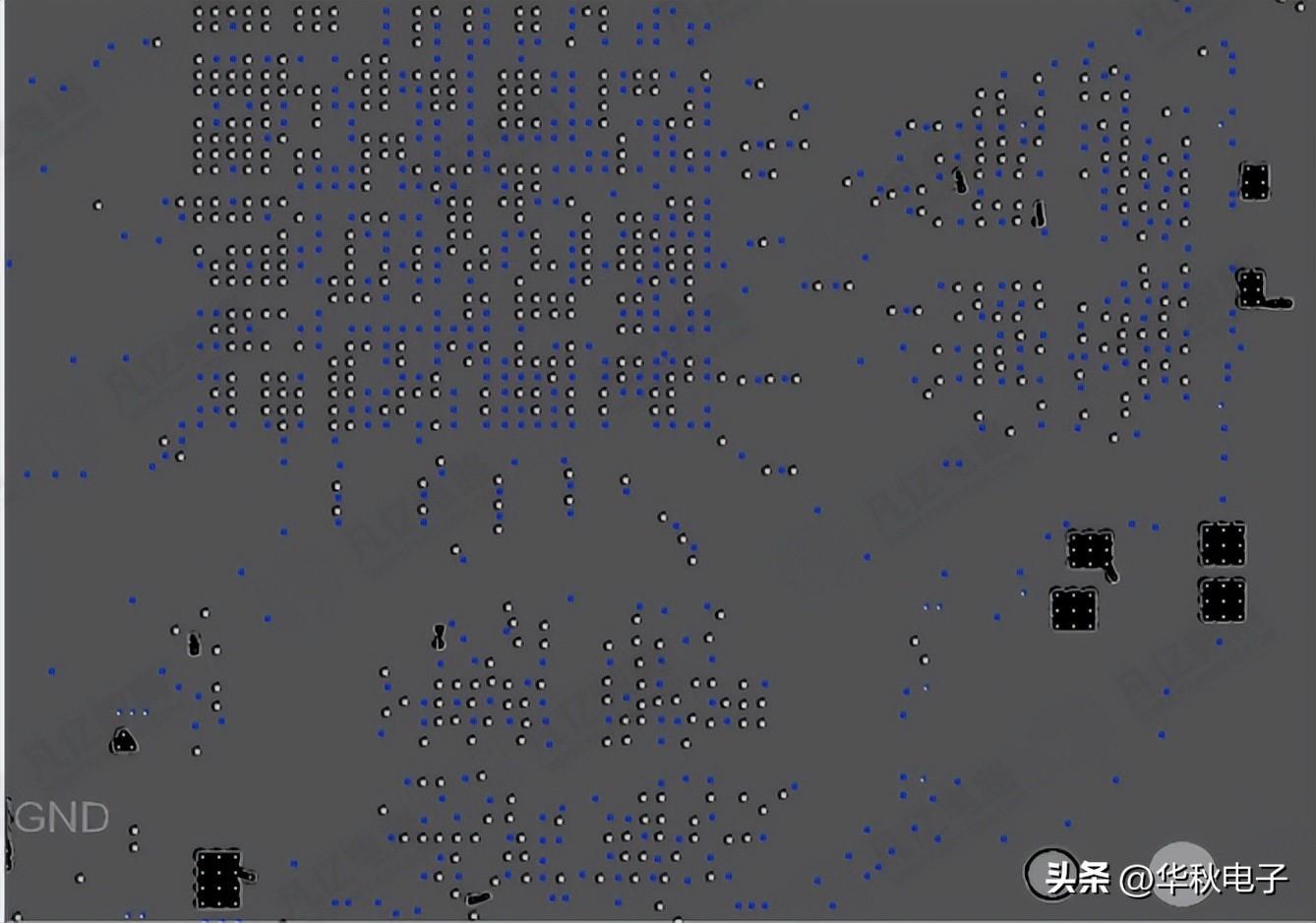

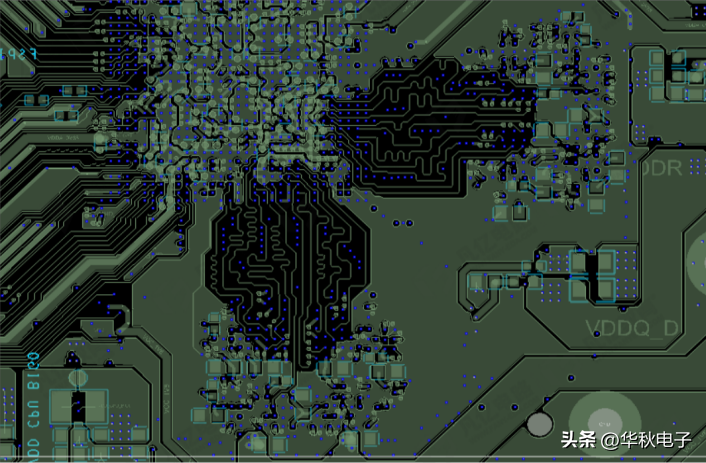

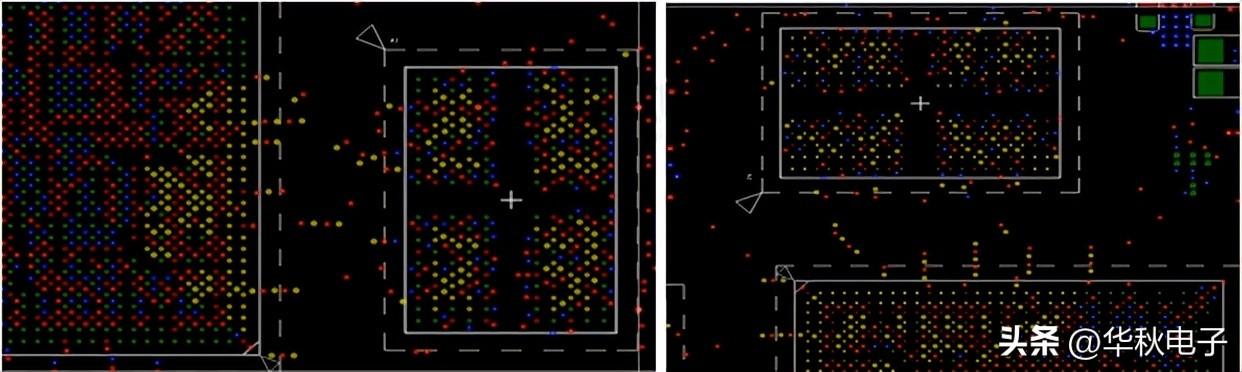

如下8张图(从左至右),分别为:L1-L8层DDR电路走线示意图。

如果自己设计PCB,请参考以下PCB设计建议,强烈建议进行仿真优化,然后与瑞芯微原厂FAE进行确认,确认没问题以后再进行打样调试。

Part.1

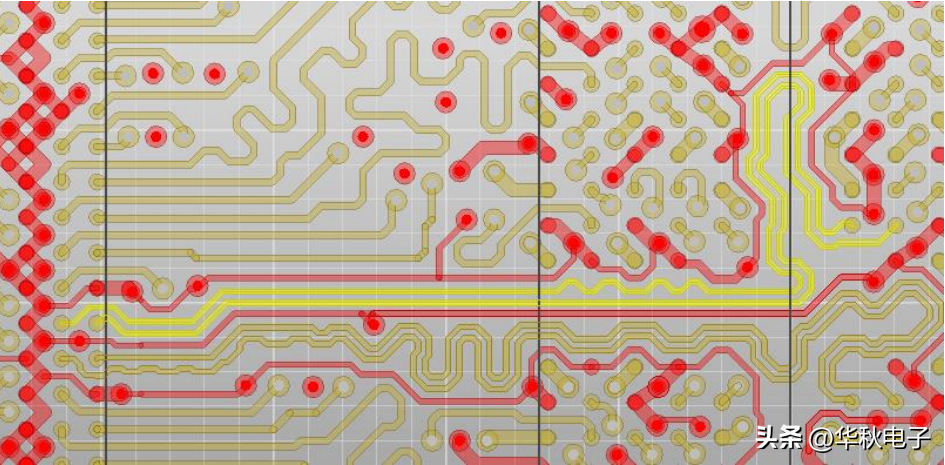

CPU管脚,对应的GND过孔数量,建议严格参考模板设计,不能删减GND过孔。8层通孔的PCB模板,CPU管脚GND过孔设计如下图所示,黄色为DDR管脚信号,地管脚为红色。

Part.2

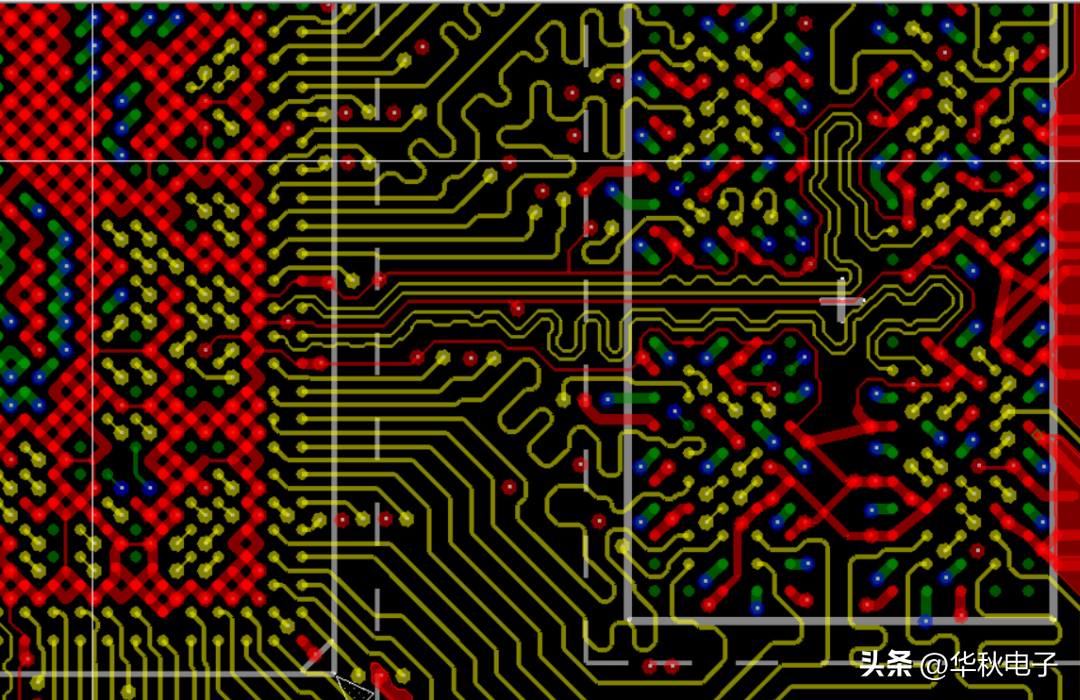

信号换层前后,参考层都为GND平面时,在信号过孔25mil(过孔和过孔的中心间距)范围内需要添加GND回流过孔(黄色为DDR信号,红色为GND信号),改善信号回流路径,GND过孔需要把信号换层前后GND参考平面连接起来。

一个信号过孔,至少要有一个GND回流过孔,尽可能增加GND回流过孔数量,可以进一步改善信号质量,如下图所示。

Part.3

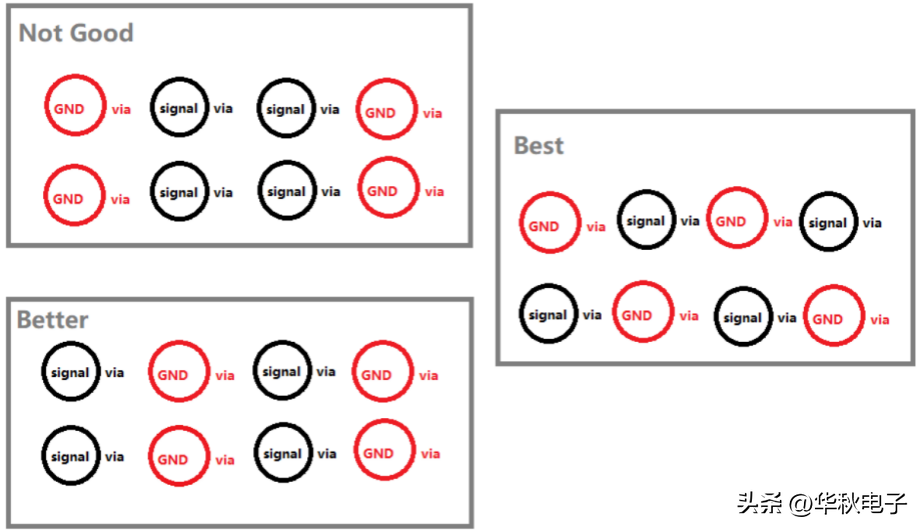

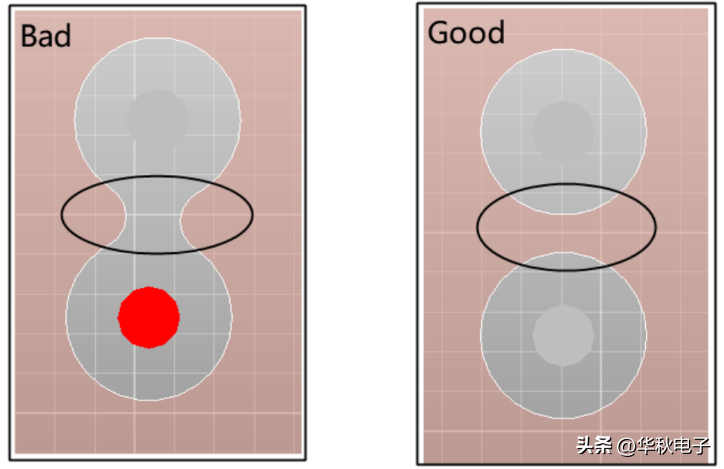

GND过孔和信号过孔的位置会影响信号质量,建议GND过孔和信号过孔交叉放置,如下图所示,虽然同样是4个GND回流过孔,4个信号过孔在一起的情况要避免,这种情况下过孔的串扰最大。

Part.4

8层板建议DDR信号走第一层、第六层、第八层,DQ、DQS、地址和控制信号、CLK信号都参考完整的GND平面,如果GND平面不完整,将会对信号质量造成很大的影响。

Part.5

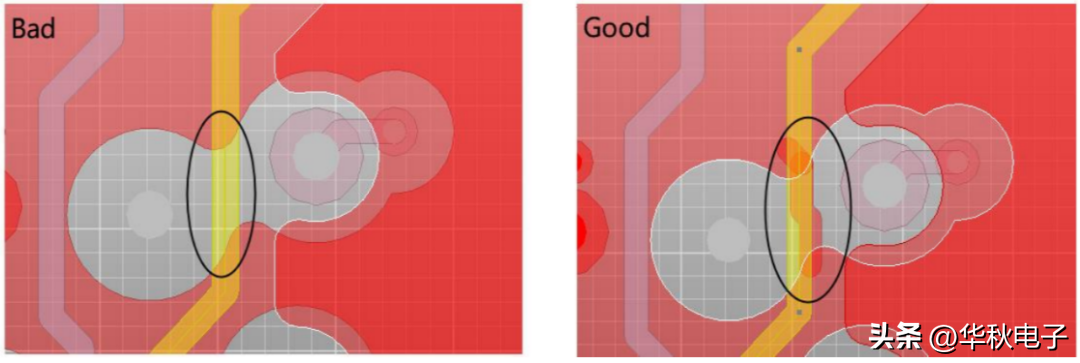

如下图所示,当过孔导致信号参考层破裂时,可以考虑用GND走线优化下参考层,改善信号质量。

Part.6

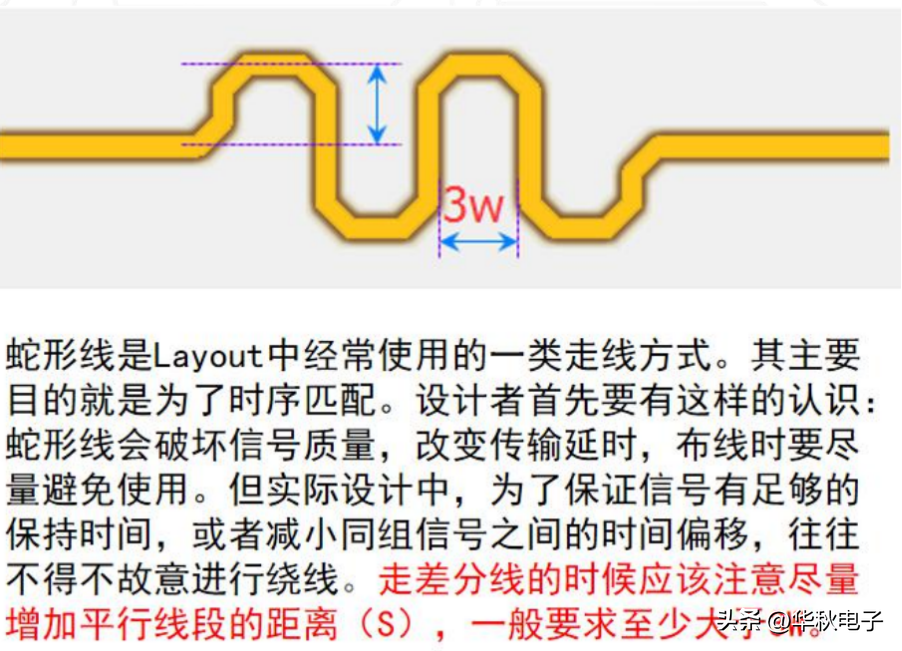

绕线自身的串扰会影响信号延时,走线绕等长时,注意按下图所示。

Part.7

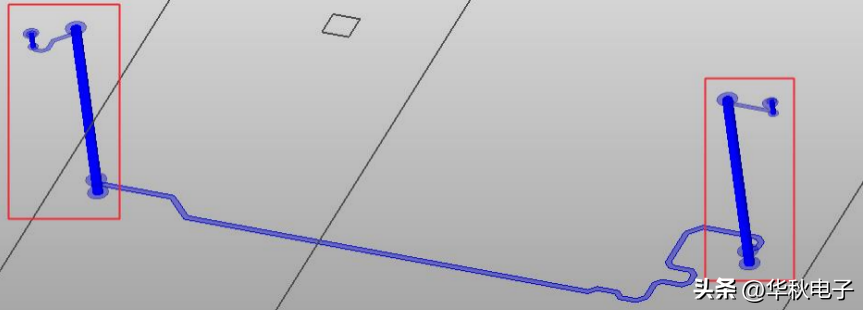

在做等长时,需要考虑过孔的延时,如下图所示。

Part.8

非功能焊盘会破坏铜皮,以及增大过孔的寄生电容,需要删除过孔的非功能焊盘,做无盘设计。

Part.9

走线距离过孔越近,参考平面越差,走线距离过孔钻孔距离建议≧8mil,有空间的地方增大间距。

Part.10

调整过孔位置,优化平面的裂缝,不要造成平面割裂,起到改善回流路径的作用,如下图所示。

Part.11

DQS、CLK、WCLK信号需要做包地处理,包地线或铜皮建议间隔≦400mil,打一个GND过孔,如下图所示。

Part.12

对于VDD_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.13

对于VDDQ_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.14

对于VDD2_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.15

对于VDD1_1V8_DDR电源,电源平面换层时,建议至少打≧2个0402过孔。

Part.16

每个电容焊盘建议至少一个过孔,对于0603或者0805封装的电容建议一个焊盘对应两个过孔,过孔的位置要靠近管脚放置,减小回路电感。

设计完PCB后,一定要做分析检查,才能让生产更顺利,这里推荐一款可以一键智能检测PCB布线布局最优方案的工具:华秋DFM软件,只需上传PCB/Gerber文件后,点击一键DFM分析,即可根据生产的工艺参数对设计的PCB板进行可制造性分析。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

审核编辑 黄宇

-

【PCB设计干货】DDR电路的PCB布局布线要求2023-08-24 3248

-

【华秋干货铺】DDR电路的PCB布局布线要求2023-08-17 1104

-

DDR电路PCB布局布线技巧2023-08-16 4371

-

【华秋干货铺】电源PCB设计汇总2023-08-10 2177

-

【华秋干货铺】PCB布线技巧升级:高速信号篇2023-08-03 1765

-

【干货分享】华秋干货铺 | PCB铺铜的DFM(可制造性)设计要点2022-12-01 2879

-

华秋干货铺 | PCB铺铜的DFM(可制造性)设计要点2022-11-24 2029

全部0条评论

快来发表一下你的评论吧 !