基于STM32H7 EXTI+SPI+DMA双缓冲应用演示

描述

最近有STM32用户咨询---如何基于STM32H7系列芯片用EXTI0中断同步触发SPI DMA并实现DMA双缓冲功能。当然,在论坛上也有发布类似咨询帖。其实,老早之前我算是未雨绸缪地在本公众号分享了有关使用DMAMUX模块通过EXTI同步触发其它DMA请求的文章和关于DMA双缓冲应用原理介绍与参考实现代码。

STM32 MCU家族中里很多系列内置DMAMUX模块,该模块可以基于某些特定事件,比如某些EXTI事件、定时器触发输出、DMA完成事件来生成DMA请求;有了它,DMA请求与DMA通道的关联可以实时编程,不再事先硬件锁定DMA请求与DMA响应通道的连接逻辑。我这里不对DMAMUX做详细介绍,有需要的请阅读STM32系列手册的相关章节或他人的相关解读。

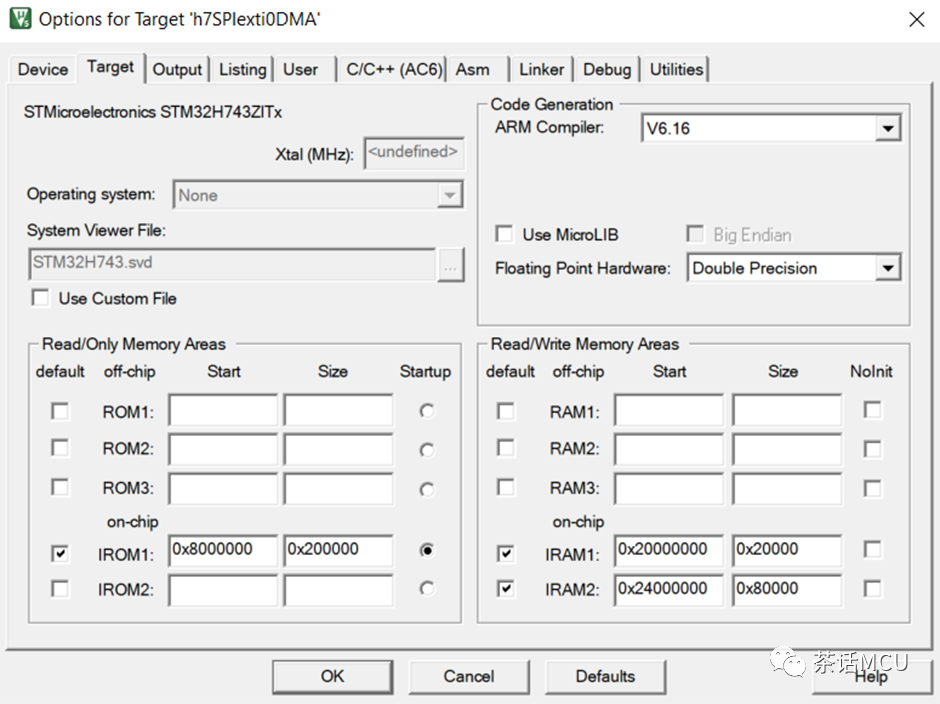

今天重点就咨询者的问题,基于AMR MDK开发环境、STM32H743Nucleo 开放板做一下实验演示,供有需要的同仁参考。

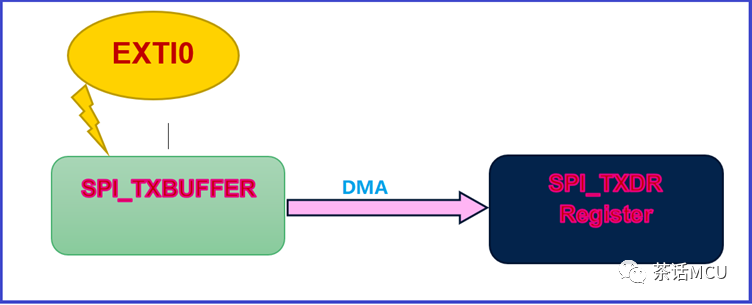

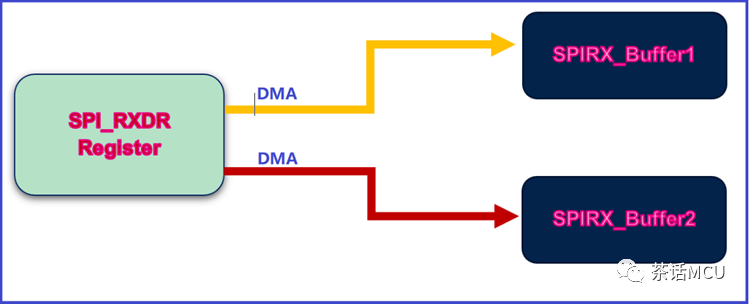

现在要实现的大致功能是,EXTI0中断作为SPI DMA发送的同步事件,SPI DMA接收采用双缓冲模式,即接收用到2个独立的缓冲区。我在测试时将SPI的发送、接收脚短接,自发自收并工作在Master全双工模式。【这里用到的DMA为通用DMA,既非MDMA也非BDMA。下面两幅图是SPI收、发实现的功能框架,具体使用SPI1。】

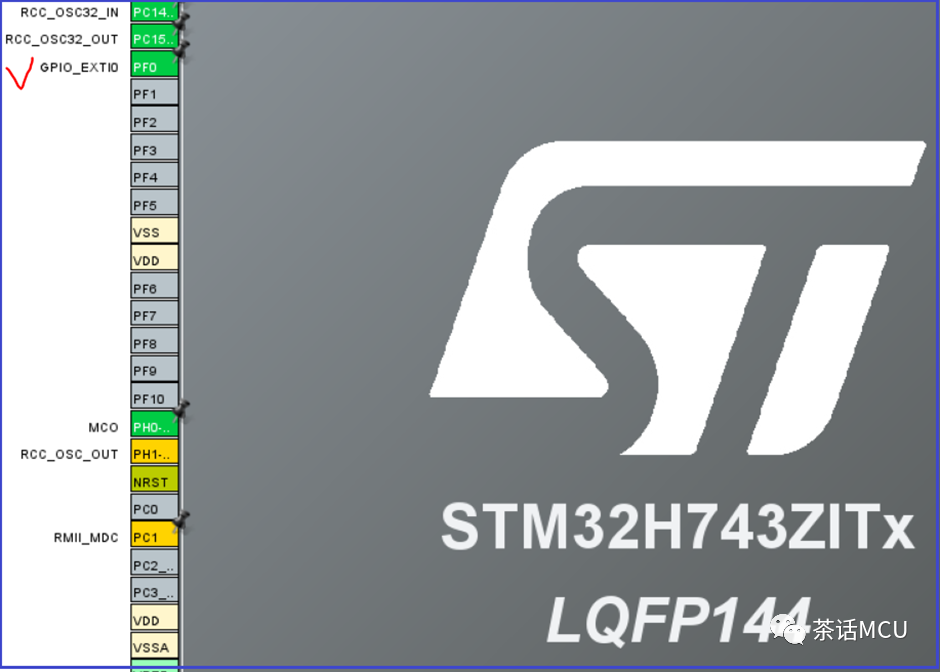

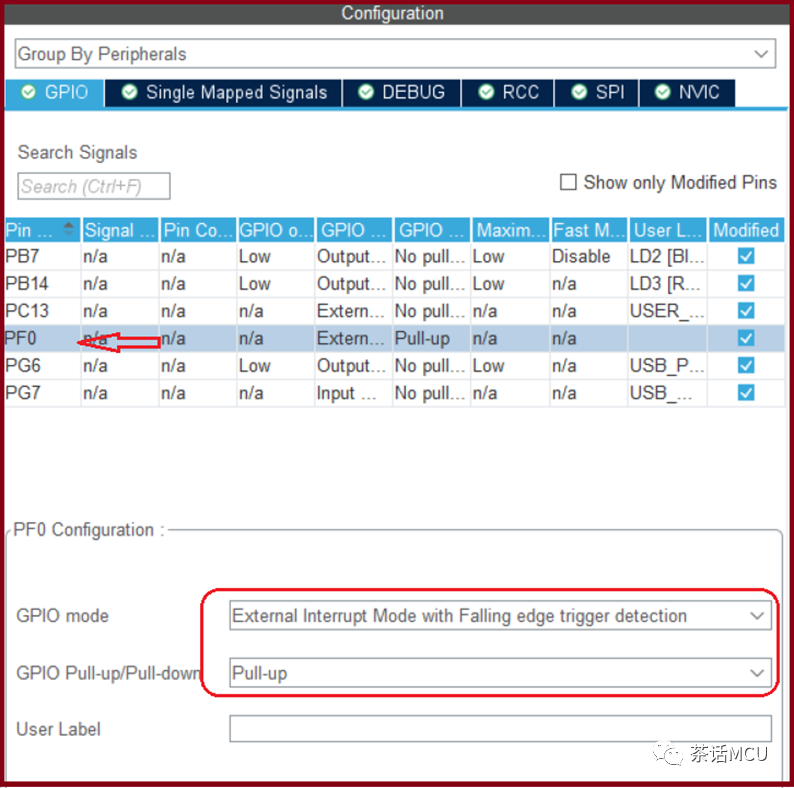

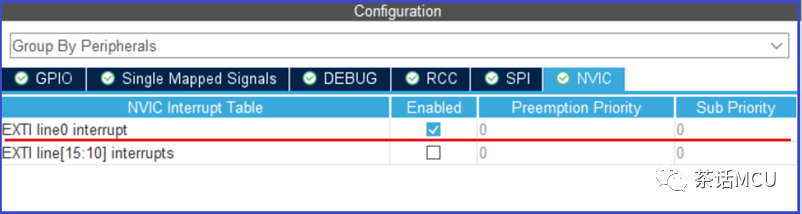

我使用到PE0管脚【只要是某个GPIO端口的0号脚即可】,开启其外部中断功能。下面都是使用STM32CubeMx图形化配置工具进行配置。

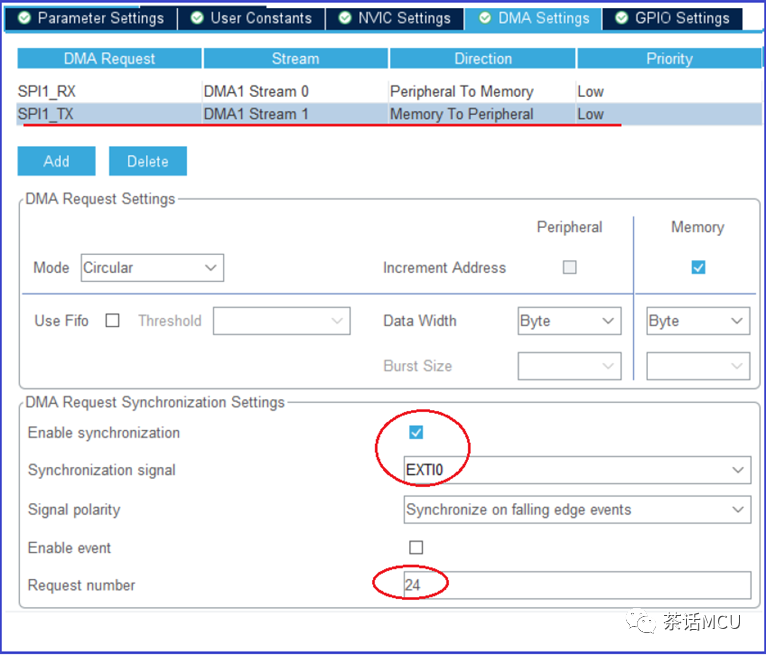

使用EXTI0作为SPI DMA发送功能的同步事件。即SPI的DMA发送须得到EXTI0事件的触发方可启动。每产生1个EXTI0事件就给SPI 申请24个 DMA发送请求,并让SPI DMA发送工作在循环模式。

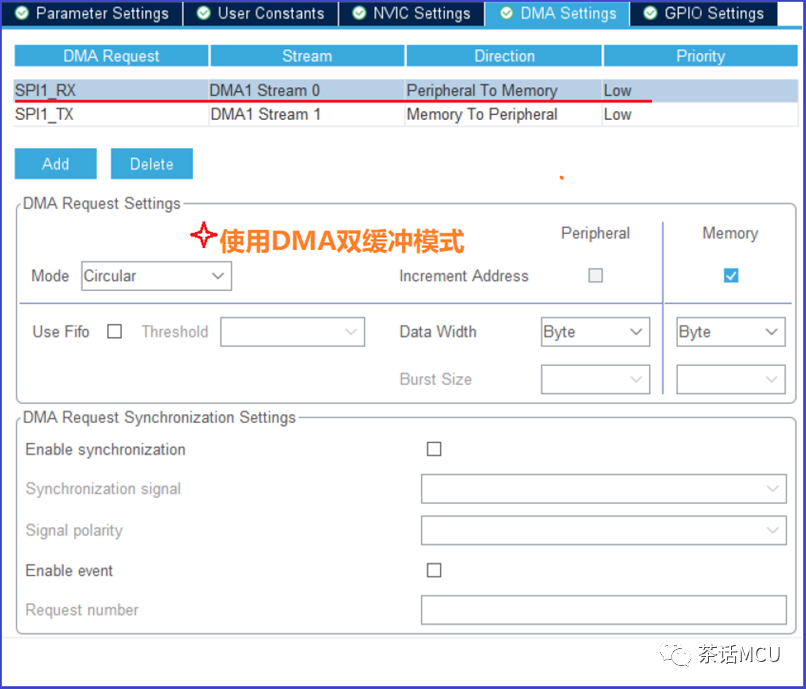

同时开启SPI的DMA接收功能,并使用DMA双缓冲模式进行接收。

使用CubeMx配置完成后,建立工程。基于ARM MDK的基本存储配置截图如下:

说明下,这里我没有开启D-Cache,也没有使用DMA FIFO。实际应用中自行开启并做适当配置及处理。关于EXTI0的产生,我刚开始是使用跳线短接地验证的,但这样操作很不方便,我后来改为软件方式触发EXTI0中断。最后测试时,我每2秒产生一个EXTI0中断,进而触发SPI通信。

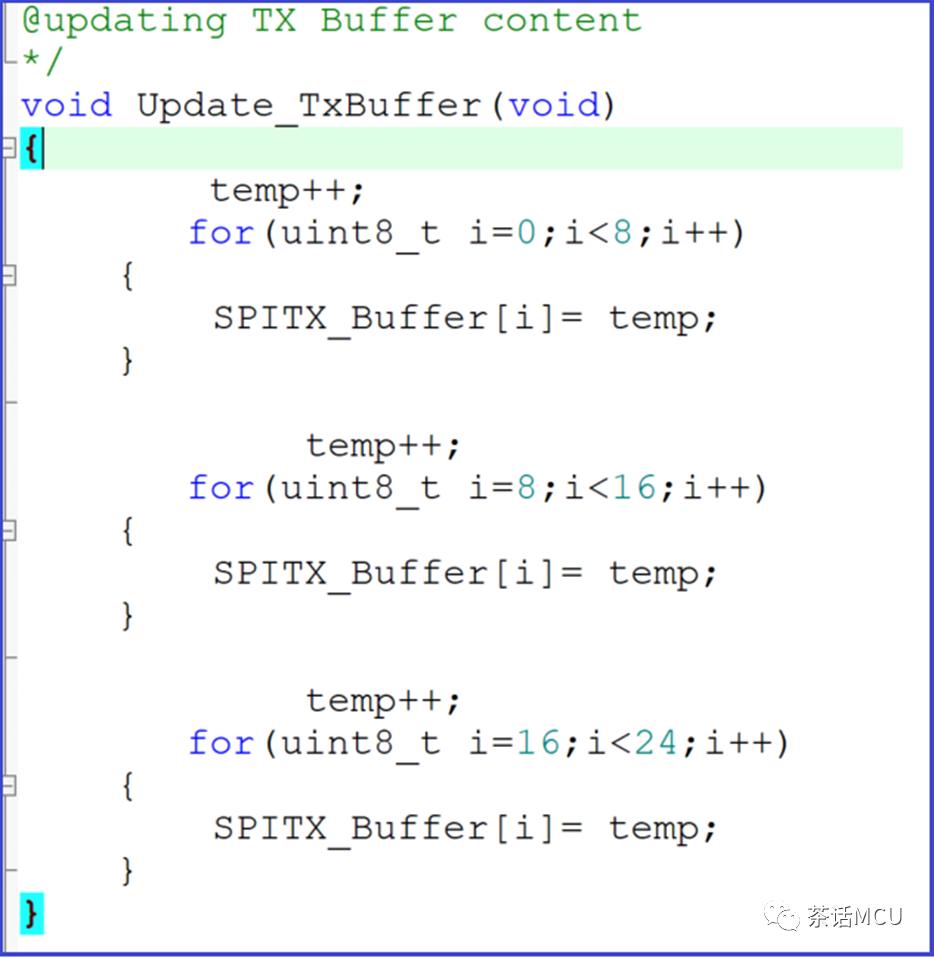

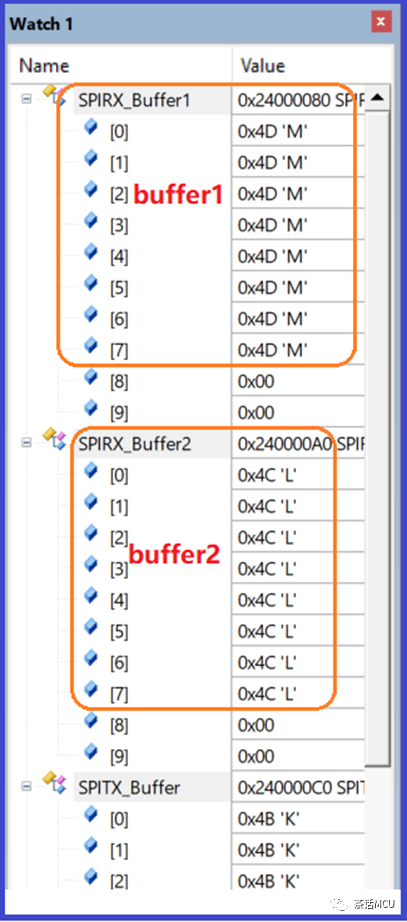

每产生1次EXTI0中断,则SPI使用DMA方式发送24个字节数据。SPI的DMA接收采用双环冲模式,每次每个缓冲区只接收8个字节数据,然后切换缓冲区。【实际上我将2个接收缓冲区开辟的空间为10个字节】

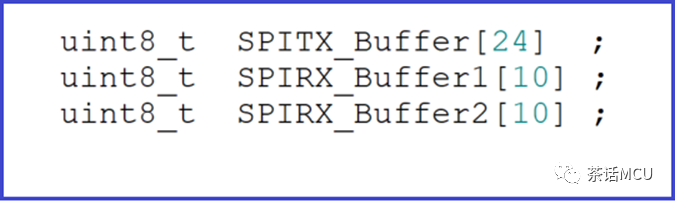

我基于STM32HAL库组织的代码,核心用户参考代码如下:

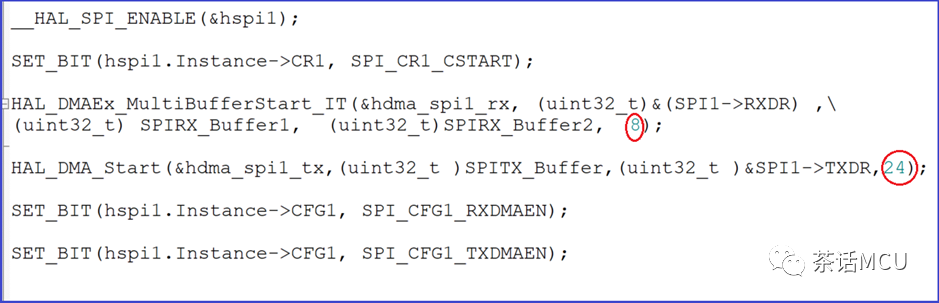

下面函数代码截图是用来更新SPI发送缓冲区内容的,测试中每2秒更新一次。

下面是经过调试后的某一刻的演示结果截图:

另外,下方还有视频演示效果,有兴趣的可以看看。建议点击全屏按钮 查看,否则效果可能不太好。整体效果就是定时产生EXTI0中断,触发SPI的DMA方式发送,SPI基于DMA双缓冲模式进行接收,可以看到2个接收缓冲区内容因周期性接收切换操作而变更。

查看,否则效果可能不太好。整体效果就是定时产生EXTI0中断,触发SPI的DMA方式发送,SPI基于DMA双缓冲模式进行接收,可以看到2个接收缓冲区内容因周期性接收切换操作而变更。

关于咨询者的功能实现的介绍及演示就到这里。最后特意给些相关提醒,这些提醒跟上面演示同等重要。

1、注意开启D-Cache时的数据一致性问题;

2、注意通用DMA访问域的限制问题

3、注意DMAFIFO开启与不开启时的差别;

4、注意初始化代码往往是有顺序要求的;

说实在的,本咨询话题涉及的内容及知识点可能有点多,在此不能一一详述。本人分享此应用演示的主要目的,是希望给关注本应用话题的人一些实现参考。能实现,可以实现,给遇到相应困难的同仁以信心。

今天的话题就聊到这里,就此打住。下次再聊~!

-

jf_15470363

2025-03-06

0 回复 举报博主你好,我也是使用外部中断,但spi可以在这个中断中得到正确数据,单独开启DMA读取操作,只能读前四个32位数据,其余的为0,开启双缓冲模式,就根本读不到数据了 收起回复

jf_15470363

2025-03-06

0 回复 举报博主你好,我也是使用外部中断,但spi可以在这个中断中得到正确数据,单独开启DMA读取操作,只能读前四个32位数据,其余的为0,开启双缓冲模式,就根本读不到数据了 收起回复

-

jf_15470363

2025-03-07

0 回复 举报太赞了 收起回复

jf_15470363

2025-03-07

0 回复 举报太赞了 收起回复

-

如何用STM32H7的EXTI0同步触发SPI DMA双缓冲?2024-03-14 381

-

STM32H7技术详解2023-08-01 814

-

AN5361_开始使用基于STM32CubeIDE双核STM32H7微控制器的项目2022-11-21 794

-

双核型号的微控制器STM32H72022-05-15 13249

-

【STM32H7教程】第14章 STM32H7的电源,复位和时钟系统2021-12-09 1317

-

"STM32H7学习继续(STM32H7系列5)第十七章比较实用,以后写程序的时候会用到"2021-12-05 944

-

【STM32H7教程】第21章 STM32H7的NVIC中断分组和配置(重要)2021-12-04 1347

-

STM32H7学习之路继续(stm32H7系列3) GPIO2021-11-30 1225

-

【STM32H7教程】第19章 STM32H7的GPIO应用之按键FIFO2021-11-23 1249

-

双核STM32H7正式投入生产 样品现已上市2020-03-01 4878

-

基于STM32介绍DMA的双缓冲模式2019-02-02 26305

-

STM32H7演示:意法半导体2018-07-02 7425

全部0条评论

快来发表一下你的评论吧 !