Foreach对Associative Array的constraint约束问题记录分享

电子说

描述

systemverilog constraint中的foreach可以对数组进行遍历和约束,常用于普通数组,队列或者动态数组。而当对associative array(联合数组/字典)应用foreach时,遇到一些问题,记录分享如下。

联合数组含有key和value两个元素,在这里key的类型以int和string为例,value元素以int和int[$]队列为例。

[int/string] [int] Associative Array

实践的demo代码如下:

class test;

rand bit[3:0] rd_dict[int];

rand bit[3:0] rd_dict_fix[int];

rand bit[3:0] rd_dict_str[string];

constraint c_rand{

rd_dict.size == 7;

foreach(rd_dict[i]) {

rd_dict[i] < 13;

}

foreach(rd_dict_fix[i])

rd_dict_fix[i]== 13;

foreach(rd_dict_str[i])

rd_dict_str[i]== 14;

}

function new();

rd_dict_fix[9] = 0;

rd_dict_str["A"] = 0;

endfunction

rd_dict没有进行初始化,使用constraint的size进行约束联合数组key的个数和value取值约束

rd_dict_fix在new函数中进行初始化,包含一个int key元素,在constraint中对value进行约束

rd_dict_str在new函数进行初始化,包含一个string key元素,在constraint中对value进行约束

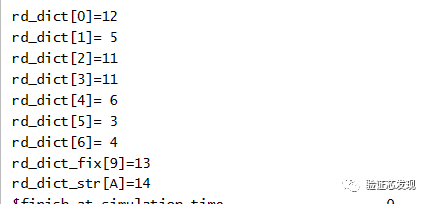

添加适当的测试打印代买,可以得到如下的仿真结果:

可以看出,普通的联合数组,如果没有初始化key元素,可以在constraint中使用size约束key的个数,但key是顺序递增的,0~size-1。

如果初始化了key元素,无论是int还是string类型的key,使用foreach时,可以对已初始化的key对应的value进行约束。

int/string->int[$] Associative Array

联合数组的value是int队列时,demo代码如下:

class test;

rand bit[3:0] rd_dict[int][$];

rand bit[3:0] rd_dict_fix[int][$];

rand bit[3:0] rd_dict_str[string][$];

constraint c_rand{

rd_dict.size == 7;

foreach(rd_dict[i]) {

rd_dict[i].size == 3;

foreach(rd_dict[i][j]) {

rd_dict[i][j] < 13;

}

}

foreach(rd_dict_fix[i]) {

rd_dict_fix[i].size == 4;

foreach(rd_dict_fix[i][j]) rd_dict_fix[i][j]== 13;

}

foreach(rd_dict_str[i]) {

rd_dict_str[i].size == 4;

foreach(rd_dict_str[i][j]) rd_dict_str[i][j]== 14;

}

}

function new();

rd_dict_fix[9] = '{};

rd_dict_str["A"] = '{};

endfunction

rd_dict的key是int类型,value是int[$]队列类型的value,size和value值都进行了约束。

rd_dict_fix类型和rd_dict相同,区别在于new函数中进行key初始化,仅包含一个key。

rd_dict_str的key类型是string类型,其他和rd_dict_fix相同。

不出意外,上述的code编译出错:

... Expression of this type cannot be used to index the array ...

错误在于key是string类型,value是int[$]队列的字典,constraint中不能使用foreach操作。

将上述string->int[$]的constraint注释后,编译可以通过,在仿真时会出错:

The constraint solver failed when accessing a null array rd_dict[0]. Please make sure array rd_dict[0] is allocated properly.

由于rd_dict[int][$]并没有在new函数中进行初始化,即使在constraint中使用了size约束大小,也没有达到预期的效果,这点和[int/string] [int] Associative Array例子中不同。

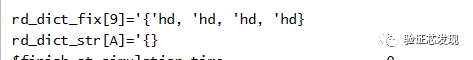

上述问题解决后,可得到最后的仿真结果:

从上述的结果来看,如果联合数组的value是队列时,则需要先进行key的初始化,才可在constraint中进行对value队列的约束。key是string类型时,似乎没办法使用foreach进行约束。

审核编辑:刘清

-

如何编写高级时序约束?2019-03-27 1076

-

设计中的关键路径如何约束2019-04-08 1509

-

OFFSET约束问题2019-05-29 2155

-

一个约束驱动(constraint-driven)的综合工具2021-07-29 941

-

编程遇到的问题记录2021-11-30 954

-

STC89C52RC单片机奇葩问题记录2021-12-08 1274

-

使用STM32的MCU开发问题记录2022-01-05 1689

-

华大MCU的应用中的问题记录2022-02-24 2920

-

HarmonyOS/OpenHarmony应用开发-ArkTS语言渲染控制ForEach循环渲染2023-08-18 2461

-

时序约束爆炸的原因研究分析2018-11-20 2464

-

Java的iterator和foreach遍历集合源代码2021-03-17 759

-

PHP教程:foreach使用引用注意的问题2021-09-22 627

-

AD学习问题记录(二):pcb设计规则检查报错Silk To Solder Mask Clearance Constraint2021-12-04 7864

-

for循环和forEach的差异2022-10-11 1925

-

SV约束随机化总结2023-12-14 1805

全部0条评论

快来发表一下你的评论吧 !