浅谈FPGA输入时钟要求 LVDS与LVPECL讲解

描述

几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟芯片输出后还要经过直流或交流耦合才能接入FPGA,有点晕了,今天仔细研究一下。

FPGA输入时钟要求

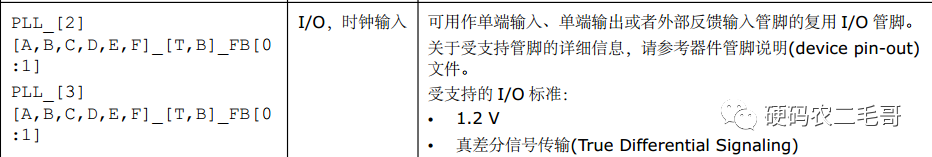

FPGA手册中对时钟输入的描述:

差分I/O电平标准:

真差分信号电压不能超过VICM(max) + VID(max)/2 。

直流耦合与交流耦合

时钟的发送端和接收端都有各自的电平接口类型,它们有可能不相同也可能是相同的。 这个时候通常就会有两种连接方式,即AC耦合以及DC耦合。 其实说简单也很简单, AC耦合就是中间用电容把发送接收端的共模电平隔开,而DC耦合就是不加电容 。交流耦合(AC Coupling)就是通过隔直电容耦合,去掉了直流分量。直流耦合(DC Coupling)就是直通,交流直流一起过,并不是去掉了交流分量。

LVDS与LVPECL

时钟芯片输出时钟信号通常有LVDS和LVPECL。

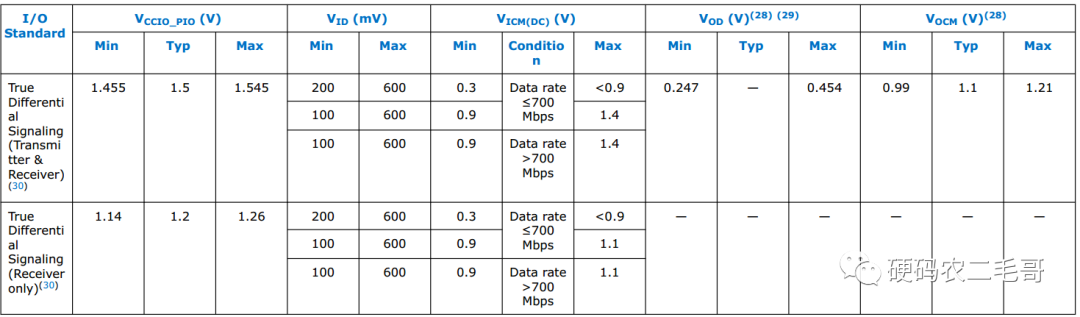

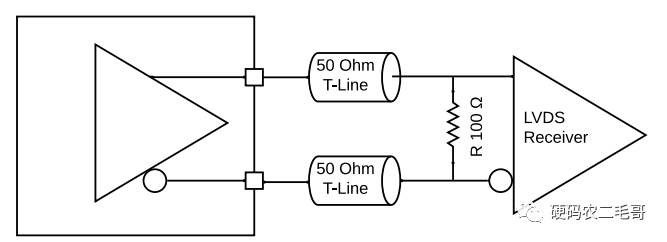

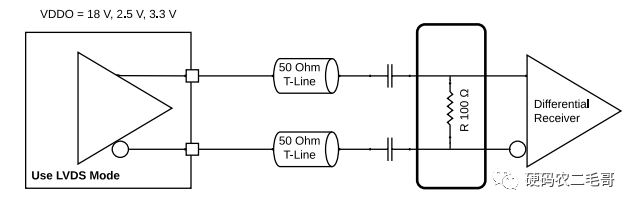

当时时钟芯片输出LVDS信号时

DC耦合

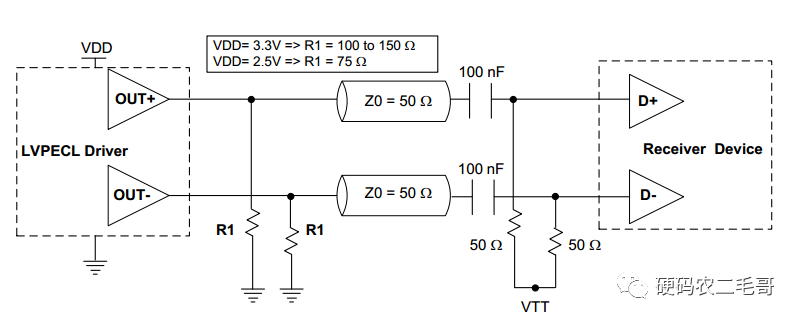

两种AC耦合方式。

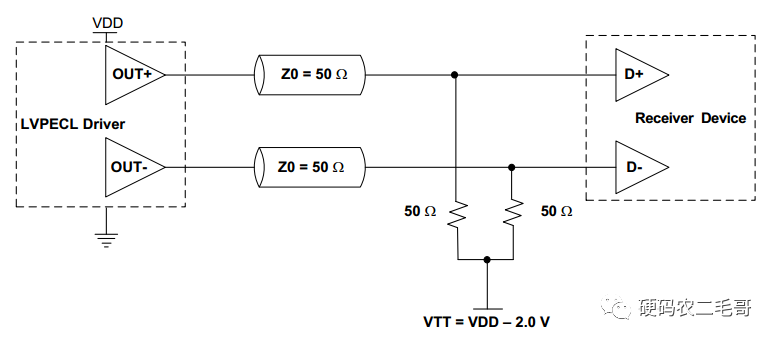

当时钟信号输出LVPECL信号时

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AD9910的SYNC_IN+、SYNC_IN-这2个LVDS输入时钟是否可以和FPGA的HP bank(1.8V供电)输出的LVDS时钟相连吗?2026-05-07 39

-

浅谈FPGA的时钟输入要求2026-03-25 1049

-

低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析2026-02-09 279

-

HACD1216QN型低抖动LVDS时钟缓冲器2025-02-13 486

-

ADS5404可以使用LVDS或LVPECL的时钟源头吗?2024-12-13 383

-

LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?2024-11-11 544

-

CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表2024-08-21 438

-

CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表2024-08-20 440

-

可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?2023-12-22 718

-

如何使用BLVDS或其他驱动Kintex LVPECL输入的方法的信息?2020-07-19 1320

-

ADCLK946是否可以直接给AD9739作为时钟驱动LVDS2019-01-03 2772

-

请问FPGA管脚是否具有电平判决功能将输入的模拟时钟信号判决为数字时钟信号?2018-12-20 2664

-

请问高速AD差分时钟驱动能使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚吗?2018-11-02 3622

全部0条评论

快来发表一下你的评论吧 !