合宙RP2040开发板轻松DIY

描述

逻辑分析仪(Logic Analyzer)是一种分析数字信号逻辑时序的仪器,能够精确捕获和显示多路数字信号,提供信号时序、协议分析等功能。也是嵌入式工程师日常开发中,极为常用的工具之一。

现在,我们使用基于树莓派主控芯片的合宙RP2040开发板,就可以低成本快速DIY逻辑分析仪。

9.9元自制100M逻辑分析仪

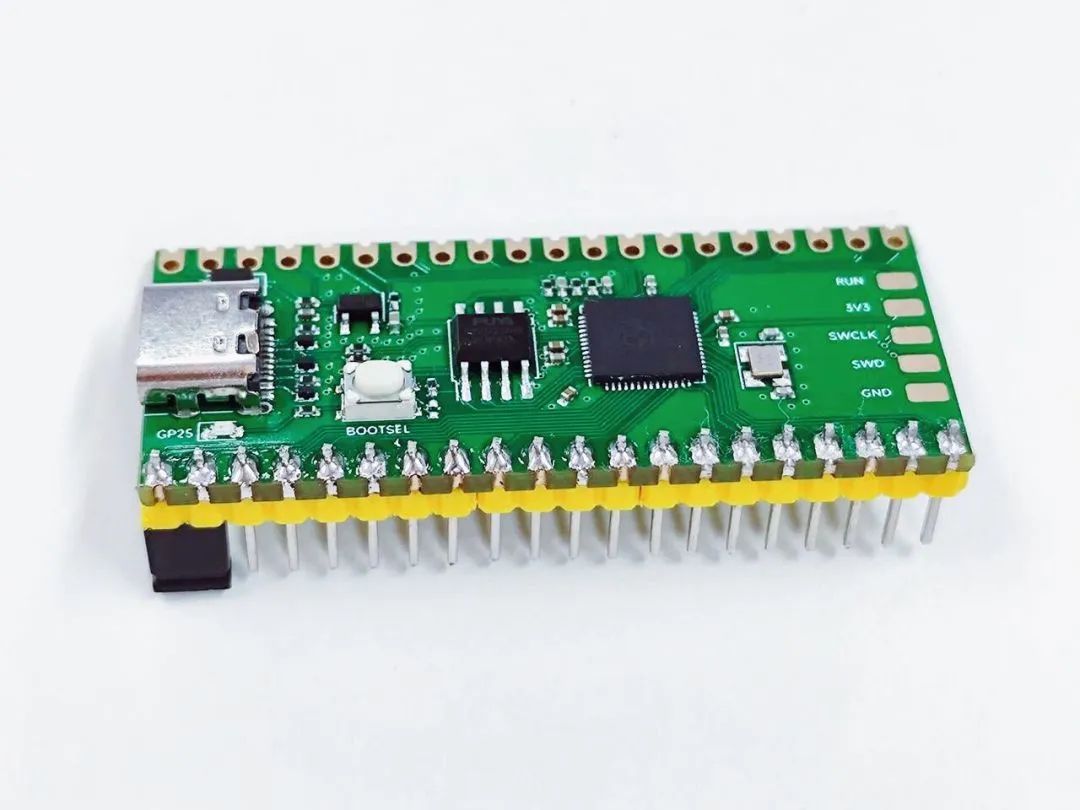

CORE-RP2040——合宙推出的9.9家族又一款新品,采用树莓派RP2040芯片作为核心,引脚定义兼容官方PICO开发板,并在官方基础上升级到4MB Flash和Type-C接口。

结合开源固件,可实现100M的逻辑分析仪功能:

逻辑分析仪开源仓库:

https://github.com/gusmanb/logicanalyzer

功能支持

基于合宙RP2040开发板的逻辑分析仪,可支持如下功能:

支持3.1K至100Mhz的采样频率;

支持24通道输入,通过菊花链最高可支持120通道;

最高支持32767个采样点;

支持多种客户端,全平台可用。

硬件准备

我们需要一块合宙RP2040开发板,并且需要将GP0与GP1两个引脚进行短接处理。

刷入固件

按住BOOT按键,再插入USB,进入升级模式。

下载固件文件,复制进入U盘,即可刷入成功:

https://github.com/gusmanb/logicanalyzer/releases/download/V5.0.0.0/Firmware-LogicAnalyzer-5.0.0.0-PICO.uf2

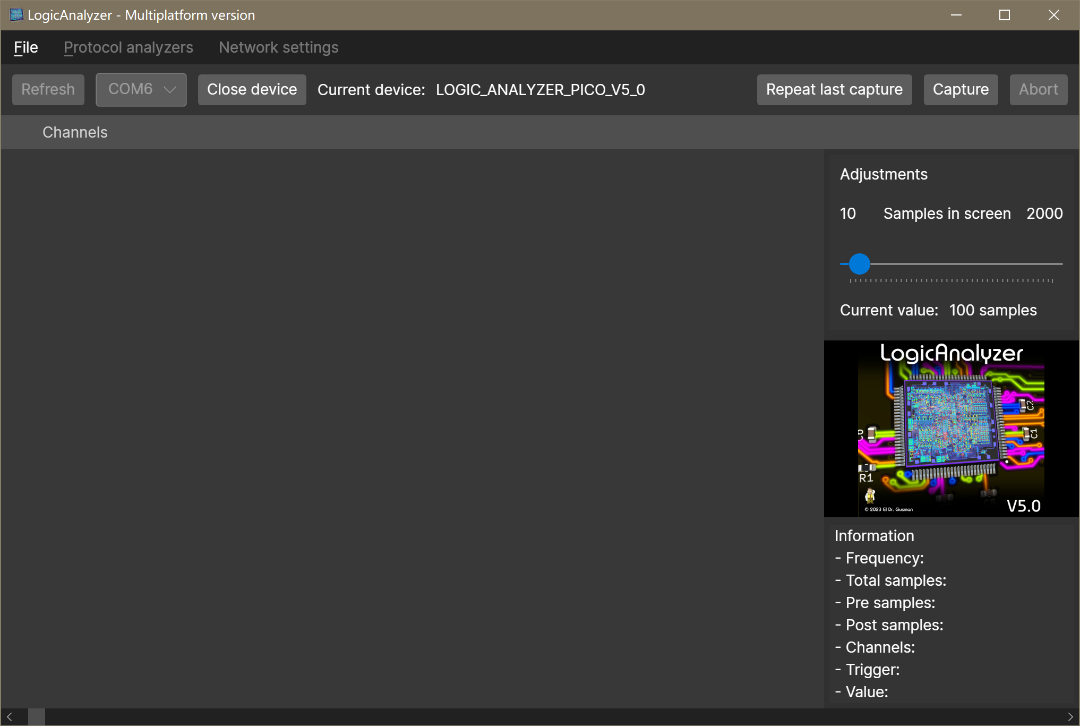

连接软件

这里默认使用开源仓库作者自行编写的客户端软件:

https://github.com/gusmanb/logicanalyzer/releases/latest

下载自己需要的系统版本,本文选用:

LogicAnalyzer-5.0.0.0-win-x64.zip

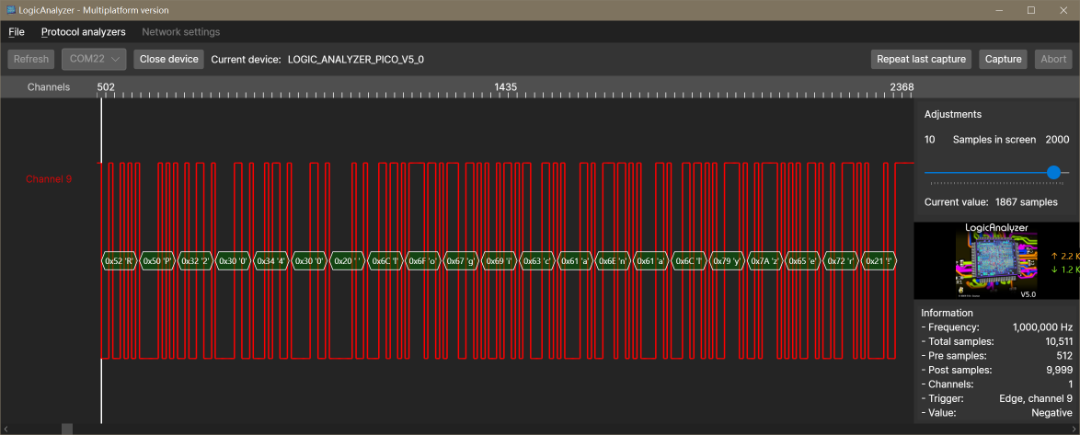

选择树莓派虚拟出来对应的串口,连接上:

抓取数据

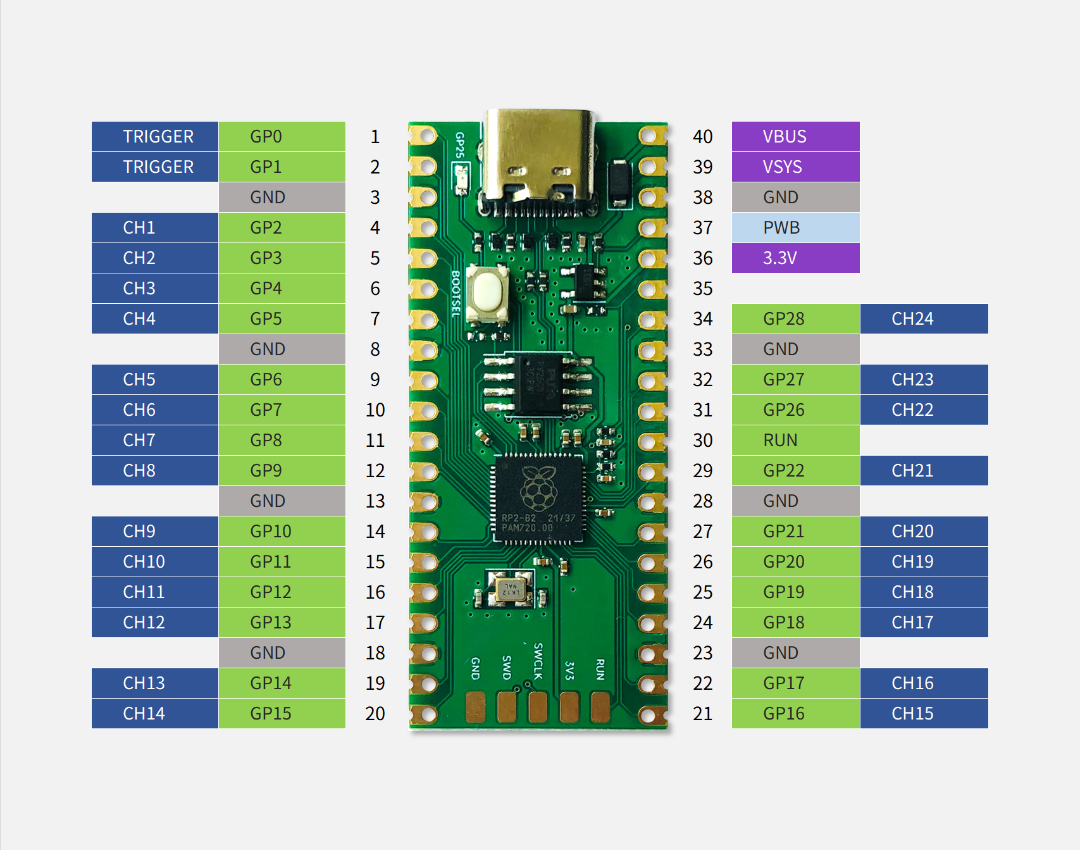

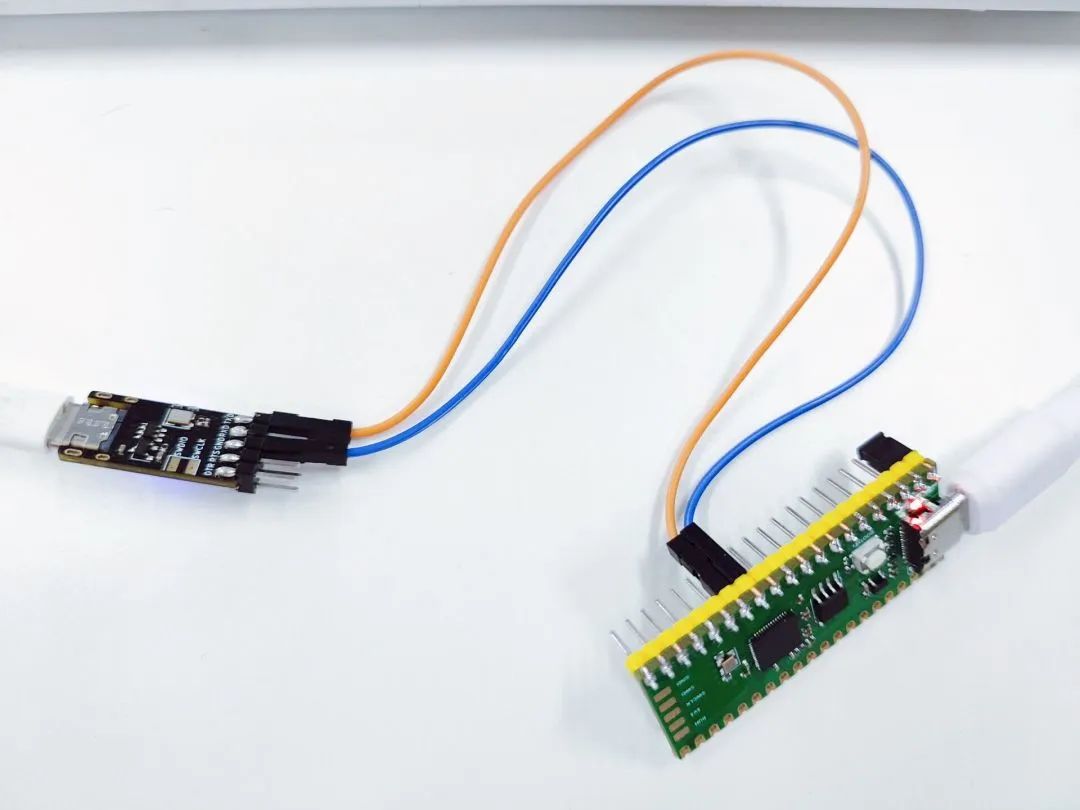

将合宙RP2040开发板的GND与我们需要测量的板子的GND相连,再将需要测量的引脚连接到开发板的GPIO上。

通道编号与GPIO编号的对应关系如下:

我们连接上被测引脚后,就能开始抓取了:

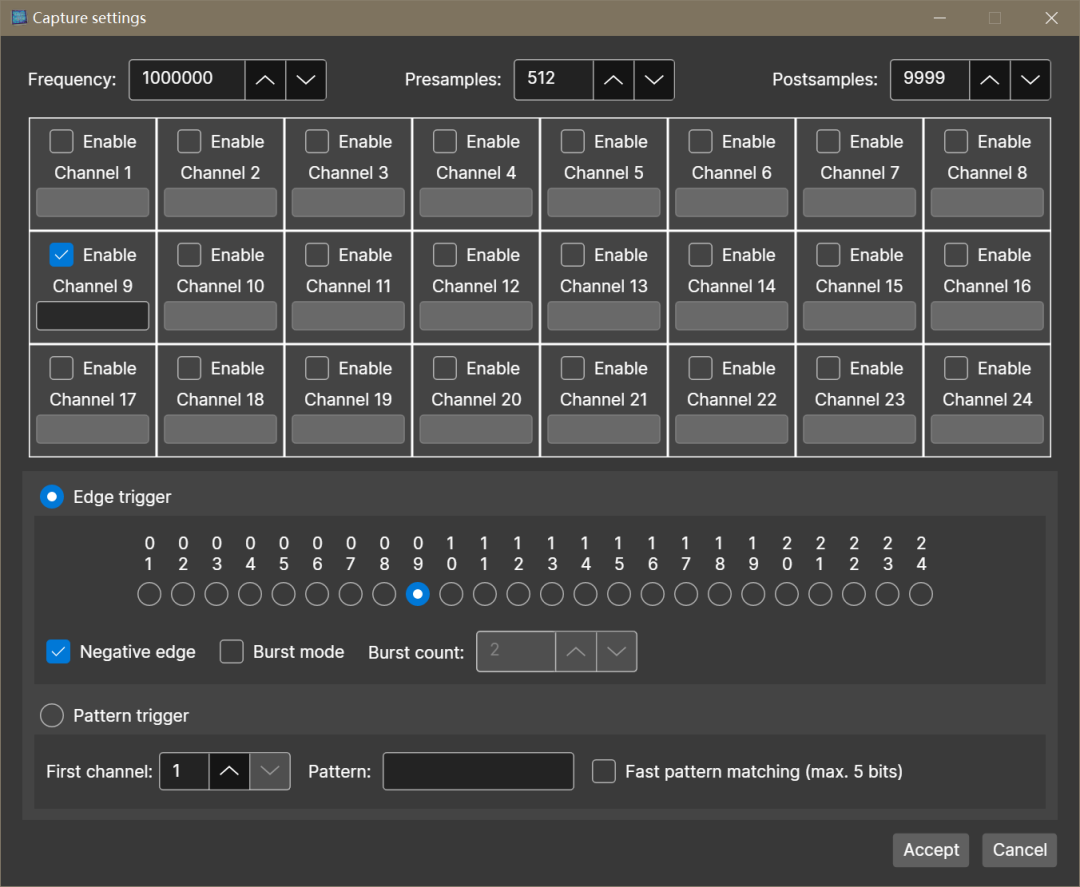

点击Capture,选上对应的通道、抓取频率与采样数、触发条件,点击Accept即可开始抓取:

-

使用RP2040设计一个迷你板2022-09-02 3349

-

pico-ice:RP2040 plus Lattice iCE40UP5K FPGA 开发板 介绍2024-06-28 6464

-

ubuntu上交叉编译rp20402024-08-27 1650

-

树莓派Pico迷你开发板及所使用的RP2040 MCU芯片有哪些特性2021-09-14 2188

-

RP20402023-09-15 22111

-

e络盟现货发售Arduino Nano RP2040 Connect和Raspberry Pi Pico2021-09-23 3612

-

RP2040 MCU如何成为受欢迎的开发板芯片2022-06-01 18340

-

RP2040 MicroMOD处理器板开源分享2022-07-21 1062

-

RP2040迷你板开源分享2022-08-15 3072

-

RP2040模块MCU开源分享2022-10-28 1028

-

搭载RP2040双核处理器芯片,BPI-Pico-RP2040 开发板开发实例展示2023-06-27 13074

-

9.9元包邮!合宙RP2040开发板,兼容树莓派PICO2023-08-07 6215

-

9.9元自制树莓派逻辑分析仪?!合宙RP2040开发板轻松DIY2023-08-14 19452

-

合宙RP2040开发板,兼容树莓派PICO2023-08-08 4957

-

矽递科技XIAO RP2040开发板的Arduino开发环境配置教程2025-03-17 3945

全部0条评论

快来发表一下你的评论吧 !