伺服环路ADC测试的基础知识介绍

描述

伺服环路测试可以确定模数转换器 (ADC) 传递函数。本文将介绍伺服环路 ADC 测试的基础知识,并说明几种不同的伺服环路测试配置。

A/D 转换器 (ADC) 的静态参数有助于了解直流或缓慢变化信号的器件行为。然而,为了确定静态参数(包括失调和增益误差、微分非线性(DNL) 和积分非线性(INL)),我们首先需要确定 ADC 的直流传递函数。伺服环路测试是确定 ADC 传递函数的经典工业方法。

ADC 与 DAC 测试

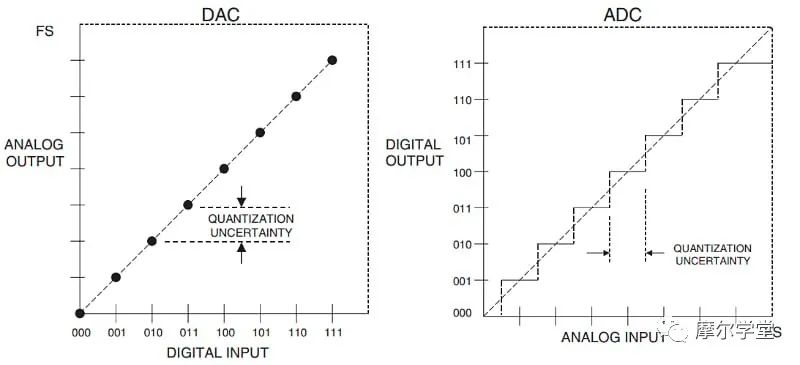

测试 ADC 可能比测试 D/A 转换器 (DAC) 困难得多。这是因为 DAC 传输曲线是一对一映射函数,而 ADC 特性曲线是多对一映射函数。图 1 对此进行了说明。

图 1. DAC 和 ADC 传输曲线。图片由Analog Devices提供。

图1显示了3位单极性DAC和3位单极性ADC的理想特性曲线。对于DAC来说,输入和输出都是量化的,传递函数由八个点组成。作为一对一的映射函数,我们可以轻松测量每个数字代码的 DAC 输出电压并确定其传输曲线。另一方面,给定的 ADC 输出代码对应于连续范围的输入值。因此,我们无法通过向 ADC 输入施加已知电压并测量输出代码来确定 ADC 传递函数。

为了完全确定 ADC 转换曲线,我们必须测量其代码转换点。这使得 ADC 测试变得复杂且昂贵。事实上, ADC 单位售价的大约15% 到 20%是由于不同的测试程序造成的。学术界和工业界的研究人员进行了大量研究,寻找有效的 ADC 测试方法。一种流行的方法是伺服环路测试,如下所述。

伺服环路 ADC 测试

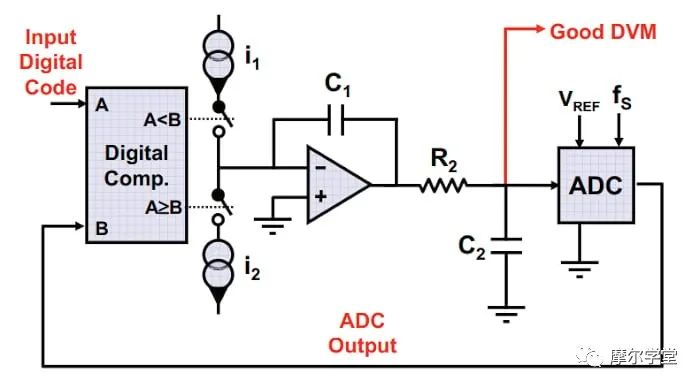

伺服环路测试于 1975 年首次推出,是一种基于反馈的技术,用于确定 ADC 转换点。测试装置的基本配置如图 2 所示。

图 2. 基本伺服环路测试配置。图片由H. Khorramabadi提供

反馈环路由数字比较器、两个电流源(I 1 和 I 2)、配置为模拟积分器的运算放大器以及被测 ADC 组成。为了确定给定的转换点,将相应的代码应用于比较器的“A”输入。该值与 ADC 输出代码进行比较(ADC 输出连接到比较器的另一个输入“B”)。如果 ADC 输出大于目标代码 (B > A),比较器将打开上部开关一段特定的时间段 Δt。当 I 1 流经 C 1时,积分器输出减少:

因此,这会减少 ADC 输出代码,使其更接近应用于比较器“A”输入的目标代码。这一过程将持续进行,直到 ADC 输入距离目标转换点在一步 (ΔV) 以内。在下一个周期,ADC 输入又减少了 ΔV,使得 ADC 输出小于或等于 A (B ≤ A)。此时,比较器打开下部开关并增加积分器输出:

通常,两个电流源具有相同的值;因此,任一方向的步长是相同的。由于 ADC 输入距离转换点仅一步之遥,后续步骤将使 ADC 输入在每个周期跨越转换点。换句话说,ADC 将交替输出大于 A (B < A) 或小于或等于 A (B ≤ A) 的代码序列。

瞬态响应和振荡行为

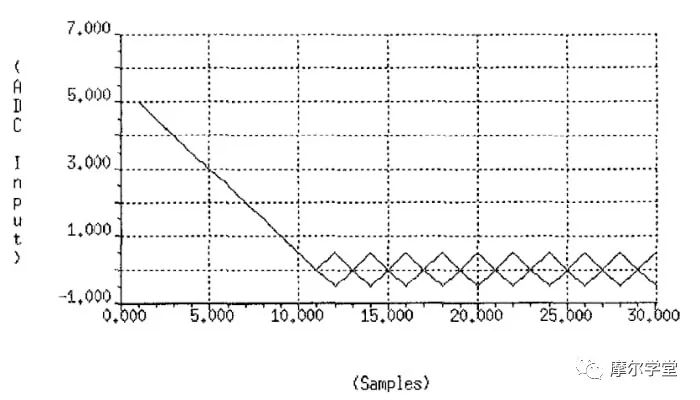

图 3 应该可以帮助您更好地可视化系统响应。该图显示了 ADC 输入电压如何接近代码转换点。该图显示了具有不同初始值的两种不同模拟的波形。在一项仿真中,ADC 输入的初始值比目标代码转换点大 10 步 (10ΔV)。在第二个中,初始值距代码边缘 10.001 步。

图 3. 伺服环路测试的瞬态响应展示了振荡行为。图片由S. Max提供 (需要订阅)

这里有一些值得一提的观察结果。首先,ADC 输入实际上并不等于转换电压。环路进入振荡状态,其中 ADC 输入电压是围绕过渡电平振荡的三角波(我们忽略 R 2 和 C 2 可能引入的滤波效应)。三角波形的平均值提供了代码转换点的估计。如图 2 所示,可以使用具有内置平均运算功能的数字电压表 (DVM) 来测量波形的平均值。

其次,图 3 显示在 ADC 输入从转换点落入一步之前存在瞬态响应。因此,平均过程应在信号稳定在最终平均值的可接受误差范围内后开始。

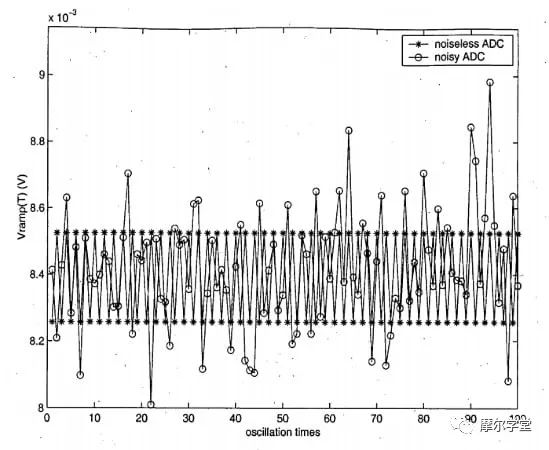

另外,应该注意的是,上述三角响应对应于无噪声系统。在现实世界的系统中,不同组件引入的噪声会导致一定程度的随机性。这会将三角波形转换为围绕代码边缘值上下锯齿状的噪声信号。图 4 比较了噪声 ADC 与无噪声系统(类似于图 3)的波形。

图 4.无噪声和噪声系统的伺服环路振荡。图片由Z.Zhao提供

通常采用信号平均 技术来减少噪声对测试结果的影响。决定反馈环动态的两个主要因素是步长 (ΔV) 和系统中存在的噪声水平。在本系列的下一篇文章中,我们将讨论这两个因素如何影响不同的参数。

ADC 反冲噪声

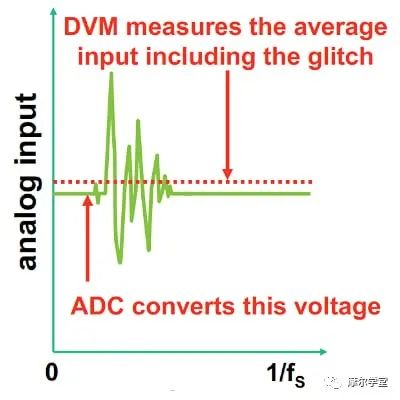

ADC 内的采样保持 (S/H) 基本上由一个开关和一个采样电容器组成。当开关在 ADC 采样阶段开始时闭合时,采样电容器与前面的驱动电路共享其存储的电荷。在图 2 所示的示例中,内部采样电容器与 C 2共享电荷。这会在采样阶段开始时在 ADC 输入处产生干扰,称为反冲噪声。图 5 说明了这种效果。

图 5.图片由H. Khorramabadi提供

反冲效应会向 ADC 模拟输入添加高频、信号相关的毛刺。通过正确设计的系统,ADC 可以采集正确的样本。然而,DVM 可能会在毛刺消失之前采集一些样本,从而导致 ADC 输入电压平均值的测量不正确(参见图 5)。

为了减少反冲噪声,我们可以增加C 2电容的值 。然而,这需要降低采样率(或等效地增加 ADC 采样阶段的持续时间)。因此,通过选择C 2 为大电容,我们可以以更长的测量时间为代价来减少反冲效应。如果您需要温习这些概念,我建议您观看 Analog Devices 的 这个视频系列。

替代伺服环路测试配置

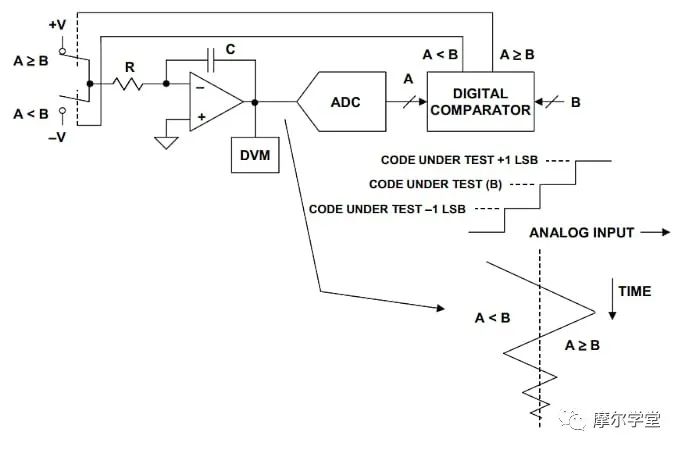

图 6 显示了略有不同的伺服环路测试配置。在这种情况下,积分器输入不是使用电流源,而是通过电阻器 (R) 连接到已知电压(图中的 +V 和 -V)。因此,输送到积分器的电流为I=V/R。

图 6.使用电压源的替代伺服环路测试配置。图片由Analog Devices提供

值得一提的是,图中提供的定性波形似乎不正确,因为在这种情况下三角波形具有衰减幅度,这与图 3 和图 4 中提供的典型波形不一致。

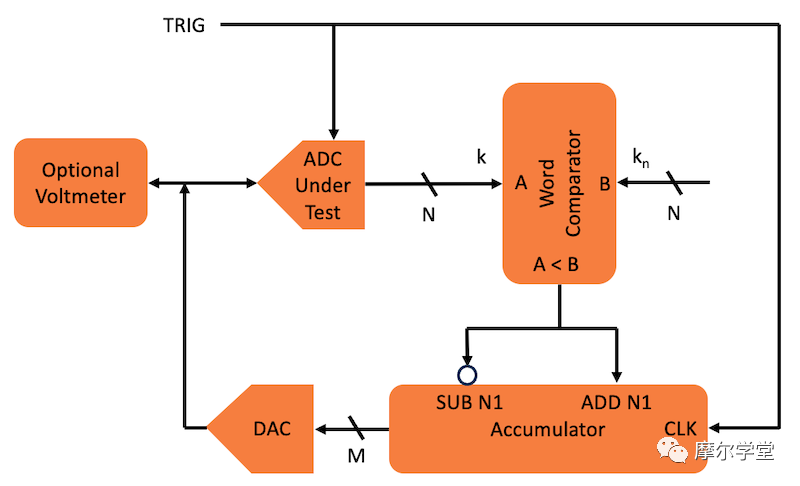

伺服环路测试的另一个版本如图 7 所示。在这种情况下,模拟积分器被替换为数字累加器,数字累加器根据比较器的输出,在其先前值中添加或减去特定值 (N1)。

图 7. 使用数字累加器的替代伺服环路测试配置。图片改编自 S. Max,并由S. Max提供 (需要订阅)

此外,DAC 用于将累加器输出转换为模拟值。生成转换点估计值的模拟值被传送到 ADC 输入,就像图 2 中的图表一样。图 3 中提供的仿真波形对应于图 7 中的配置。

在本系列的下一篇文章中,我们将继续讨论,并了解如何根据所需的测量精度和系统中存在的噪声来选择此测试设置的不同参数。希望您现在了解了伺服环路 ADC 测试的基础知识,甚至对 ADC 表征的困难有了一定程度的认识。

审核编辑:刘清

-

电感基础知识 图文介绍2012-08-16 6422

-

IGBT的介绍和应用基础知识2015-06-24 9116

-

电阻的基础知识介绍2021-02-26 3057

-

4-20mA电流环路系统基础知识,总结的太棒了2021-04-13 4137

-

介绍关于编程的基础知识2021-07-27 2012

-

介绍PLC的原理及基础知识2021-09-09 2198

-

GSM基础知识的介绍2009-07-29 1002

-

ADC【DSP基础知识】2016-01-06 554

-

ADC入门_基础知识2016-03-11 1152

-

软件测试基础知识总结2018-04-24 22566

-

模拟数字转换器(ADC)基础知识2018-06-05 1672

-

ADC转换器的基础知识详细资料说明2019-07-18 1497

-

伺服驱动的基础知识_pdf2021-12-13 979

-

PCB应变测试基础知识2022-02-18 2312

-

FPGA基础知识介绍2024-02-23 810

全部0条评论

快来发表一下你的评论吧 !