GAA器件集成工艺与关键挑战

电子说

描述

GAA,一般指全环绕栅极晶体管(Gate-All-Around FET)。GAA被广泛认为是鳍式结构(FinFET)的下一代接任者。下面简单介绍一下GAA器件集成工艺与关键挑战。

GAA器件集成工艺——主要流程与关键工艺

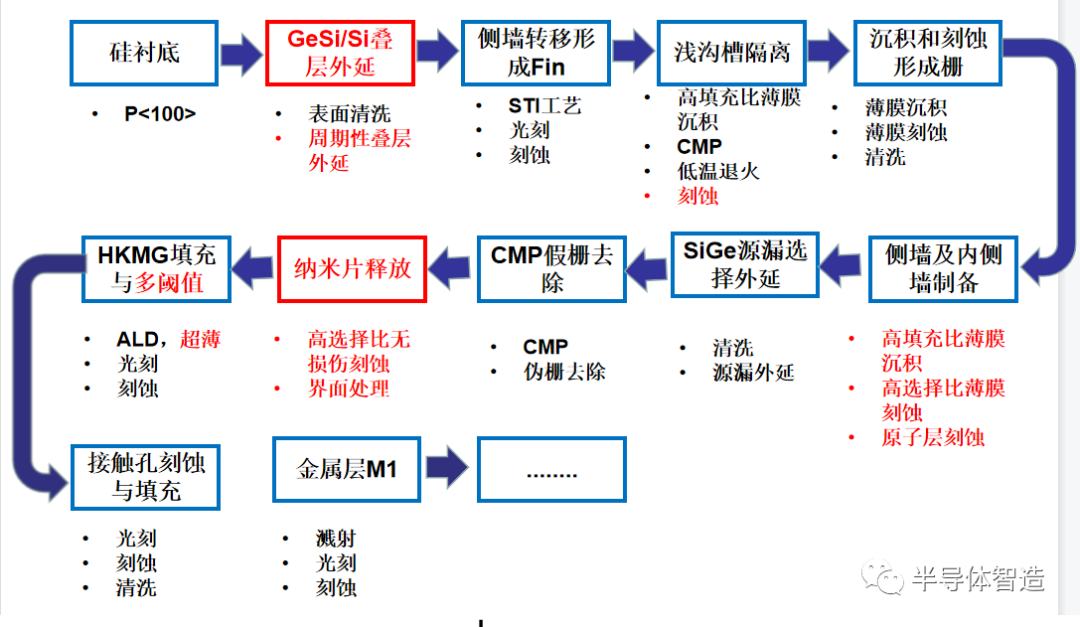

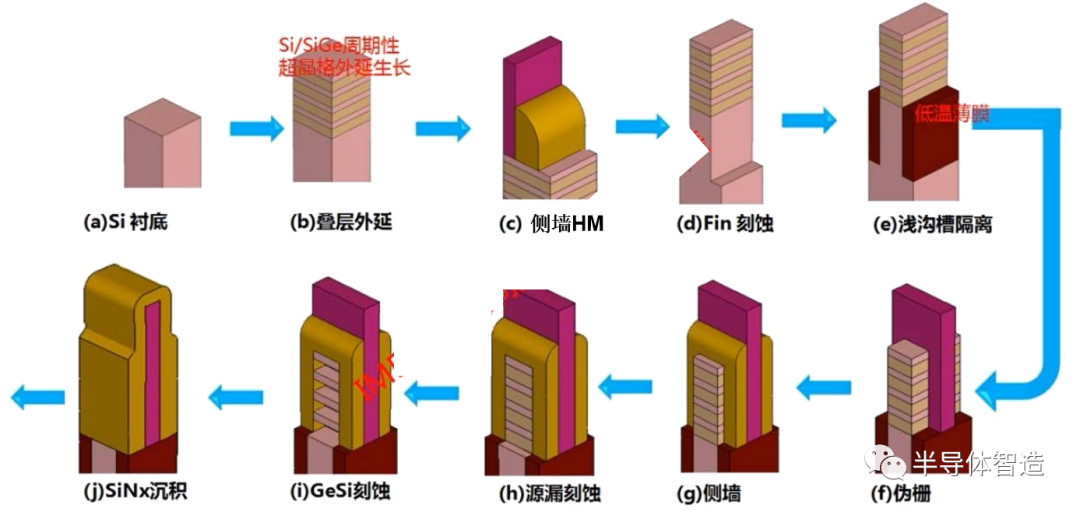

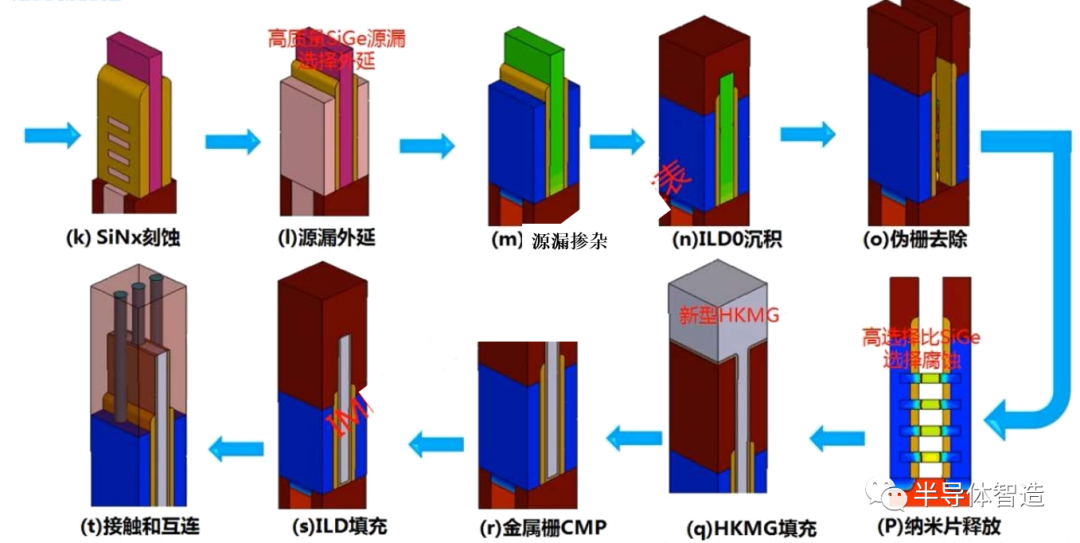

环栅硅纳米片(GAA NS)主要流程工艺

硅纳米片GAA器件——主要工艺流程

硅纳米片GAA器件——关键技术与挑战

3nm技术节点GAA器件工艺制备和集成应用所面临的挑战

N/P MOS性能差异大(Si-100)/<110>沟道)

前道Ge元素具有沾污风险,限制工艺温度

内侧墙集成挑战大,工艺不成熟

HKMG多阈值实现困难(空间有限)

高选择比纳米沟道释放工艺(干法、湿法、对形貌、表面等要求)

难以满足电路所有器件需求,如I/O、HV等)

底层纳米片沟道非理想因素(寄生电阻、阈值漂移)

寄生电容与寄生电阻优化挑战大

硅纳米片GAA器件——纳米线释放工艺优化

GAA堆叠纳米片沟道释放工艺优化

采用GeSi高选择腐蚀溶液,腐蚀速率不断增加,48h后,速率饱和

GeSi RTA退火在750度时腐蚀速率最慢,温度高于或低于750度,腐蚀速率都会加快

GeSi层腐蚀的速率与其厚度呈正相关

硅纳米片GAA器件——热预算控制优化

GAA堆叠纳米片器件热预算控制优化

Ge/Si在900度以下,几乎没有相互扩散

Ge/Si在900度时,出现相互扩散

Ge/Si在1000度时,严重相互扩散

光刻工艺——挑战及技术难点

3nm技术节点GAA器件→更小的沟道及金属线尺寸,并且NS具有宽度变化性

M0、栅和Fin制备等关键层需要使用高级极紫外光刻(EUV)技术

3nm技术节点gate pitch为42nm,器件最小周期为21nm

必需使用EUV光刻技术,并结合HNA、DP技术

EUV计算光刻技术是关键环节之一

源漏选择性外延——挑战及技术难点

SiGe外延工艺选择性挑战:多介质表面(SiN,SiO,Dummy Gate)和不同晶面生长

图形密度效应影响:SiGe的厚度和浓度分布不均匀

SiGe源漏原位掺杂:更高的Ge组分(大于40%),更高的掺杂浓度,更低的电阻率

GAA中沟道横向外延与纵向外延的质量控制

内侧墙工艺——挑战及技术难点

内侧墙控制NS沟道在释放工艺中向源漏方向的横向腐蚀

该工艺包含高选择比各向异性刻蚀、高填充比薄膜沉积和高质量选择外延等多个具有挑战性的工艺环节

高选择比SiGe空腔刻蚀(对Si、硬掩模、STI等露出物高选择比)

侧面空腔保形性填充( -般ALD SiNx材料) ;

高选择比内侧墙刻蚀(露出Si沟道,对Si、SiO2、 SiGe同时高选择比)

源漏的选择性外延( SiGe源漏外延并和沟道良好连接)

原子层刻蚀工艺——挑战及技术难点

原子层刻蚀(ALE) 为ALD的逆过程,其挑战和难点:

新型三维器件结构沟道及很多精细化图形制备需要原子层刻蚀技术;

反应源的寻找及自限制条件是其技术难点

新型金属栅材料、新型衬底材料(Ge , SiGe, III-V族)等需要新刻蚀方案;

刻蚀过程中要求原子级精细化的无损刻蚀

高k介质金属栅——挑战及技术难点

GAA器件中HKMG的集成挑战

挑战1 :堆叠NW/NS沟道中HK/MG填充空间狭窄,受限于Lg和Tsus

挑战2 :传统通过TiN/TaN及功函数层的薄膜厚度来实现多阈值面临极大挑战

挑战3 :不同宽度(不同功能)的纳米片GAA器件对HKMG的功函数需求不同

解决方案:设计简单的HKMG结构,ALD生长超薄膜实现保型覆盖,偶极子实现多阈值调节等

低阻接触工艺——挑战及技术难点

源漏接触电阻成为制约器件性能提升的重要因素降低源漏接触电阻率

低阻接触工艺的关键挑战:

接触面积的缩减

反应源的寻找及自限制条件影响金属与n-SiGe和p-SiGe形成极低接触电阻率

源漏杂质固浓度限制

高质量的金-半接触界面

自对准接触工艺——挑战及技术难点

自对准接触孔工艺(Self Aligned Contact, SAC), 减小接触尺寸,提升集成

该技术的关键是解决接触孔层与栅极层光刻对准偏差,依靠设计合适的膜层,和开发特殊的接触孔刻蚀工艺来获得自对准效果

孔刻蚀对栅极顶部侧墙材料的高选择比(尤其是角位置)是一个较大的技术

自对准接触工艺——研究进展

SAC技术早期用在DRAM上,采用C4F8/CO, C4F8/CH2F2气体刻蚀ILD层; 7nm以下F inFET和GAAI艺也必须用到SAC工艺

可靠性技术——必要性

可靠性技术研发是新器件技术走向产业化规模应用的一个重大瓶颈问题

可靠性技术研发涉及多个环节,在尺寸缩小、走向系统集成的未来面临更多挑战

缩短研发周期,提前介入新器件技术可靠性研究十分必要

国际上针对先进器件的可靠性研发细节都是“黑盒子”

可靠性技术——挑战及技术难点

新器件在开展可靠性研究上面临诸多技术挑战:

新结构导致可靠性问题更加严重和错综复杂; →表征技术/寿命预测难题➢新材料导致可靠性退化机理分析存在更多未知因素; →机理分析难题

器件的小尺寸对可靠性测试精度和准确度提出更高要求: →测试技术难题

可靠性技术——设备需求

先进器件的可靠性量测对测试设备精度提出更高的需求:

更低的电流值/电容值:小尺寸器件量测;

更强的屏蔽效果:降低外界干扰/噪声量测;

纳秒级的快速测量系统:准确评估器件可靠性,降低恢复特性;

-

FinFET与GAA结构的差异及其影响2025-05-21 4401

-

集成电路新突破:HKMG工艺引领性能革命2025-01-22 5141

-

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用2024-12-20 8127

-

使用半大马士革工艺流程研究后段器件集成的工艺2023-10-24 2290

-

GAA器件结构工艺和挑战2023-06-13 2259

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2947

-

美国从EDA下绊子,3nm工艺关键技术GAA将与中国无缘?2022-08-17 3737

-

剖析晶体管结构新变革以及GAA机遇与挑战2021-09-23 3614

-

新思科技与三星合作,加速推广变革性3纳米GAA技术2021-07-07 820

-

5nn重夺领导地位 GAA工艺性能提升将会更明显2020-03-11 3154

-

LTE基站发射机的RF IC集成设计方案2019-07-05 2203

-

MEMS与IC集成工艺介绍 NEMS器件在IC 中的应用2018-05-03 10986

-

RTD与PHEMT集成的关键工艺2011-06-24 994

全部0条评论

快来发表一下你的评论吧 !