DDS-IP核的理论知识和应用案例

描述

DDS,Director Digital Synthesis,直接频率合成技术,是指通过固定频率的参考时钟(采样时钟)生成指定频率的正余弦信号。采用FPGA配合DAC芯片,可以实现频率、相位可调的模拟信号用于一些特定的领域。

01、DDS-IP核理论部分

1.1、4个重要概念

PINC, Phase Increase,频率控制字,用于生成期望频率的波形数据;

POFF, Phase Offset,相位控制字,用于生成期望初始相位的波形数据;

Spurious Free Dynamic Range (dB),无杂散动态范围,用于调整正弦和余弦输出数据的位宽,假设需要的正弦和余弦输出数据的位宽是16bit,动态范围的数值设置为16*6 = 96 ;

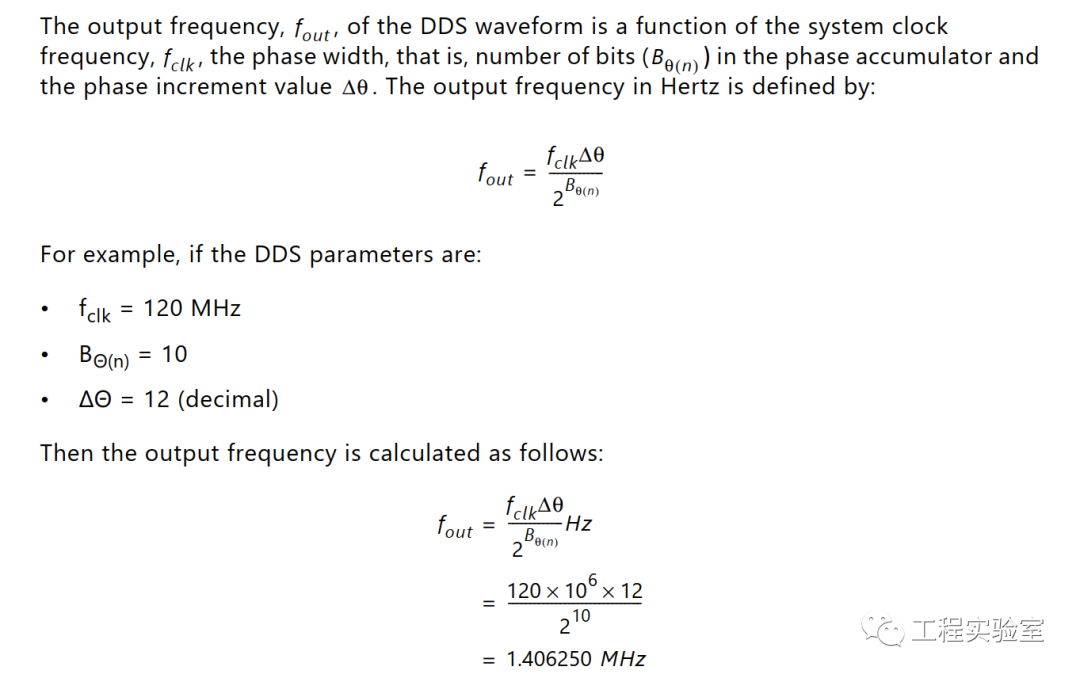

Frequency Resolution(Hz),频率分辨率,IP核输出正余弦信号能够达到的最小频率。参考时钟/采样时钟(f_clk)、频率控制字(delta_theta)、输出频率(f_out),三个变量之间的计算关系如下:

上述公式中2^n(公式中的分母),n取决于频率分辨率,分辨率越小,n的数值越大,频率控制字(delta_theta)的位宽越大。

相位控制字与位宽n之间的关系如下:

POFF = phase * (2^n-1)/360,比如期望输出的正弦波初始相位是90度,那么POFF = 90* (2^n-1)/360 = (2^n-1)/4。

1.1.1、输出信号的频率f_out和频率控制字delta_theta之间的关系

前面的公式:

假设系统的参考时钟是f_clk=250MHz, 通过公式易知,频率控制字delta_theta的取值范围还是0 ~ 2^n,对应输出信号的频率,其取值范围是0~f_clk。根据采样定理,所产生的信号频率不能超过时钟频率(采样时钟频率,250Mhz)的一半,在实际应用中,为了保证信号的输出质量,输出频率不要高于时钟频率的33%,以免混叠或谐波落入有用输出频带内。

假设系统的参考时钟是f_clk=250MHz, 通过公式易知,频率控制字delta_theta的取值范围还是0 ~ 2^n,对应输出信号的频率,其取值范围是0~f_clk。根据采样定理,所产生的信号频率不能超过时钟频率(采样时钟频率,250Mhz)的一半,在实际应用中,为了保证信号的输出质量,输出频率不要高于时钟频率的33%,以免混叠或谐波落入有用输出频带内。

1.2、DDS-IP 核配置

step1:在Ip-catalog中搜索dds,找到 DDS Compiler。

step2:设置PINC/POFF的数据形式,Fixed-Programmable-Streaming。

三种模式的区别如下:

Fixed是固定相位增量,IP核运行过程中不可更改,即输出的信号频率固定不变;

Programmable可编程,可在DDS运行过程中随时写入频率控制字改变输出波形的频率,用于偶尔改变频率;

Streaming应用于频繁改变频率。

输出信号如果勾选为正弦和余弦信号,输出信号的结果如下:高位bit31:16为正弦信号,低位bit15:0为余弦信号。

step3:IP核复位信号

step4:IP核配置summary

02、DDS-IP核应用部分

2.1 、使用DDS-IP 核合成高频信号

工程需求 :参考时钟是250MHz,使用8路DDS合成具备2G采样率的信号,输出到DAC芯片。

解决方案 :参考时钟是250MHz,周期为4ns,2G采样率的信号,采样周期为0.5ns,使用DDS-IP核输出250MHz的信号,相邻2个采样点之间的时间间隔是4ns,要满足2G采样率,原始4ns的周期内需要有8个采样点,DDS-IP核的信号输出通过移相实现,每个DDS-IP核移相的大小为频率控制字的1/8。

2.2、代码实现

逻辑代码顶层,模拟DAC芯片内部2G采样时钟信号,对8路DDS-IP核的输出信号连续采样,合成高频信号。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2021/06/09 19:15:35

// Design Name:

// Module Name: dds_ctrl

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module dds_ctrl(

input wire sclk,

input wire sclk_2gHz,

input wire rst_n,

input wire s_axis_phase_tvalid, // 初始相位控制字

input wire [23:0] s_axis_phase_tdata,

input wire s_axis_config_tvalid,

input wire [23:0] s_axis_config_tdata, // 频率控制字

output wire m_axis_data_tvalid0,

output wire [15:0] m_axis_data_tdata0,

output wire m_axis_data_tvalid1,

output wire [15:0] m_axis_data_tdata1,

output wire m_axis_data_tvalid2,

output wire [15:0] m_axis_data_tdata2,

output wire m_axis_data_tvalid3,

output wire [15:0] m_axis_data_tdata3,

output wire m_axis_data_tvalid4,

output wire [15:0] m_axis_data_tdata4,

output wire m_axis_data_tvalid5,

output wire [15:0] m_axis_data_tdata5,

output wire m_axis_data_tvalid6,

output wire [15:0] m_axis_data_tdata6,

output wire m_axis_data_tvalid7,

output wire [15:0] m_axis_data_tdata7,

output wire analog_data_valid,

output wire [127:0] analog_data_128bit,

output reg [2:0] cnt,

output reg [15:0] sample_data

);

wire [23: 0] config_pinc_0;

wire [23: 0] config_poff_0;

wire [23: 0] config_pinc_1;

wire [23: 0] config_poff_1;

wire [23: 0] config_pinc_2;

wire [23: 0] config_poff_2;

wire [23: 0] config_pinc_3;

wire [23: 0] config_poff_3;

wire [23: 0] config_pinc_4;

wire [23: 0] config_poff_4;

wire [23: 0] config_pinc_5;

wire [23: 0] config_poff_5;

wire [23: 0] config_pinc_6;

wire [23: 0] config_poff_6;

wire [23: 0] config_pinc_7;

wire [23: 0] config_poff_7;

assign analog_data_valid = m_axis_data_tvalid0 |m_axis_data_tvalid1 | m_axis_data_tvalid2 |m_axis_data_tvalid3 | m_axis_data_tvalid4 |m_axis_data_tvalid5 | m_axis_data_tvalid6 | m_axis_data_tvalid7;

assign analog_data_128bit ={ m_axis_data_tdata0,

m_axis_data_tdata1,

m_axis_data_tdata2,

m_axis_data_tdata3,

m_axis_data_tdata4,

m_axis_data_tdata5,

m_axis_data_tdata6,

m_axis_data_tdata7

};

mux1_8 inst_mux1_8 (

.sclk (sclk),

.rst_n (rst_n) ,

.config_pinc (s_axis_config_tdata) , // 频率控制字

.config_poff (s_axis_phase_tdata), // 初始相位控制字

.poff_dds_ctrl (s_axis_config_tdata),

.config_pinc_0 (config_pinc_0) ,

.config_poff_0 (config_poff_0) ,

.config_pinc_1 (config_pinc_1) ,

.config_poff_1 (config_poff_1) ,

.config_pinc_2 (config_pinc_2) ,

.config_poff_2 (config_poff_2) ,

.config_pinc_3 (config_pinc_3) ,

.config_poff_3 (config_poff_3) ,

.config_pinc_4 (config_pinc_4) ,

.config_poff_4 (config_poff_4) ,

.config_pinc_5 (config_pinc_5) ,

.config_poff_5 (config_poff_5) ,

.config_pinc_6 (config_pinc_6) ,

.config_poff_6 (config_poff_6) ,

.config_pinc_7 (config_pinc_7) ,

.config_poff_7 (config_poff_7)

);

dds_compiler_0 your_instance_name0 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_0), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_0), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid0), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata0) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name1 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_1), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_1), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid1), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata1) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name2 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_2), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_2), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid2), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata2) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name3 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_3), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_3), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid3), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata3) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name4 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_4), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_4), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid4), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata4) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name5 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_5), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_5), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid5), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata5) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name6 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_6), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_6), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid6), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata6) // output wire [15 : 0] m_axis_data_tdata

);

dds_compiler_0 your_instance_name7 (

.aclk(sclk), // input wire aclk

.aresetn(rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(config_poff_7), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(config_pinc_7), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid7), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata7) // output wire [15 : 0] m_axis_data_tdata

);

reg [15:0] sample_data;

//(* keep = "true" *) reg [2:0] cnt;

always @(posedge sclk_2gHz or negedge rst_n) begin

if (~rst_n) begin

cnt <= 3'b0;

end

else if (analog_data_valid == 1'b1) begin

if (cnt == 3'd7) begin

cnt <= 3'b0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= 3'b0;

end

end

always @(posedge sclk_2gHz or negedge rst_n ) begin

if (~rst_n) begin

sample_data <= 16'b0;

end

else begin

case (cnt)

3'd0: sample_data <= m_axis_data_tdata0;

3'd1: sample_data <= m_axis_data_tdata1;

3'd2: sample_data <= m_axis_data_tdata2;

3'd3: sample_data <= m_axis_data_tdata3;

3'd4: sample_data <= m_axis_data_tdata4;

3'd5: sample_data <= m_axis_data_tdata5;

3'd6: sample_data <= m_axis_data_tdata6;

3'd7: sample_data <= m_axis_data_tdata7;

endcase

end

end

endmodule

DDS-IP核移相实现过程

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2021/06/09 19:20:43

// Design Name:

// Module Name: mux1_8

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module mux1_8(

input wire sclk,

input wire rst_n,

input wire [23: 0] config_pinc, // 频率控制字

input wire [23: 0] config_poff, // 初始相位控制字

input wire [23: 0] poff_dds_ctrl, // dds 相位偏移控制

output wire [23: 0] config_pinc_0,

output wire [23: 0] config_poff_0,

output wire [23: 0] config_pinc_1,

output wire [23: 0] config_poff_1,

output wire [23: 0] config_pinc_2,

output wire [23: 0] config_poff_2,

output wire [23: 0] config_pinc_3,

output wire [23: 0] config_poff_3,

output wire [23: 0] config_pinc_4,

output wire [23: 0] config_poff_4,

output wire [23: 0] config_pinc_5,

output wire [23: 0] config_poff_5,

output wire [23: 0] config_pinc_6,

output wire [23: 0] config_poff_6,

output wire [23: 0] config_pinc_7,

output wire [23: 0] config_poff_7

);

/*--------------- DDS 相位偏移作为输入参数传入 ------------------*/

// localparam poff_dds_ctrl = 4194303 ; // 2^22-1

//localparam poff_dds_ctrl = 176161 ; // 10Mhz 2^22-1 360度 的 1/25-周期(167773)

// localparam poff_dds_ctrl = 335544 ; // 20Mhz

// localparam poff_dds_ctrl = 838861 ; // 50Mhz

// localparam poff_dds_ctrl = 1677721 ; // 100 Mhz

// localparam poff_dds_ctrl = 4194303 > > 1 ; // 125 Mhz --(2097151)

// localparam poff_dds_ctrl = 2642415 ; // 150 Mhz

// localparam poff_dds_ctrl = 4194303 > > 2 ; // 250 Mhz

assign config_pinc_0 = config_pinc;

assign config_pinc_1 = config_pinc;

assign config_pinc_2 = config_pinc;

assign config_pinc_3 = config_pinc;

assign config_pinc_4 = config_pinc;

assign config_pinc_5 = config_pinc;

assign config_pinc_6 = config_pinc;

assign config_pinc_7 = config_pinc;

assign config_poff_0 = config_poff;

assign config_poff_1 = config_poff+ (poff_dds_ctrl > > 3);

assign config_poff_2 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

assign config_poff_3 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

assign config_poff_4 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

assign config_poff_5 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

assign config_poff_6 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

assign config_poff_7 = config_poff+ (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3) + (poff_dds_ctrl > > 3);

endmodule

仿真激励文件

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2021/06/08 19:56:44

// Design Name:

// Module Name: tb_top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_top(

);

reg aclk;

reg sclk_2gHz;

reg rst_n;

reg s_axis_phase_tvalid;

reg [23:0] s_axis_phase_tdata;

reg s_axis_config_tvalid;

reg [23:0] s_axis_config_tdata;

wire m_axis_data_tvalid0;

wire m_axis_data_tvalid1;

wire m_axis_data_tvalid2;

wire m_axis_data_tvalid3;

wire m_axis_data_tvalid4;

wire m_axis_data_tvalid5;

wire m_axis_data_tvalid6;

wire m_axis_data_tvalid7;

wire [15:0] m_axis_data_tdata0;

wire [15:0] m_axis_data_tdata1;

wire [15:0] m_axis_data_tdata2;

wire [15:0] m_axis_data_tdata3;

wire [15:0] m_axis_data_tdata4;

wire [15:0] m_axis_data_tdata5;

wire [15:0] m_axis_data_tdata6;

wire [15:0] m_axis_data_tdata7;

wire analog_data_valid;

wire [127:0] analog_data_128bit;

wire [15:0] sample_data;

wire [2:0] cnt;

initial begin

s_axis_config_tvalid = 1'b1;

//s_axis_config_tdata = 24'd16777; // ---1 MHZ 频率控制字

//s_axis_config_tdata = 24'd167770; // ---10MHZ 频率控制字 --- 由频率分辨率决定 --- (10*10^6*2^22)/250*10^6 = (0.0167772)* 10*10^6 = 167770

//s_axis_config_tdata = 24'd335540; // ---20MHZ 频率控制字

//s_axis_config_tdata = 24'd838850; // ---50MHZ 频率控制字

//s_axis_config_tdata = 24'd1677700; // ---100MHZ 频率控制字

//s_axis_config_tdata = 24'd2097125; // ---125MHZ 频率控制字

//s_axis_config_tdata = 24'd2516550; // ---150MHZ 频率控制字

s_axis_config_tdata = 24'd4194250; // ---250MHZ 频率控制字

//s_axis_config_tdata = 4194250 < < 1; // ---500MHZ 频率控制字

//s_axis_phase_tdata = 24'd0; // --- 相位控制字 - 0度

s_axis_phase_tdata = 24'd524288; // --- 相位控制字 - 45度

//s_axis_phase_tdata = 24'd1048576; // --- 相位控制字 - 90度

s_axis_phase_tvalid = 1'b1;

rst_n = 0;

#10

rst_n = 1;

//#1000

//s_axis_phase_tdata = 24'd1048576; // --- 相位控制字 - 90度

//#500

//s_axis_phase_tdata = 24'd524288; // --- 相位控制字 - 45度

end

initial

begin

aclk = 0; forever #2 aclk = ~aclk;

end

initial

begin

sclk_2gHz = 0; forever #0.25 sclk_2gHz = ~sclk_2gHz;

end

dds_ctrl your_dds_ctrl (

.sclk(aclk), // input wire aclk

.sclk_2gHz(sclk_2gHz),

.rst_n(rst_n),

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(s_axis_phase_tdata), // input wire [23 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(s_axis_config_tdata), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid0(m_axis_data_tvalid0), // output wire m_axis_data_tvalid

.m_axis_data_tdata0(m_axis_data_tdata0), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid1(m_axis_data_tvalid1),

.m_axis_data_tdata1(m_axis_data_tdata1), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid2(m_axis_data_tvalid2),

.m_axis_data_tdata2(m_axis_data_tdata2), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid3(m_axis_data_tvalid3),

.m_axis_data_tdata3(m_axis_data_tdata3), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid4(m_axis_data_tvalid4),

.m_axis_data_tdata4(m_axis_data_tdata4), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid5(m_axis_data_tvalid5),

.m_axis_data_tdata5(m_axis_data_tdata5), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid6(m_axis_data_tvalid6),

.m_axis_data_tdata6(m_axis_data_tdata6), // output wire [15 : 0] m_axis_data_tdata

.m_axis_data_tvalid7(m_axis_data_tvalid7),

.m_axis_data_tdata7(m_axis_data_tdata7), // output wire [15 : 0] m_axis_data_tdata

.analog_data_valid(analog_data_valid),

.analog_data_128bit(analog_data_128bit),

.cnt(cnt),

.sample_data(sample_data)

);

endmodule

2.3、仿真验证结果

图2-3-1、生成50Mhz正弦波信号,采样率为2G

图2-3-2、生成100Mhz正弦波信号,采样率为2G

图2-3-3、生成250Mhz正弦波信号,采样率为2G

2.4、仿真验证总结

1、单个DDS调制模块在使用的时候,如果输出频率高于采用时钟频率的一半时候,DDS输出信号会失真。比如设置输出频率超过时钟频率的一半(大于125Mhz),导致单个DDS输出信号失真。实验发现尽管单个DDS输出信号失真,整合后的输出信号(8路DDS移相后输出)仍然可以保证设置的信号频率,比如图2-3-3中单个DDS输出信号失真,但是合成后的信号依然质量较高;

2、每个DDS-IP核移相的大小为频率控制字的1/8,频率控制字的位宽为24bits,频率分辨率为100hz, 即整个DDS模块可以输出频率为100hz或者100hz整数倍的波形数据。频率控制字的位宽决定了频率分辨率的大小,频率控制字的位宽越大,DDS输出信号的频率分辨率越小,系统输出信号的频率范围越宽。

2.5、板级测试结果

图2-5-1 50Mhz正弦波信号,通过采样率为2G的DAC芯片输出模拟信号

图2-5-2 250Mhz正弦波信号,通过采样率为2G的DAC芯片输出模拟信号

-

气动理论知识-SMC品质管理课培训教材2010-02-02 818

-

波导理论知识2009-11-03 3720

-

开关电源开发人员所需具备的理论知识实践技能和工程素质2011-11-24 19264

-

初学者需要具备哪些理论知识2013-09-27 2428

-

基于FPGA的IP核的DDS信号发生器如何用IP核2015-03-10 4868

-

ip核使用问题2016-05-17 5603

-

检测技术基础理论知识2016-11-27 3318

-

USB接口的基础理论知识2008-10-15 1142

-

基于FPGA的DDS IP核设计方案2012-04-05 1150

-

开关电源的理论知识2016-03-31 899

-

维修电工中级理论知识试卷分享2017-10-11 1058

-

电信传输理论知识详解2017-11-16 734

-

学好电子技术关键是理论知识和实践动手能力2017-12-26 8146

-

变频器的故障分析和解决 实践检验、理论知识及维修水平2019-07-17 4893

-

Xilinx DDS IP核的使用和参数配置2024-10-25 5813

全部0条评论

快来发表一下你的评论吧 !