火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

描述

近日,第五届集成电路EDA设计精英挑战赛正式拉开帷幕。作为国内首家EDA上市公司,也是集成电路设计自动化(EDA)产教融合联盟常务理事单位,概伦电子一直秉持与中国集成电路产业共同成长的理念,始终致力于为中国集成电路产业打造多层次的专业人才培养机制,已连续五年支持和参与该项赛事。本次概伦电子全新发布“标准单元电路的版图自动生成”企业赛题,欢迎广大同学们踊跃报名!

赛题名称

标准单元电路的版图自动生成

赛题背景

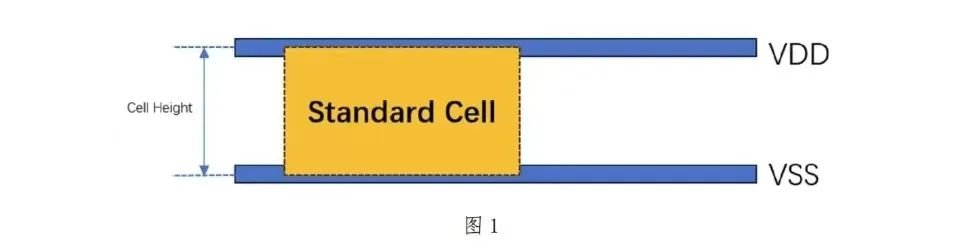

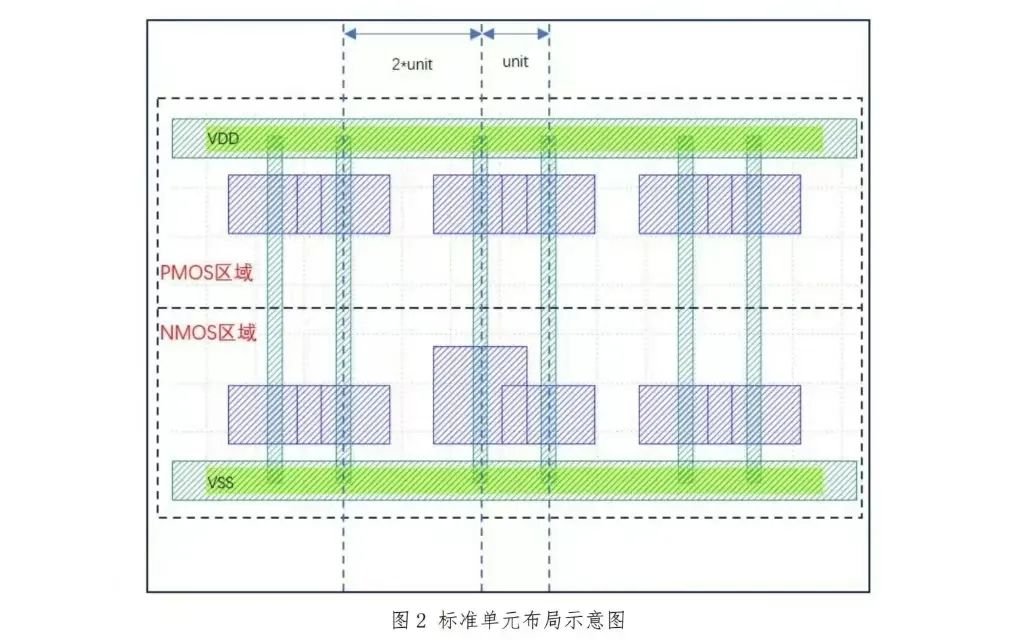

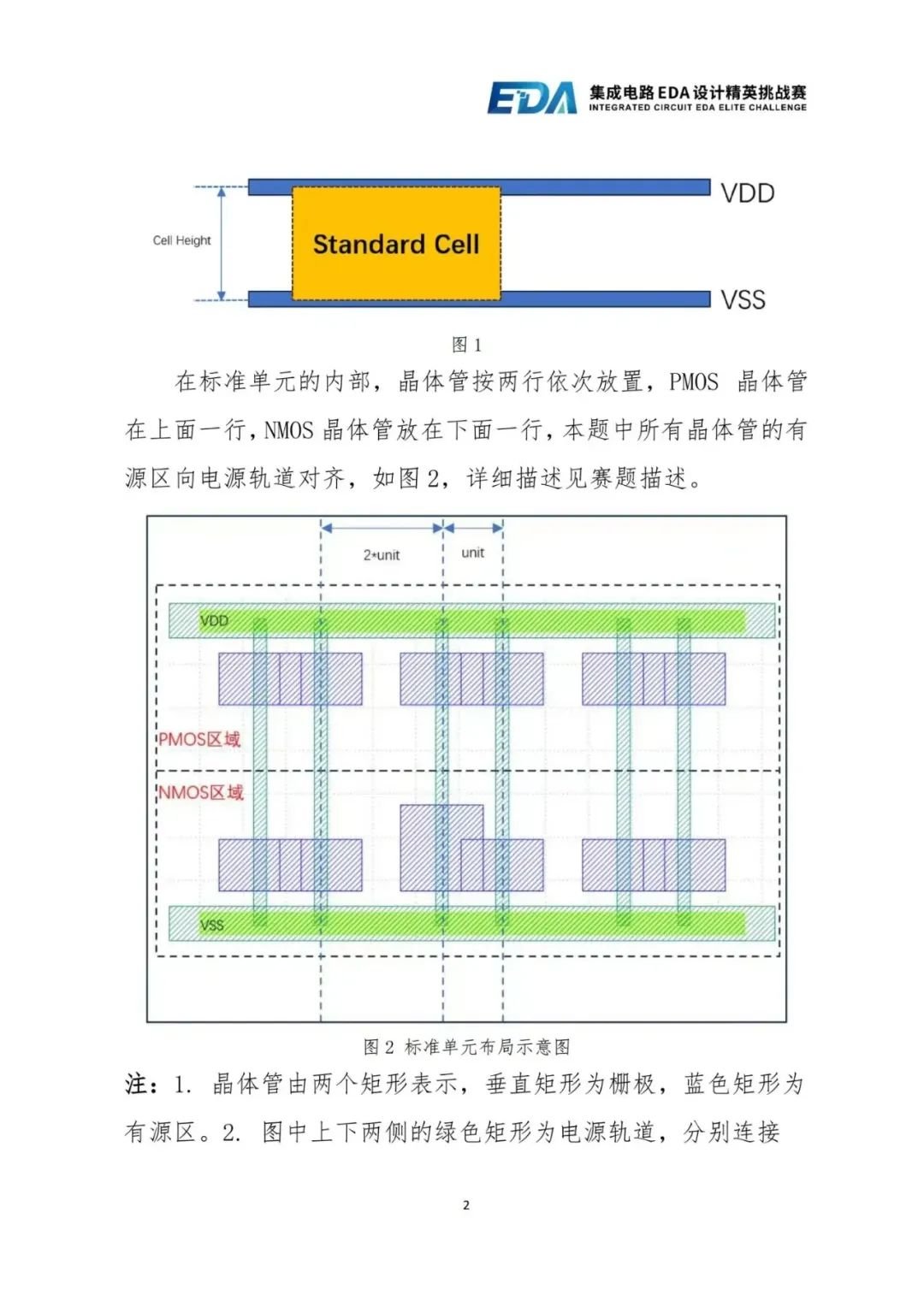

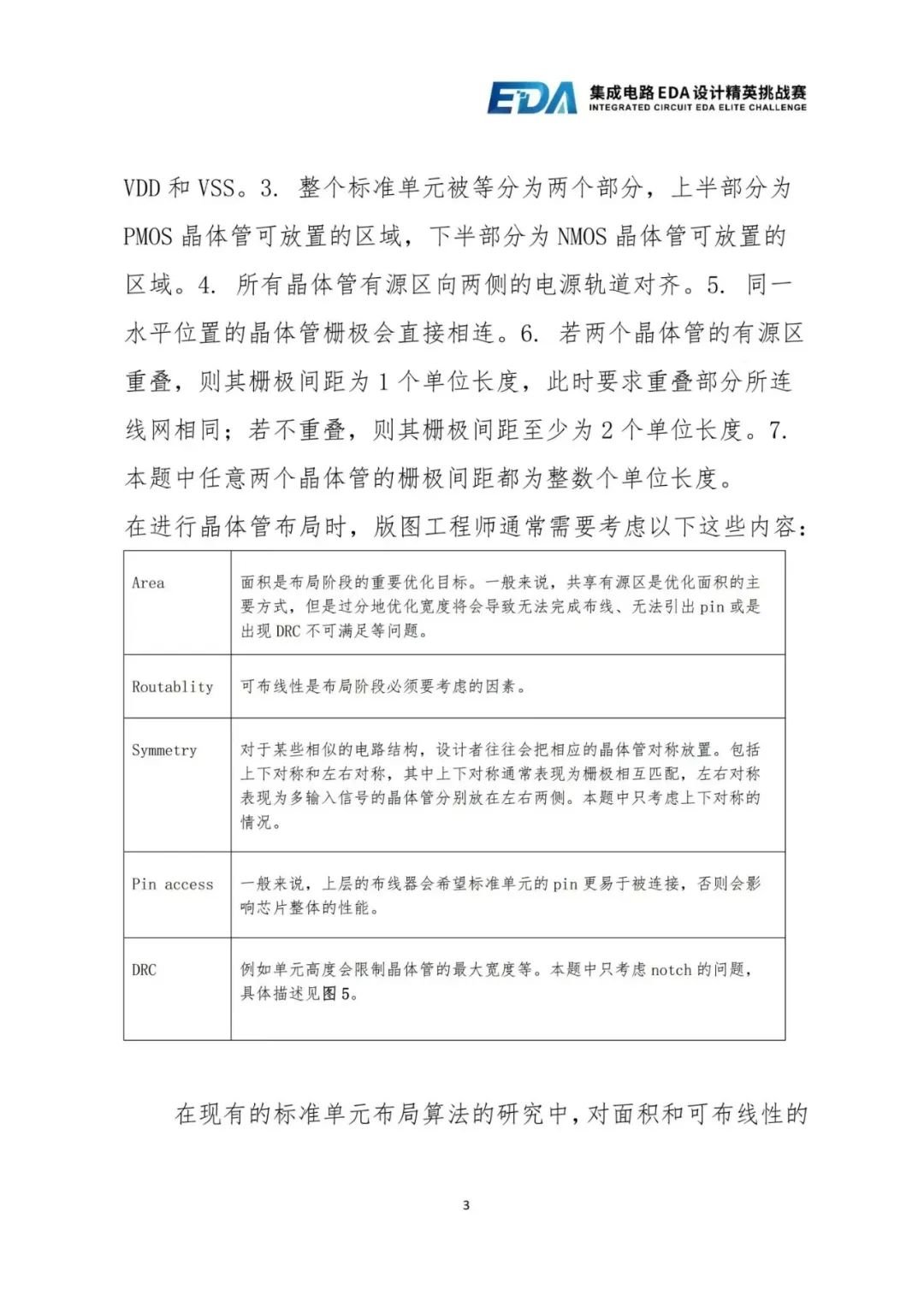

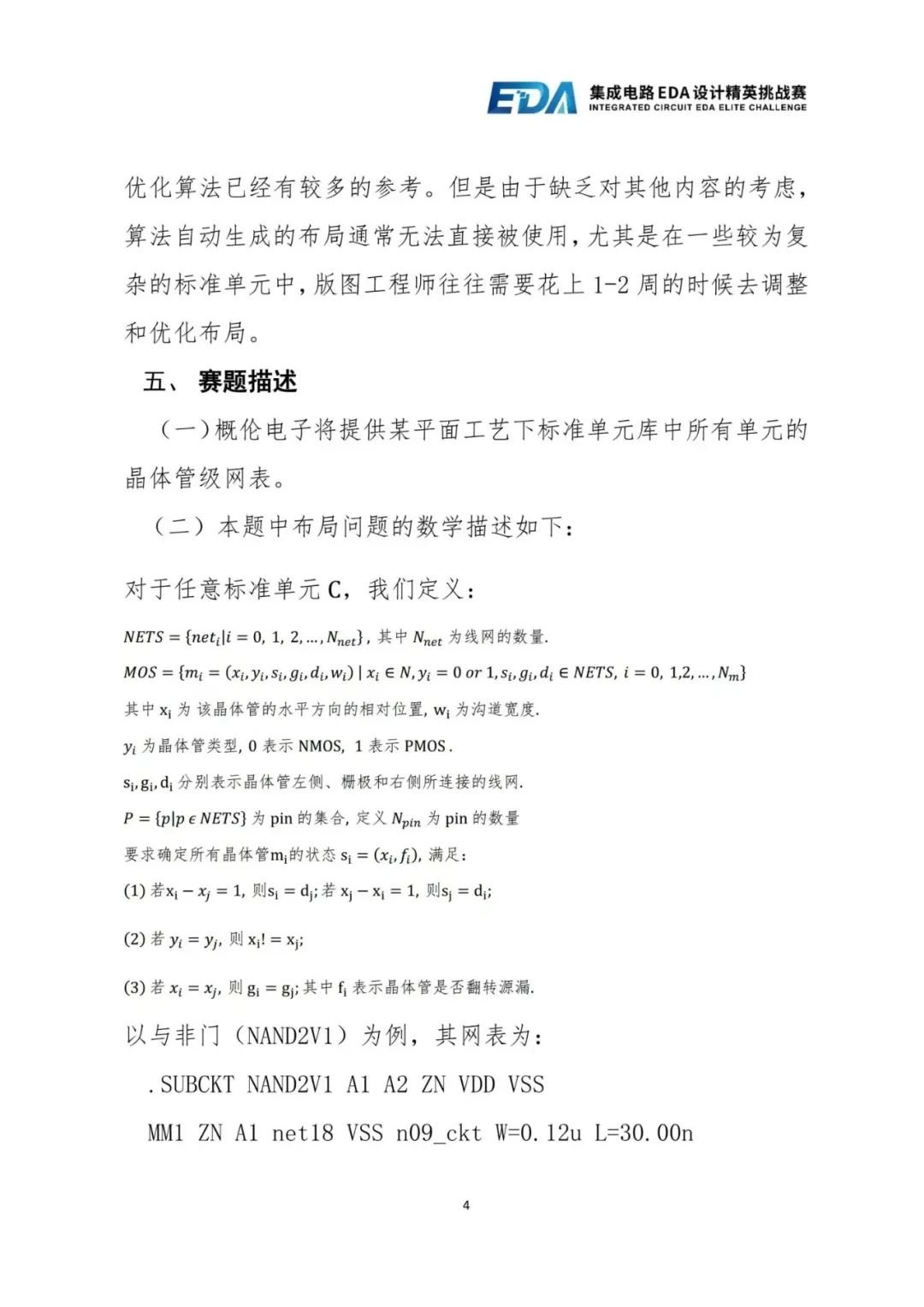

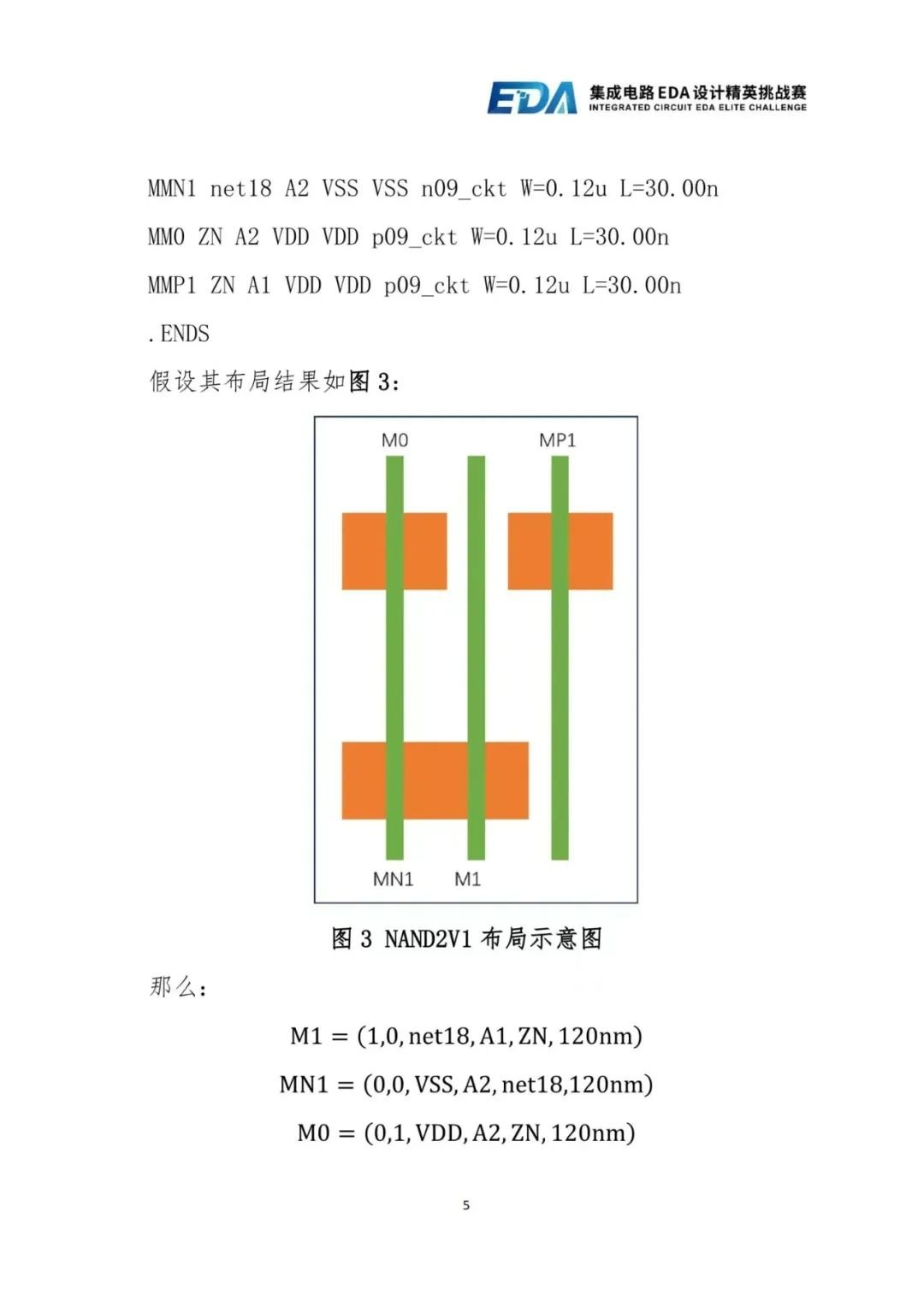

在数字电路标准单元库的开发中,版图设计是最重要的环节之一。目前标准单元的版图绘制仍然以人工绘制为主,而库中单元的数量往往多达上千颗,导致整个标准单元库的开发周期较长。如果能够提高标准单元版图设计自动化的程度,整个库的开发周期将大大缩减。标准单元的版图设计中,通常包含两个环节——晶体管布局和布线。本赛题重点关注布局环节,主要考虑组合逻辑和时序逻辑的标准单元,包含NMOS 和 PMOS 晶体管。在本题中,平面工艺下简化后的布局问题如图1所示,标准单元将被放在两条电源轨道(Power Rail)之间,高度固定,宽度不定。

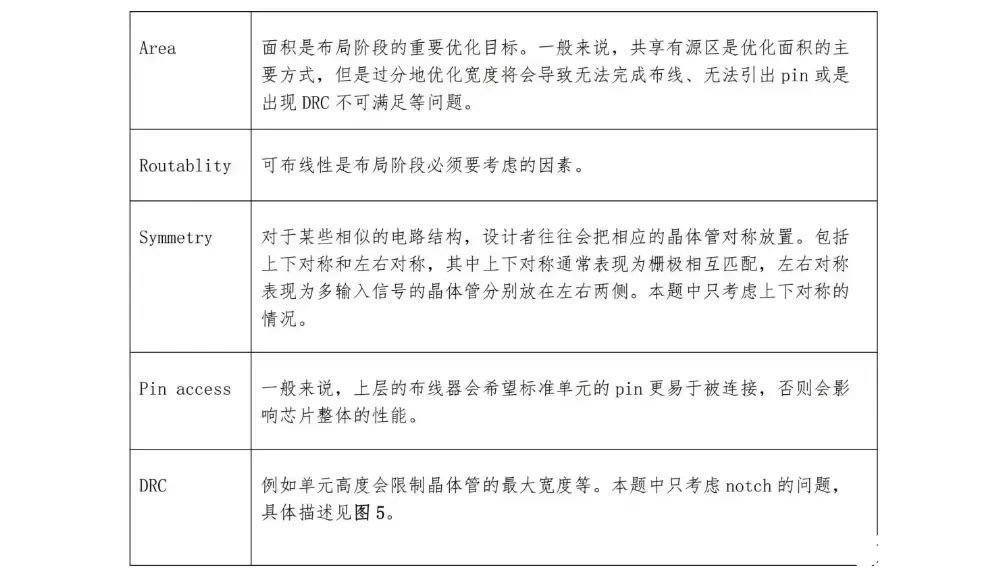

在进行晶体管布局时,版图工程师通常需要考虑以下这些内容:

赛题Chair介绍

叶佐昌

清华大学

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。赛题描述

向左滑动查看更多内容>>

大赛概况

2023 (第五届)集成电路EDA设计精英挑战赛赛程时间安排如下:

EDA设计精英挑战赛现已正式开放报名,关注官网(http://eda.icisc.cn),获取更多大赛信息。

奖项设置

麒麟杯(1支):20万菁英杯(1-2支):8万一等奖(最高15%):2万二等奖(最高30%):1万

关于概伦

上海概伦电子股份有限公司(688206.SH)作为国内首家EDA上市公司,是关键核心技术具备国际市场竞争力的EDA领军企业,致力于打造应用驱动的、覆盖集成电路设计与制造的EDA全流程解决方案,支撑各类高端芯片研发的持续发展,并联合产业链上下游和EDA合作伙伴,建设有竞争力和生命力的EDA生态。通过EDA方法学创新,概伦电子推动集成电路设计和制造的深度联动,加快工艺开发和芯片设计进程,提高集成电路产品的良率和性能,增强了集成电路企业整体市场竞争力。

扫描二维码

扫描二维码加入EDA设计精英挑战赛交流群

了解活动详情

原文标题:火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

文章出处:【微信公众号:概伦电子Primarius】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 概伦电子

-

2025 EDA精英挑战赛华大九天赛题发布2025-08-26 1849

-

2025 EDA精英挑战赛概伦电子赛题发布2025-08-25 1499

-

芯华章持续助力EDA精英挑战赛2024-12-17 1681

-

EDA精英挑战赛赛果公布!思尔芯“战队”薪火相承斩获“麒麟杯”2024-12-11 1669

-

思尔芯赛题正式发布,邀你共战EDA精英挑战赛!2024-08-03 1791

-

第五届EDA挑战赛赛果公布!思尔芯“战队”成绩斐然2023-12-27 1709

-

诚邀破题!集成电路EDA设计精英挑战赛芯华章赛题发布!2023-08-23 3020

-

思尔芯EDA助力2022第四届集成电路EDA设计精英挑战赛2022-12-08 3873

-

集成电路 EDA 设计精英挑战赛最后一天,报名即将截止,错过再等一年2022-10-11 3359

-

芯华章科技持续助力EDA设计精英挑战赛2022-01-05 3125

-

芯华章助力集成电路EDA设计精英挑战赛2021-08-10 7386

-

西电学子问鼎EDA设计精英挑战赛最高奖项麒麟杯2020-12-03 1340

-

LabVIEW挑战赛正式开赛,台北总决赛等着你!2014-05-23 13936

全部0条评论

快来发表一下你的评论吧 !