常用pcb布线经验法则是什么

PCB设计

描述

信号完整性的工作,很大一部分基于PCB走线规则的设定以及走线优化。仿真工作或者说后仿的工作都是基于PCB设计已经定型的情况下进行的,也就是说链路的相关风险已经固定了。所以,设定规则来管控风险比出现风险解决来得更重要。预防管控的能力是未来信号完整性工程师的必备基础技能。

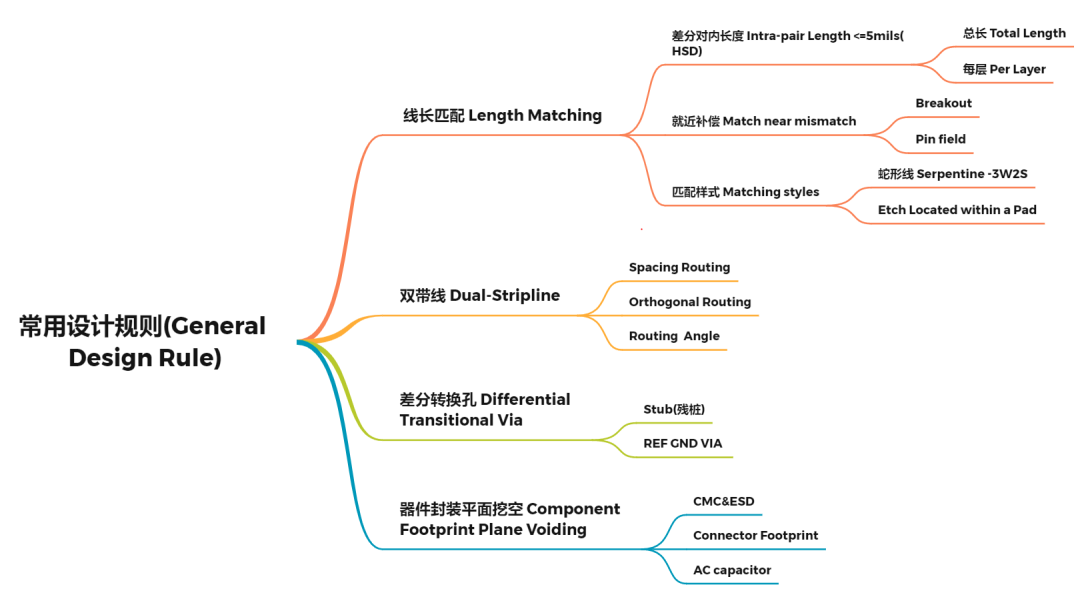

PCB设计的常用走线规则

预防管控PCB走线的风险,最最基础的知识就是熟知常用走线规则。

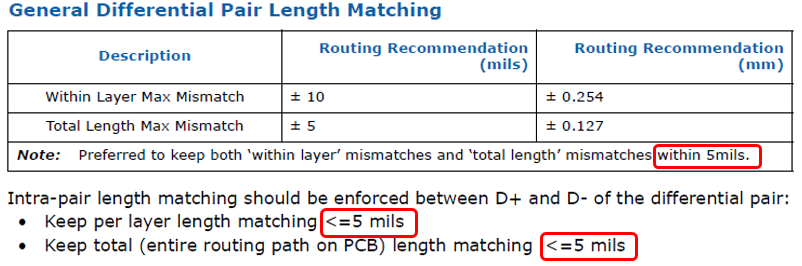

1、线长匹配 Length Matching 01.总长线长匹配&分层线长匹配 总长线长匹配的5mils已经在很多产品设计中有应用,这也是很多设计准则里提到的。

分层线长匹配的概念好像没有那么普遍,差分线的走法,BGA区域打过孔到内层,内层走线打过孔到终端,内层阻抗相对容易管控和差分线走线对称性缘故,一般情况下,表层两段距离相对比较短,所以长度的匹配一般在内层进行,也就是间接实行了分层线长匹配。很多时候,这种分层线长匹配的概念在很多产品的设计中被忽略了。

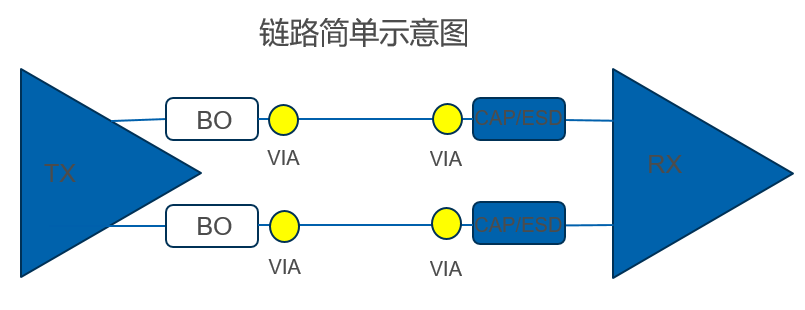

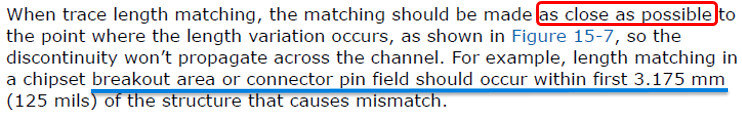

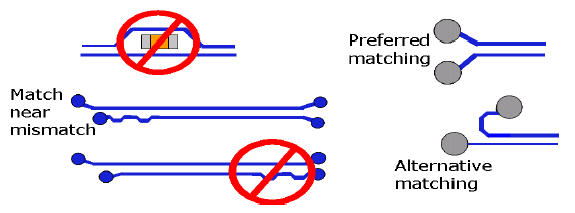

02.就近补偿

当长度不匹配发生时,推荐就近补偿,防止不连续的传播。如何就近长度匹配,产品的分类不同,要求也不同,消费类产品没有给出相关建议,只是对BREAKOUT区域以及连接器的PIN区域,给出了相关建议的数值。

就近补偿的一些走线方式:

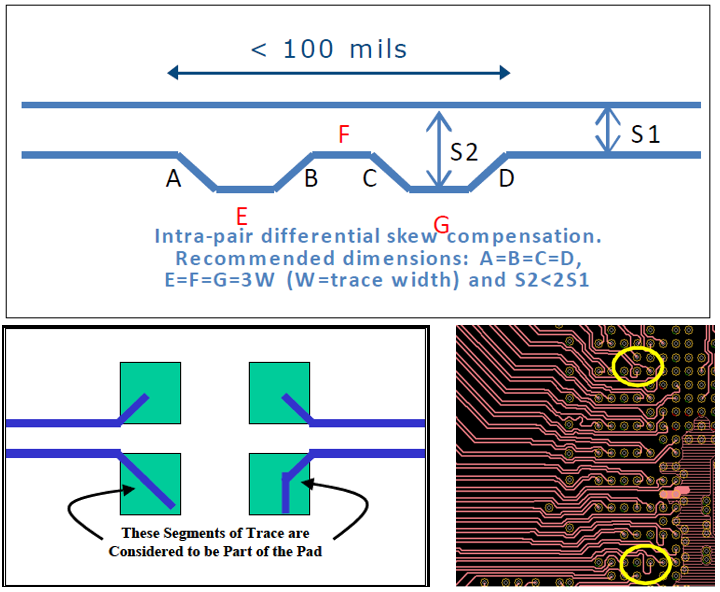

03.匹配样式

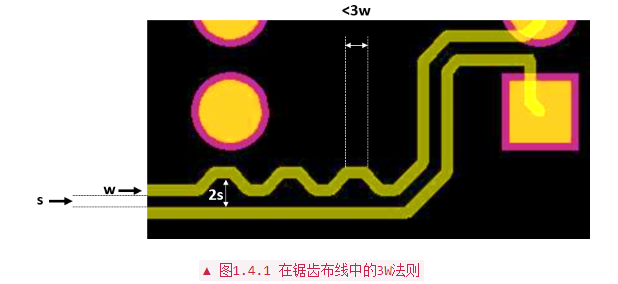

常见的匹配样式有蛇形线,PAD区域内走线等,蛇形线中3W2S原则是很多产品设计中常用的绕线方法,通过这样的操作,来达到线长匹配。 3W2S有些相互关系的,建议还是搞清楚点。相对于3W2S故意绕线来达到线长匹配,PAD区域走线匹配的方式对匹配所带来的影响更小。

需要注意的是:线长匹配最终目的是等时。

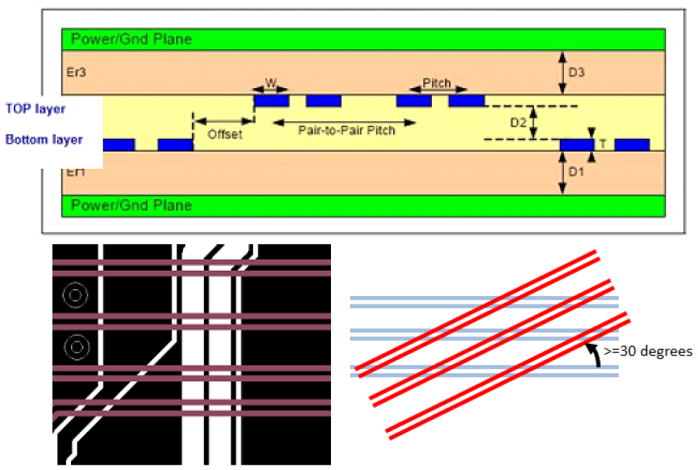

2、双带线 Dual-Stripline 高速产品的轻薄化,PCB厚度限制了走线层数,就有了高速线走在相邻两层上,为了减少相互的串扰,走线的方法有间距管控(DDR部分实现难度比较大),垂直走线(这种方法实现难度比较大),30度角走线(这种方法比较推荐)。

双带线是未来产品设计的一大趋势,细节性的东西很多,比如双带线相互平行重复度及长度等。

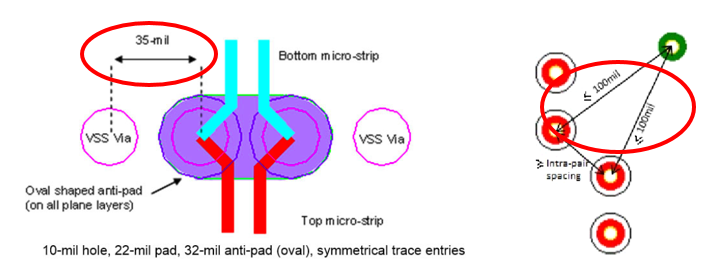

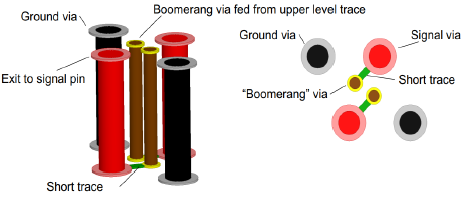

3、差分转换过孔 Differential Transitional Via

PCB走线,过孔是不可缺少的部分,这里不讲盲埋孔之类,只讲差分过孔处理方式。 不同产品有不同的设计细则,但大体是相通的: 1.如果差分过孔stub(残桩)较长,信号的速率比较高(比如PCIe4.0),要做Backdrill(背钻); 2.差分过孔如果转换参考层,要打回流地孔,地孔到VIA的距离要大于本身的差分过孔距离,同时地孔要在100mils以内。

说到stub(残桩),还有一种U-turn的走法,在终端THM连接器会用到。

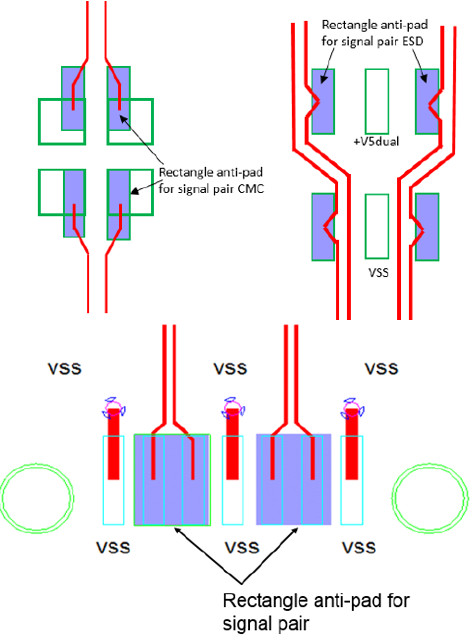

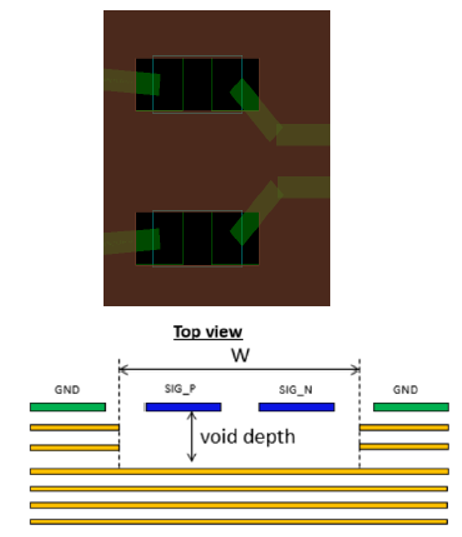

4、器件封装平面挖空 Component Footprint Plane Voiding

这里说的器件不仅仅是USB中要用的Electrostatic Diode (ESD) 和Common-mode choke(CMC),也包括高速链路中的匹配电阻,还有耦合电容,还有SMT连接器等。对其进行优化,是减少阻抗的突变。

优化处理的方式就是相邻平面层进行挖空(Voiding)。

几个有争议的PCB布线经验法则

有人说:如今,仍然还能看到一些在20年前就常见的PCB布线的经验法则,它们现在还被广泛遵守和适用吗?确切的答案是“也许吧”。一些关于PCB设计论坛中的遵守/避免布线法则,使得PCB设计者在这些规则也许不适用的地方要么遵守,要么忽略它们。一些情况下,这未必造成电路板设计失败。正像一些有经验PCB设计者所说,电路板是出于偶然的机会恰好可以正常工作。关于PCB设计的经验法则的讨论并不是说它们是正确还是错误,问题是这些讨论往往缺乏应用场合的针对性。下面希望将这些规则背后所适应的场景讲清楚,能将不同的规则在什么时候适用,什么时候需要避免阐释准确。

下面将一些常用到的PCB布线经验法则抽丝剥茧,分析它们背后所适用的场景。

一、垂直布线

垂直布线的规则是说在相邻信号层的引线需要相互垂直,以减少相互之间互感引起的串扰。在高频信号中,通过电容耦合产生的串扰占主要成分,在垂直引线之间产生电流尖峰。 当信号的变化沿时间,或者频率较低(小于几个GHz),相邻信号层垂直布线件的耦合电容干扰小。在射频(RF)频段(几十个GHz),引线间交织产生空穴谐振,没有被地线包围导体结构会在一些特殊频率点产生电磁谐振。此时即便引线间是垂直的,也会在它们之间引起强的串扰。为了消除一切频率点上的干扰,简单有效的方法就是采用多层板,在信号层之间使用隔离层。在当代信号高速变化的应用中尤其重要。当你对正交线之间耦合强度拿不准时,你需要使用基本串扰仿真软件对垂直引线进行检查,看它们之间的串扰是否在噪声容限范围之内。此时,你更需要对信号回流路径进行规划,这在垂直布线中是一个主要的问题。

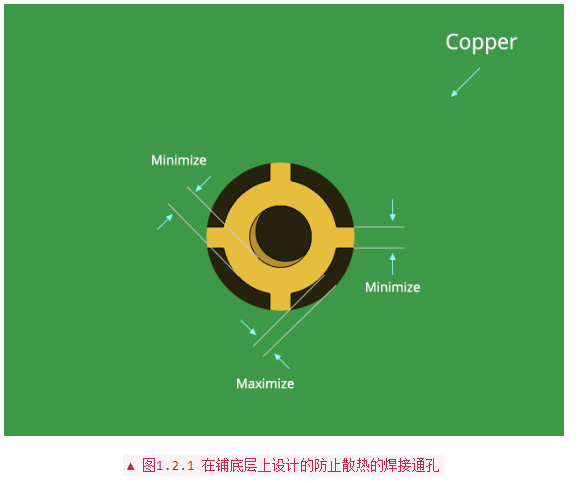

二、散热过孔

这是一个经典的“遵守/避免”法则,常常引起争论。一些PCB设计者说他们从来不使用防止散热过孔,并从未遇到焊接和组装方面的问题。而另外一批人则坚持防止散热过孔需要在每一个平面相连的时候都需要使用。他们到底谁对呢?他们的观点分别适用于不同的场合。如果你手工焊接电路板时,你需要提高烙铁头的温度以补偿焊接过孔在铜层散热带来的焊接问题。但如果使用波峰焊接时,则需要使用防止散热过孔来防止器件松脱、冷焊、立碑等现象。

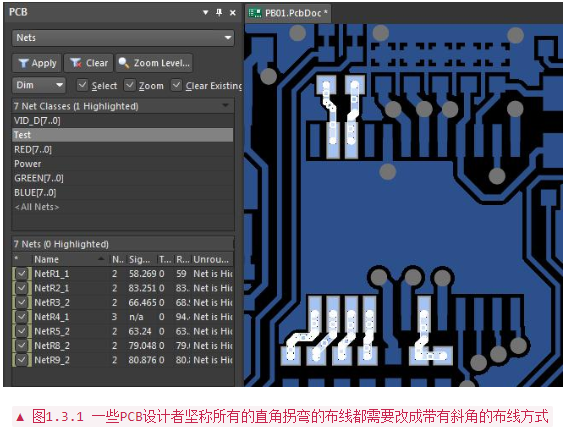

三、直角布线

这个PCB布线法则也许最令人又爱又恨。如今我仍然看到很多PCB设计者坚称在任何时候布线都不能够拐直角,理由也是五花八门。比如他们说电子在引线中运动时拐直角弯困难,但他们也不想想,在电路板上的所有过孔可都是与引线垂直的呀。还有些理由显得比较靠谱,比如通过45°拐角可以减少引线长度,所有直角拐弯布线都需要倒角。还有的说直角拐弯会在电路板酸性腐蚀液中产生酸蚀陷阱,在现在广泛使用碱性电路板腐蚀液中则没有这个问题。 除非你的电路板工作在50GHz以上的高频(涉及到毫米波雷达/5G通讯)电路,你无需担心引线拐直角。实际上,在电路板布线时你可以使用任何你所喜欢的角度来铺设引线。如果你所使用的的PCB设计软件内置有电磁场求解功能这会使得你布线更加容易。

四、“3W”法则

第一个版本的"3W法则是说,在相邻两条引线之间的间隔应该大于等于引线宽度的三倍 ,为的是降低引线之间的磁通量耦合,进而减少引线见的电磁干扰。这个法则也许忘记了,引线之间的电磁耦合是与引线回路重叠面积成正比,而不是引线之间的距离;因此将引线回路重叠面积降低,引线间距不用受到3W法则限制。就像前面垂直布线一样,通过基本电磁干扰仿真可以检查不同布线间距带来的影响。 “3W”法则的另外一个版本是指在引线长度匹配时所使用的锯齿布线时,锯齿宽度需要大于等于引线宽度的三倍,这可以将引线阻抗的不连续性降到最低。

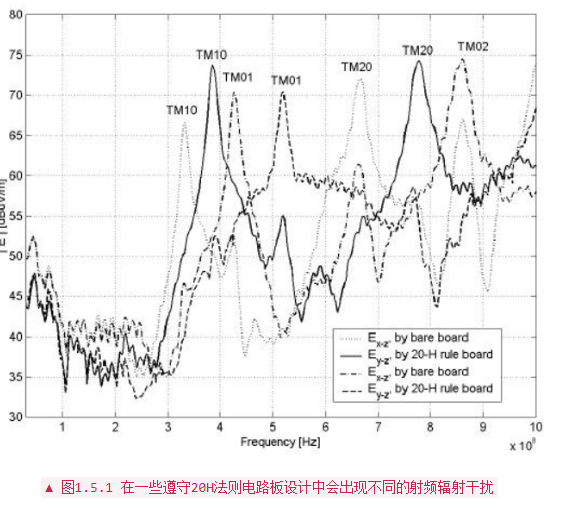

五、“20H”法则

这个法则定义了PCB中的地线层与电源层之间重叠距离,在现代PCB设计时需要将电源铺设在地线附近,这样可以保证它们之间具有足够的层间电容,进而在高速电路板上减少电源波动。但实际测量结果会发现结果很复杂。有些在300MHz时遵守20H法则可以降低电磁辐射;但在地线-电源层之间会出现高频谐振,它们结构类似于波导,反而会加重线路之间的高频干扰。

所以,在实际应用中,如果你的电路频率在GHz以内,可以遵循20H法则;否则,20H法则有可能会带来更糟糕的结果。

总结

以上就是PCB走线相关常用规则,有些是有争议的。当然,针对不同产品会有不同细则,殊途同归,所有的规则都是为了减小串扰,反射,损耗等,来保证信号完整性。如果遇到一些规则相互矛盾,这个时候就需要信号完整性工程师做出取舍,给出合理方案。

编辑:黄飞

-

PCB布线中常用经验法则分析2023-02-19 1440

-

PCB设计必需遵守/避免布线法则2022-11-09 951

-

PCB设计的经验法则2022-11-02 1197

-

高速PCB布线经验分享2022-02-12 6750

-

一些与众不同的PCB布线经验规则2021-11-01 3895

-

估算RMS周期间抖动,经验法则是什么?资料下载2021-04-09 1161

-

15条高速PCB布线经验分享2021-03-04 1516

-

PCB布线设计-PCB布线设计经验大全(六)2016-08-16 1329

-

PCB布线的几点经验2016-07-26 811

-

PCB布线经验技巧总结2016-01-20 1027

-

PCB布线经验(九大经典文档)2015-12-25 1209

-

pcb 设计的经验法则2012-08-20 7563

-

PCB布线的经验之谈2009-05-12 893

全部0条评论

快来发表一下你的评论吧 !