把子模块包含网表的RTL代码添加到BD中的方法分享

描述

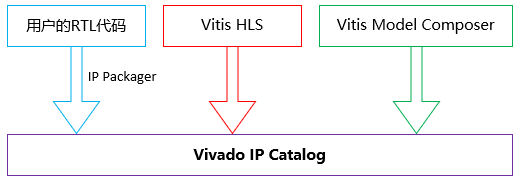

Vivado以IP为核心的设计理念的一个重要支撑就是IP Integrator(简称IPI,IP集成器)。用户可以很便捷地把VivadoIP Catalog中的IP拖到IPI中形成Block Design(.bd文件)。

同时,对于用户自己的RTL代码,可以借助IP Packager先封装成IP,再导入到IP Catalog中,然后在IPI中使用。

此外,Vitis HLS、Vitis Model Composer都可以将用户设计以IP形式输出供用户导入到IP Catalog中调用。

尽管如此,不得不说借助IP Packager封装IP的过程还是有些繁琐的。当然,我们也要看到封装IP带来的好处就是便于不同设计团队开发使用。IPI的功能仍在不断增强。

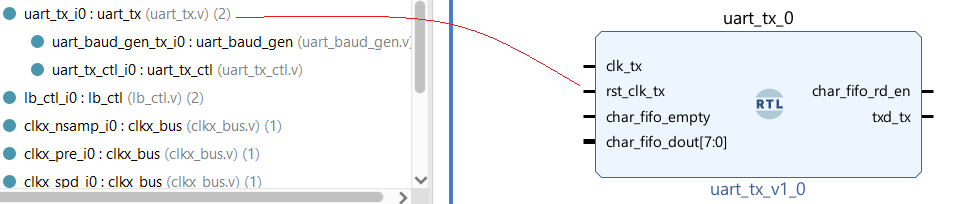

一个显著的功能是用户可以直接将RTL代码拖到IPI中构成BD,如下图所示。要求RTL设计的顶层如这里的uart_tx必须是Verilog或VHDL描述。SystemVerilog/VHDL-2008不支持此功能。

此功能被称为模块引用(Module Reference)。

关于模块引用,我们可能会碰到以下问题。

问题1:待引用的顶层采用的是SystemVerilog或VHDL-2008描述的。

因为模块引用不支持SystemVerilog也不支持VHDL-2008,在这种情况下,可以用Verilog或VHDL先对该模块封装以下,这样就可以将封装后的.v或.vhd模块添加到IPI中。

问题2:若待引用的顶层其子模块包含IP Catalog中的IP(以.xci形式存在),那么是否支持此功能?

模块引用功能允许待引用的顶层其子模块包含.xci IP,但并不是所有的IP都支持。可通过如下命令获取不支持此功能的IP。可以看到NoC、CIPS和PS是不支持的。换言之,目前的Vivado版本(2023.1)只能在IPI中直接使用这些IP。

审核编辑:刘清

-

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?2016-09-07 15563

-

可以将块设计添加到库中吗?2019-04-18 1277

-

有什么方法能将以太网功能添加到PSoC设计中去?2019-08-13 2121

-

将新库添加到Petalinux rootfs的最简单方法是什么2020-05-22 3793

-

怎样将PMSM模块添加到Simulink中2021-09-23 3046

-

请问如何将自己的代码添加到工程中?2022-01-05 1256

-

如何在arduino IDE上将SPI模块作为库添加到nodemcu代码中?2023-02-24 528

-

Yocto S32G添加新层,如何添加到图像?2023-04-25 714

-

包含路径不会添加到项目中的每个源文件怎么解决?2023-05-05 612

-

如何将Crosswalk添加到Cordova应用程序中2018-11-07 3263

-

谷歌将在本周把隐私信息添加到ios应用中2021-01-07 2111

-

S7-1200将模块添加到组态的方法2022-03-11 7288

-

将RTL模块添加到Block Design的步骤2023-06-11 6091

-

西门子博途S7-1200:将模块添加到机架的方法2023-09-04 10843

-

安装python怎么添加到环境变量2023-11-23 4705

全部0条评论

快来发表一下你的评论吧 !