ESD静电放电分析及整改总结

EMC/EMI设计

描述

ESD应该是EMC中最常见也是遇到问题最多的测试项,许多硬件工程师遇到试验Fail时,无从下手,今天就来谈谈ESD分析与整改的理论基础,不涉及实际案例应用。

█ ESD干扰方式

地弹

根据静电放电电流波形可知,其电流具有较宽的频率范围。如此高频率电流通过参考地平面时,理想情况下参考地平面阻抗处处相等,地电平抬升或者降落对系统信号以及电源无明显影响。但是由于参考地电位受静电电流冲击产生的现象,即所谓的〝地弹〞现象。

容性耦合

容性耦合是指电磁骚扰源通过电路或系统之间的电场并以耦合电容作用于敏感对象的电磁耦合方式。

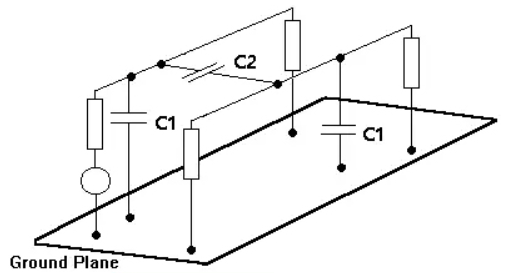

静电放电产生容性耦合的机理是:静电电流流过阻抗变化的参考地平面时,会在参考地平面上产生变化电压。平行于静电电流泄放路径参考地平面的导线,会因为容性耦合产生骚扰电压,当骚扰电压幅值超过芯片容错电压时则会引起芯片误动作,严重情况下会导致芯片内部半导体器件过压击穿而彻底损坏。

感性耦合

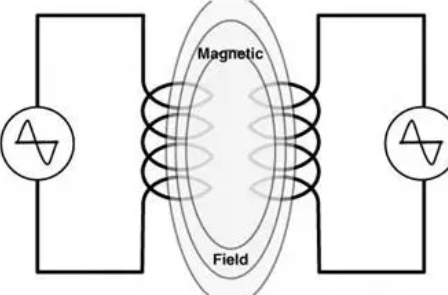

感性耦合是指电磁骚扰源通过电路或系统之间的磁场并以耦合电感形式作用于敏感对象的电磁耦合方式。

静电放电产生感性耦合的机理是:静电放电变化电流流过参考地平面时,当遇到阻抗较低的信号布线(互感耦合到信号线上面,此时电压突变),会沿着阻抗较低的信号布线流进芯片,在芯片内部产生骚扰电压或者以电流形式冲击芯片,严重时会造成芯片内部半导体器件因过流烧毁。

辐射

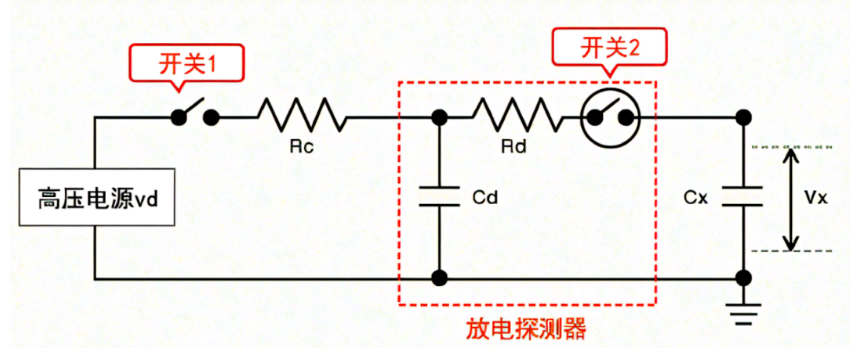

如上图所示,静电枪充电开关1接通时,充电电阻Rc与Cd电容构成充电回路,给电容充电;放电开关2接通时,Cd电容与Rd电阻构成放电回路。当放电开关接通瞬间通过放电枪头对DUT放电,此时瞬间的高压脉冲流过放电电阻Rd产生变化的电流,变化的电流产生变化的磁场,从而形成丰富的电磁场干扰。

█ ESD电流泄放路径

静电电流会选择阻抗最低的路径返回到源端。ESD整改简单来说就是找出静电电流泄放路径中的敏感信号,并对其进行ESD防护,提高其抗静电能力。如果产品已经DV/PV,无法改变PCBA,则想办法设计一条阻抗最低路径,使电流返回源端。

█ ESD分析方法

现象分析法

静电放电测试失效过程中,肯定会伴随着各种各样的现象,根据静电放电的Fail现象结合具体的电路,快速定位Fail器件。

排除法

排除法属于破坏性试验,针对静电放电过程中出现的异常现象,使用静电枪直接对DUT敏感IC进行接触放电,找出与静电放电过程中出现的异常现象,增加ESD保护。

屏蔽法 对于PCB来说,最显而易见的方式就是加屏蔽罩(分析时候可以用铜箔或者导电胶带接地),第二个简单有效的屏蔽方法是拉远距离,使敏感器件远离静电放电电流路径,减小敏感器件与静电放电路径之间的耦合。

█ ESD整改步骤

1. 当EMC技术员反馈ESD测试Fail时,首先确认Fail产生的初始Setup; 2. 问题现象确认清楚后,就需要对问题现象进行深入的分析。 3. 根据问题现象分析,做出初步的原因判断,进行相关试验验证,不断排除缩小问题的范围,直至锁定敏感信号、元件、或者模块电路。 4. 根据问题分析试验结果,结合具体电路和结构,拟定解决方案。

编辑:黄飞

-

案例分析||医用电钻静电整改2016-07-29 4896

-

电缆对静电放电的影响分析2020-10-23 2595

-

微小医疗产品ESD静电整改问题2023-02-07 13908

-

ESD整改方案—完整地对ESD静电管的作用2018-12-25 2061

-

静电抗扰度(ESD)整改案例—蓝牙音箱整改2019-01-28 2121

-

模拟分析静电放电(ESD)事件2019-08-11 10828

-

某产品ESD静电放电设计与整改案例2022-10-12 6136

-

ESD静电整改有什么基本思路?2023-11-02 1637

-

【电磁兼容技术案例分享】静电放电(ESD)整改案例分析2023-11-03 2632

-

ESD静电的原理与整改建议?2023-12-07 2050

-

静电ESD整改:如何让企业避免损失?2023-12-08 1300

-

静电ESD整改:原因、影响与解决方案详解?2024-03-13 2138

-

ESD器件与静电放电的关系2024-11-14 1633

-

ESD静电与静电放电的区别与联系2024-11-20 2447

-

【电磁兼容技术案例分享】控制柜静电放电整改分析案例2025-07-29 731

全部0条评论

快来发表一下你的评论吧 !