PCB板上晶振电路的设计

描述

时钟(Clock)在一般SoC电路上是必不可少的,精准的时钟通常由晶振提供,晶振很难集成到芯片中去,而是作为分立元件设计在PCB上。它就像是人的心脏,晶科鑫人的使命便是为电子硬件装上一颗安心的心脏,如果时钟出错了,整个电路或者通信就会发生问题。

比如,16MHz晶振给一个2.4G蓝牙芯片提供参考时钟,如果16MHz的晶振出现频偏,比如偏-48ppm(频率为15.999223MHz),由于射频是参考时钟倍频上去的,也会出现-48ppm的频偏(蓝牙频点变成2,399,883,450Hz,约100KHz的频偏),造成蓝牙与标准频率的对端无法通信。因此一个好的时钟电路,一颗高精度的晶振是非常必要的,晶科鑫30余年来一直为广大客户提供高品质高精度晶振,并会帮助客户上板调试晶振电路使时钟至最佳最精准状态,力求帮助客户的方案得到最好的稳定性。此篇文章对时钟电路中的晶振电路layout简单做一下阐述。

对于晶振电路,我们需要从几个方面考虑设计:

1、降低寄生电容的不确定性

2、降低温度的不确定性

3、减少对其他电路的干扰

设计注意点:

1. 晶振尽量靠近芯片,保证线路尽量短,防止线路过长导致串扰以及寄生电容。

2. 晶振周围打地孔做包地处理。

3. 晶振底部不要走信号线,尤其是其他高频时钟线。

4. 负载电容的回流地要短。

5. 走线时先经过电容再进入晶振。

6. 封装较大,可从晶振中间出线。

7. 如果有测试点,使stub尽量短。

8. 走线可以走成假差分形式。尽量走在同一层。

9. 部分晶振底下需要做掏空处理,以防电容效应以及热效应造成频偏。

10. 如果是铁壳晶振,外壳做接地处理,提高抗干扰能力。

下面分别举例贴片无源晶振及有源晶振的走线方式:

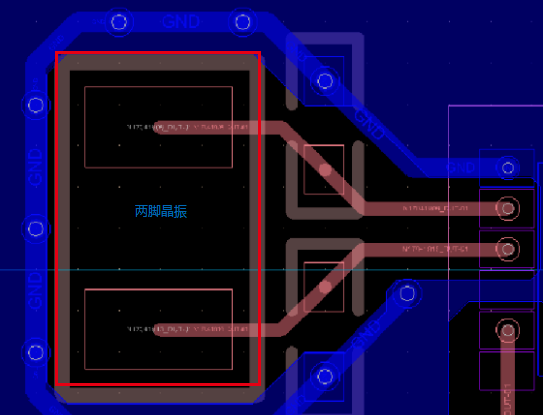

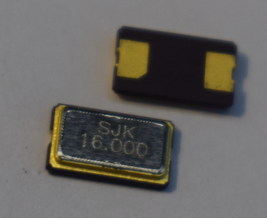

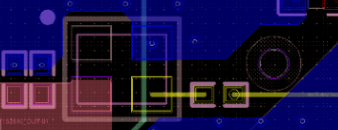

两脚贴片无源晶振

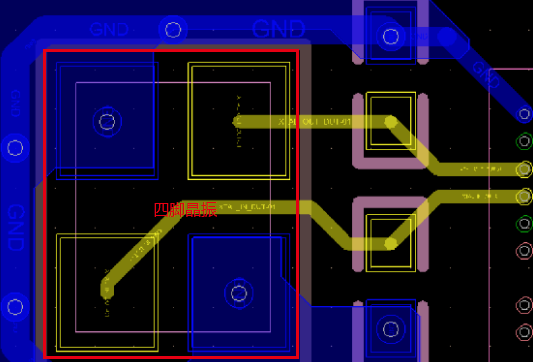

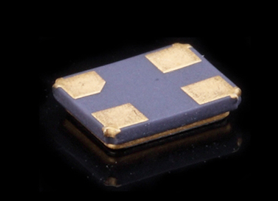

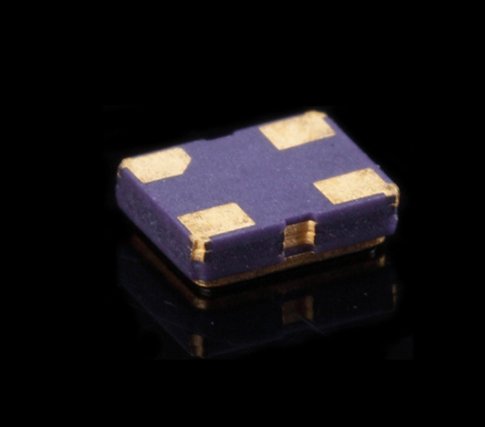

四脚贴片无源晶振

HTOL测试板上有源晶振的布局:

由于老化测试中一般芯片都在socket中测试,所以晶振不能与Socket放置在同一面,否则晶振会距离芯片较远。

晶振放在反面则需要打孔后连接至芯片管脚,此时需要在打孔附近增加回流地孔。

有源晶振需额外注意电源滤波电路处的电容,从大到小依次靠近晶振放置。

贴片有源晶振

-

晶振在PCB板上如何布局2025-05-26 2032

-

在PCB板上加入晶振的原因主要有哪些?2024-04-09 7648

-

为什么PCB上要有晶振?晶振的类型和作用2023-03-16 5880

-

从PCB电路板上认识了解晶振2023-02-03 5058

-

赛思晶振来袭!一文带你了解电路板上的“心跳”2022-12-16 2502

-

晶振在PCB板上如何布局?都是精髓!2022-11-14 2920

-

晶振在PCB板上如何布局?2022-11-11 3156

-

PCB板上常用的晶振有哪些?2019-05-20 8245

-

电路图晶振符号2017-04-10 8131

-

PCB上晶振封装的设计2016-07-23 5807

-

晶振和PCB板不吻合了2013-11-14 2339

全部0条评论

快来发表一下你的评论吧 !