LVDS- 静电放电及插拔脉冲电压防护

描述

方案简介:

LVDS 是一种低摆幅的差分信号技术,利用非常低的电压摆幅(约 350mV)在 2 条 PCB 走线或者一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输,采用 LVDS 接口,可以使得信号在差分 PCB 线或平衡电缆上以几百 Mbps 的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗,LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用,常见于液晶电视中,LVDS 其较高的数据传输速率,普通的防护方案会对数据的传输造成一定影响。此方案高速差分信号部分采用集成低压四通道保护(有效降低后端残压值)、超低容值、低漏电、低残压的 ESD 防护器件,在不影响数据传输的前提下满足 IEC61000-4-2 Level 4 静电放电防护需求,让后端的电路得到有效防护。

产品图示:

SRV05-4

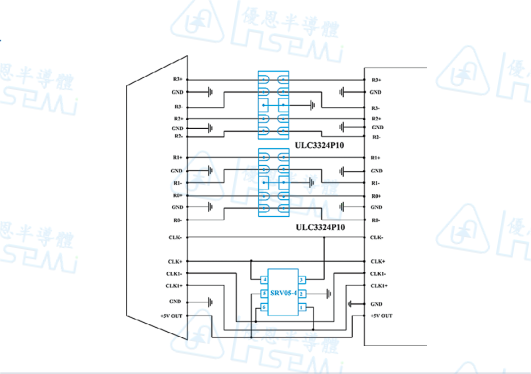

SRV05-4 ULC3324P10

ULC3324P10应用示例:

符合要求 : ESD IEC 61000-4-2 Level 4

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LVDS静电放电防护方案2024-09-19 1558

-

SD卡-ESD静电放电及插拔脉冲电压防护设计-优恩半导体2023-05-15 2781

-

优恩半导体-USB3.1- ESD静电放电及插拔脉冲电压防护 II2023-04-11 1660

-

信号端口防护-USB2.0- 静电放电及插拔脉冲电压防护-优恩半导体2023-03-02 1575

-

音频接口丨接口静电放电及插拔脉冲电压ESD防护2023-01-14 2753

-

DC12V- 电源口ESD静电放电及插拔脉冲过电压防护##esd #ESD防护 #静电防护 #电路设计深圳市优恩半导体有限公司 2022-08-08

-

DC24V- 电源口静电放电及插拔脉冲过电压防护2022-06-23 1992

-

关于静电放电及防护的全面介绍2019-07-02 4496

-

电路静电防护小科普:了解放电器件与ESD防护方法2019-05-28 3150

-

静电放电及防护基础知识2017-11-23 2247

-

RS232端口浪涌和静电防护设计2017-07-27 5380

-

RGB接口静电放电防护方案2017-04-21 4702

-

USB3.0静电放电防护解决方案2015-04-28 7766

全部0条评论

快来发表一下你的评论吧 !