国芯思辰|替代AD9231BCPZ,国产12位SC1232用于数字射频接收器

描述

近年来,数字射频接收器技术取得了巨大进步,这主要得益于高速ADC的性能发展。直接转换、中频采样以及软件定义的无线电架构开始在现代射频接收器设计中普及。现在ADC中也包含许多以前在独立器件中使用或者通过软件实现的数字信号处理 (DSP) 功能;选择适合某个系统的正确ADC并不仅仅是选择分辨率(位数)和采样速率。

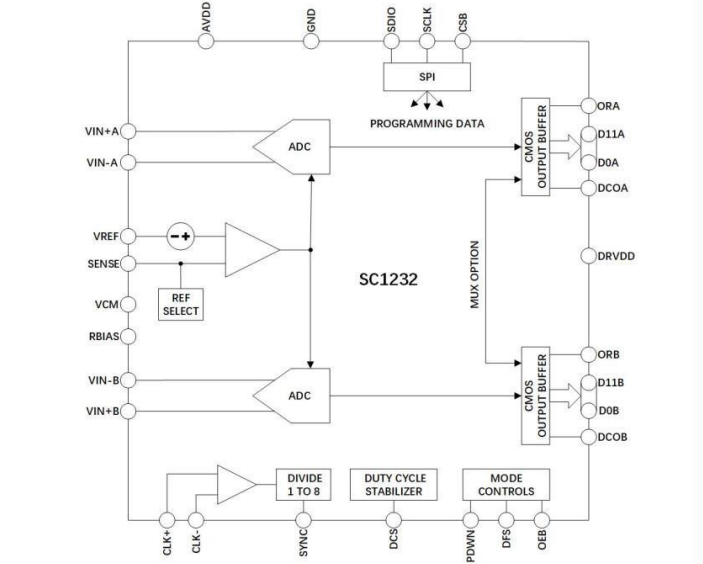

如今的高速/高分辨率ADC是具有众多规格和性能特征的复杂系统。国产芯炽的双通道12位20/40/65/80MSps ADC SC1232非常适合高灵敏度的接收机应用,并且改善了那些在接收机设计中最为重要的参数:数字化带宽采样、保持带宽采样、信噪比等。

SC1232 ADC内部采用的是多级差分流水线架构,内置输出纠错逻辑,在 80MSPS数据速率时可提供14位精度,并保证在整个工作温度范围内无失码。该ADC内置多种功能特性,可使器件的灵活性达到最佳、系统成本最低,例如可编程时钟与数据对准、生成可编程数字测试码等。可获得的数字测试码包括内置固定码和伪随机码,以及通过串行端口接口(SPI)输入的用户自定义测试码。

SC1232主要性能:

• 1.8V 电源供电

• 1.8V至3.3V输出电源

• 低功耗:每个通道31mW(20MSPS)

每个通道66mW(80MSPS)

• 信噪比(SNR):72.5dBFS(30.5MHz输入)

69dBFS(200MHz输入)

• 无杂散动态范围(SFDR):82dBc(30.5MHz输入)

74dBc(200MHz输入)

• 微分非线性(DNL):±0.2LSB(典型值)

• 片内基准电压源和采样保持电路

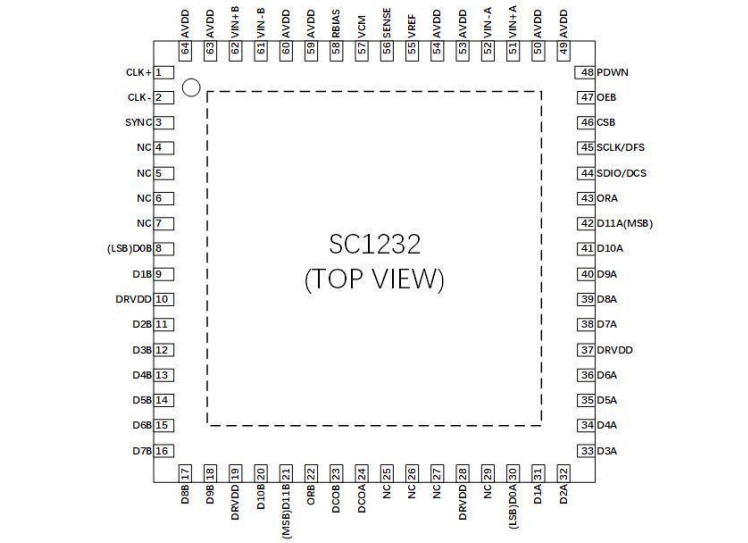

• QFN-64封装9mm×9mm

SC1232采用一个差分时钟输入来控制所有内部转换周期。数字输出数据格式为偏移二进制、格雷码或二进制补码。每个ADC通道均有一个数据输出时钟(DCO),用来确保接收逻辑具有正确的锁存时序。该器件支持1.8V和 3.3V两种CMOS电平,输出数据可以在单条输出总线上多路复用。

注:如涉及作品版权问题,请联系删除。

-

国芯思辰| 基于SC1467(替代AD7606)的同步多通道语音采集系统设计2023-08-03 1954

-

国芯思辰|多模式数字接收机可使用双通道SC1252,兼容AD9251BCPZ2023-07-05 1349

-

国芯思辰 |兼容AD8009ARZ,国产SC7508可用于脉冲信号放大器2023-06-09 1857

-

国芯思辰|兼容AD9245BCPZ,国产SC1246助力FFT式频谱仪信号处理2023-06-07 1640

-

国芯思辰|可替代英飞凌、安森美,国产碳化硅用于新能源充电桩2023-06-05 1639

-

国芯思辰 |替代AD7606,国产16位ADC SC1467在智能电网中的应用2023-06-02 2984

-

国芯思辰 |替代AD811JRZ,国产SC7301用于视频线路驱动器2023-05-30 1824

-

国芯思辰 |替代AD7173,高集成度ADC SC1644可用于地震勘测仪器2023-05-24 1383

-

国芯思辰 | 模数转换器SC1226兼容AD9235BCPZ在超声检测中的应用2023-05-15 1425

-

国芯思辰 | SC1083可替代AD7822BRUZ用于道路车辆的信息采集2023-02-27 1446

-

国芯思辰 | 双通道12位ADC SC1232可用于光纤测试仪2023-02-07 1612

-

国芯思辰 | 200kADC SC1463可替代AD7606用于电力监控系统中2023-01-11 1732

-

芯炽双通道12位ADC SC1232兼容AD92312022-09-22 610

全部0条评论

快来发表一下你的评论吧 !