verilog/systemverilog中隐藏的初始化说明

电子说

描述

在Verilog和SystemVerilog中经常需要在使用变量或者线网之前,期望变量和线网有对应的初始值,为此经常会在过程块或者连续赋值语句中对相关变量或者线网进行初始化,这样的初始化我们称之为“显式初始化”,其实除了这种初始化操作方式之外,也有人会在变量和线网声明的同时进行初始化,这种初始化方式成为“隐式初始化”,只不过在使用“隐式初始化”时经常会出现一些不期望的结果,下面将通过示例对这些初始化操作进行说明。

1 线网初始化

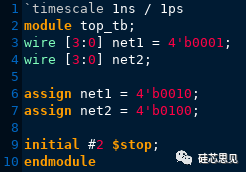

【示例】

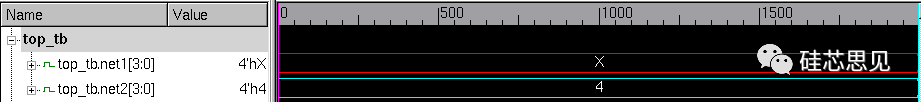

【仿真结果】

示例中,net1在声明的同时进行了赋值操作(初始化),同时在代码中通过连续赋值语句对net1又进行了赋值(与声明时初始化的值不同),此时从仿真结果可以观测到net1显示结果为不定态;net2在声明时并没有进行赋值操作,对其的赋值操作发生在连续赋值语句中,从仿真结果可以看到net2并没有出现不定态,其获得了确切的数值。

出现线网net1这种现象的主要是因为线网声明时的“初始化”是一种“隐式的连续赋值语句”,并且在仿真过程中会一直保持,当有其他语句驱动该线网时,此时相当于对该线网进行了多驱动,在仿真波形上就会表现出不定态。那么对于变量的初始化操作是否也会像示例中net1这样的情况呢?请看下例。

2 变量初始化

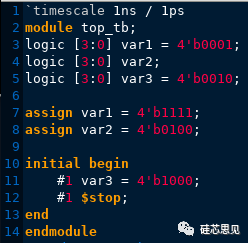

【示例】

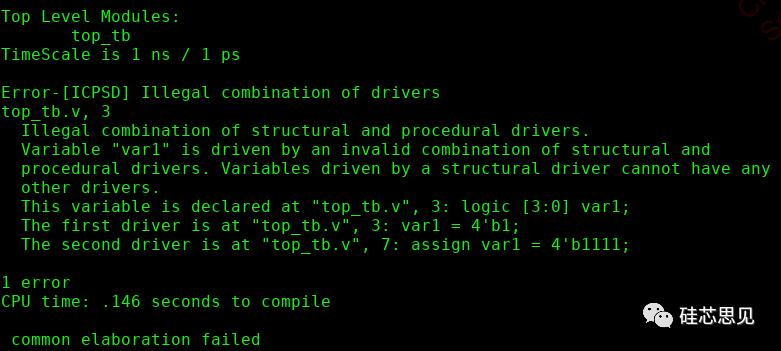

【仿真结果】

编译报错,从报错信息上可以知道,var1同时被过程块代码和结构级代码驱动,这主要是因为var1为变量,在声明时进行了初始化,同时又在连续赋值语句中也进行了赋值,从而导致了编译错误,即错误原因是变量声明时进行了初始化的话,那么该变量不能作为连续赋值语句的赋值对象进行使用,即SystemVerilog中不允许对于同一变量在连续赋值语句和过程语句中同驱动。对上述代码进行修改,如下。

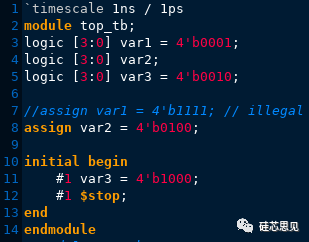

【示例】

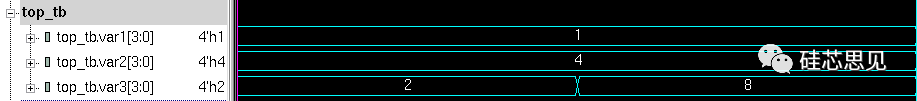

【仿真结果】

示例中,var1声明时进行了初始化,但是本例中并没有其他连续赋值语句对该变量的值进行修改驱动,所以此时var1中的值在仿真过程中一直保持,var2在声明时没有进行初始化,其值由连续赋值语句驱动为4’b0100,可见,SystemVerilog中变量可以用于连续赋值语句中,var3声明时进行了初始化,但在过程块(initial)中对var3进行了修改,此时var3的值更新为了过程块中的值,由此我们可以看出,变量在声明时的初始化先于过程块的执行,其次变量声明时的初始化并不具有持续性,会被后续的赋值操作所更新,否则就会出现多驱动情况,即并不具有“隐式连续赋值的特点”。

通过上述示例可以看到,线网声明时的初始化实际上是一种“隐式连续赋值语句”,其“初始化”具有持续性,而变量声明时的初始化会被后续的赋值操作更新,并不具有持续性,同时需要注意如果变量在声明时进行初始化,此时该变量不能同时被连续赋值语句驱动。

审核编辑:刘清

-

请问verilog如何实现SJA1000的初始化2018-11-01 4176

-

手机模块初始化向导2009-09-18 835

-

RDA1846S初始化设置2016-01-15 2314

-

UCOS_III_配置与初始化2016-12-20 1044

-

objc源码中NSObject如何进行初始化2017-09-26 899

-

SEED-DEC2812初始化函数说明2018-04-13 1120

-

uboot和内核里phy的初始化_内核里的双网络配置及phy的初始化2018-05-17 13377

-

8253初始化程序分享_8253应用案例2018-05-23 23306

-

在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决2019-08-20 1433

-

C++之初始化列表学习的总结2020-12-24 1691

-

Armlinux内核移植及系统初始化过程分析2021-04-06 965

-

VHDL和Verilog中数组定义、初始化、赋值方法2022-09-23 14188

-

如何在Segger J-Flash中设置芯片初始化序列?2022-12-12 4085

-

隐式初始化操作说明2023-07-24 1213

-

GraniStudio:初始化例程2025-08-22 1016

全部0条评论

快来发表一下你的评论吧 !