如何设计并实现一个基于FPGA的多功能信号发生器?

可编程逻辑

描述

1 系统设计

1.1 设计要求

1.1.1 设计任务

设计并实现一个基于FPGA的多功能信号发生器。

1.1.2 性能指标要求

1.能够产生两种以上输出波形(正弦波、三角波、锯齿波等)。

2.输出的波形的频率允许有多种选择。

3.输出波形的幅度在 1V~5V 范围内。

4.输出的波形能够用示波器测量。

1.2 设计思路及设计框图

1.2.1设计思路

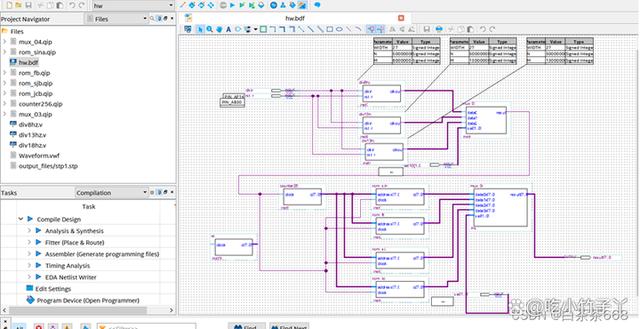

多功能信号发生器的原理框图如图所示。其中,CLKGEN是分频器,提供的50MHz的主频率进行分频,以得到满足多功能信号发生器设计需要的时钟频率。

之后是三选一 数据选择器,分别为8hz,13hz,18hz。

Lpm_counter256是参数可设置的计数器,用于产生lpm_rom256的8位地址,并从q[7..0]端输出。

lpm_rom只读存储器,用于存放多功能信号发生器的波形数据信号。

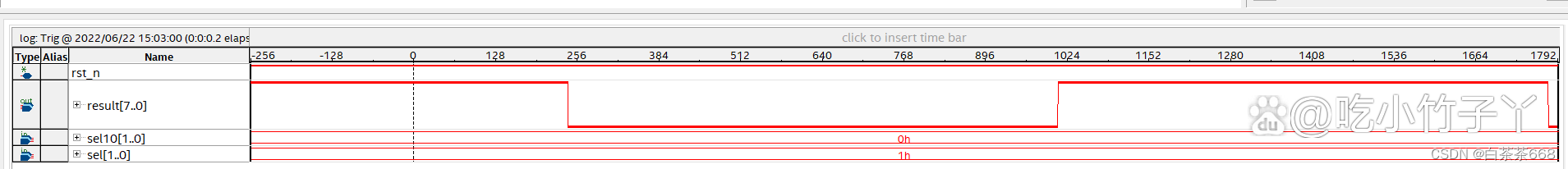

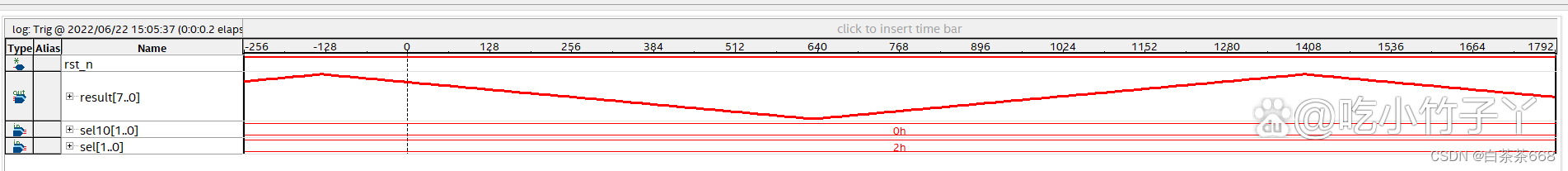

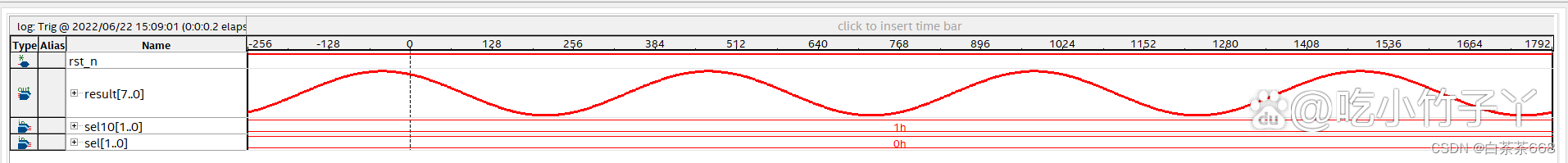

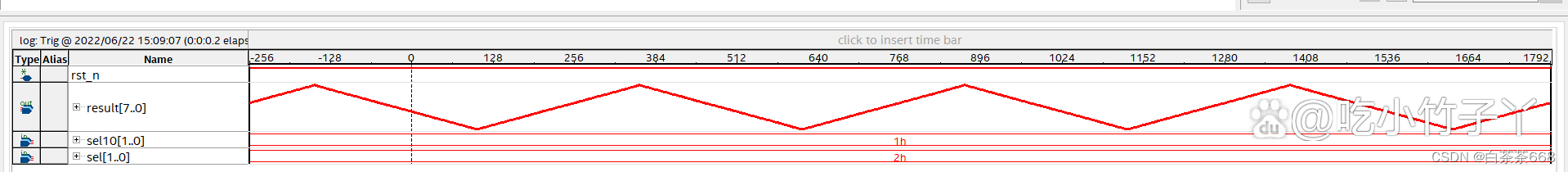

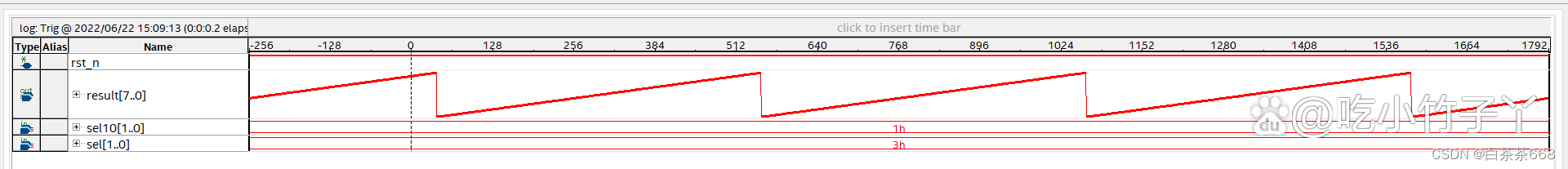

设计了三个波形为的正弦波,方波,三角波。结果由输出端q[7..0]输出到四选一选择器,由sel[1..0]选择控制。

1.2.2总体设计框图

2 各个模块程序的设计

数据选择器,分频器程序见下表计数器模块:计数器的元件生成时,首先在执行File然后New,打开一个分频器计数器锯齿波正弦波三角波方波输出波形选择器新的模块或者原理图文件编辑窗口,双击窗口并选择libraries栏中的选着ari themtic的lpm couter(计数器) lpm元件,之后点击ok并在弹出窗口中完成对参数的设置之后就可得到一个计数器元件。波形 ROM模块:为了将数据装入ROM中,在加入并设置ROM之前,应首先新建一个Memory initial izationfile文件,并设置波形最后保存后缀为,mif,生成的存储器初值设定文件保存在工程的目录中,完成存储器初始值设定后,就可以加入波形只读存储器ROM,在library中选着storage中的lpm rom即只读存储器ROM的lpm元件,输出位为8位,字数是256,采用但时钟控制方式。由于我的设计出的波形有四种,所以我要加的ROM有四个元件,他们分别输出锯齿波,方波,正弦波还有三角波,生成四个元件后,波形ROM模块就完成了。

3 调试过程

在QuartusII中打开工程,连接好试验箱和示波器,编译成功后将程序烧录到硬件中,并将硬件中的输出波形端与波形发生器相连,最后在硬件中拨动相应的开关,观察波形发生器的波形,对波形进行来回测试,即可得出结果。

4 功能测试

4.1 测试仪器与设备

笔记本,EDA试验箱。

4.2 性能指标测试

能产生四种波形且频率可调。

4.3 误差分析

附录

附录1:仿真波形图(部分模块)

部分程序清单:

分频器:

module div5hz #(

parameter WIDTH=27,

parameter N=50_000_000, //开发板上的时钟MHz

parameter M=5_000_000 //待分频的频率

)

(clkin,clkout,rst_n); //0.1S->10Hz

input clkin,rst_n;

output reg clkout;

reg[WIDTH-1:0] cnt;

always @(posedge clkin,negedge rst_n) //50_000_000MHz

begin //1s->1Hz 50_000_000/1=50_000_000/2=25_000_000

if(!rst_n) cnt=0;

else if(cnt

else cnt=0;

end

always @(posedge clkin,negedge rst_n)

begin

if(!rst_n) clkout=0;

else if(cnt==N/(2*M)-1) clkout=~clkout;

else clkout=clkout;

end

endmodule

数据选择器:

`timescale 1 ps / 1 ps

// synopsys translate_on

module mux_04 (

data0x,

data1x,

data2x,

data3x,

output [7:0] result;

wire [7:0] sub_wire5;

wire [7:0] sub_wire4 = data3x[7:0];

wire [7:0] sub_wire3 = data2x[7:0];

wire [7:0] sub_wire2 = data1x[7:0];

wire [7:0] sub_wire0 = data0x[7:0];

wire [31:0] sub_wire1 = {sub_wire4, sub_wire3, sub_wire2, sub_wire0};

wire [7:0] result = sub_wire5[7:0];

-

信号发生器如何输出直流信号?2024-05-20 5058

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 950

-

EDA程序设计之多功能信号发生器的设计2023-08-22 528

-

DG4000系列多功能信号发生器介绍2023-03-02 2039

-

如何使用FPGA实现多功能图像目标发生器的设计与实现2021-01-26 1107

-

以FPGA芯片为载体设计一个多功能信号发生器2018-10-14 7451

-

基于fpga实现信号发生器2018-04-20 1641

-

一种电路简单、成本低廉,简易多功能信号发生器2018-02-26 35012

-

基于FPGA的DDS信号发生器设计方案解析2017-12-04 2263

-

基于CPLD和单片机的多功能信号发生器2016-08-25 2225

-

基于FPGA的正弦信号发生器2015-10-30 698

-

基于FPGA的信号发生器设计2011-09-26 9299

-

基于FPGA LPM多功能信号发生器设计2011-08-15 1003

-

基于FPGA的多功能图像目标发生器的设计与实现2009-09-02 575

全部0条评论

快来发表一下你的评论吧 !