异步FIFO-格雷码

描述

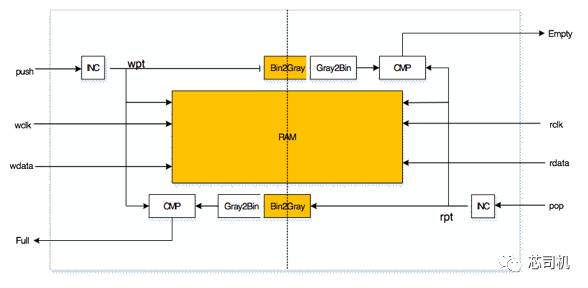

异步FIFO常用于跨时钟域之间的数据传输,其可以实现数据的存储,也可以处理异步时钟数据传输的亚稳态问题。异步FIFO的设计其关键点:通过格雷码对内部读写指针进行编码,然后比较产生空满标志,以维护FIFO的正常工作。

很多人在面试时被问到为什么异步FIFO中需要用到格雷码,可能大部分的答案是格雷码可以消除亚稳态。这种回答比较模糊,今天我们就针对这个来深入探讨一下。如下图所示:

Push信息产生的连续写指针wpt, 通过同步后,在rclk域与rpt进行比较,以产生rclk域的Empty信号。Empty信号用于控制读操作,以避免在FIFO为空时仍然进行读操作而导致的错误,并影响后续所有的FIFO读操作。

Pop 信息产生的连续读指针rpt, 通过同步后,在wclk域与wpt进行比较,以产生wclk域的Full信号。Full信号用于控制写操作,以避免在FIFO为满时仍然进行写操作而导致的错误,并影响后续的所有的FIFO写操作。

异步时钟产生的亚稳态发生在不同时钟域信号wpt和rpt的比较上。对于多bit的读写指针信号,在跨时钟域传输时会存在bit之前不同延时导致的毛刺,比如写地址在从0111到1000转换时4条地址线都会跳变,这样在写地址同步到读时钟域后得到的写地址可能是0000-1111的某个值,因此本来wpt = rpt的情况变成了wpt > rpt的情况,本来应该出现空状态,因为亚稳态导致未被发现,读操作继续进行,从而影响了整个FIFO的功能。

我们知道,格雷码编码的连续数值之间只有1bit会发生变化,这种特性其实不能消除异步时钟数据传输出现的亚稳态。假设格雷码编码的写地址从001(2)-> 011(3),读时钟域同步出错,写地址为001->001,也就是地址没有跳变,此时用这个错误的写地址与读地址进行比较,出现虚假的空标志,但这种虚空只是提前阻止了后续的读操作,不会发生读空的情况,因此不会影响后续的操作及整个FIFO的功能。同样对于读地址同步到写时钟域时也会出现虚满的情况,这种虚空和虚满,不会影响FIFO的功能,因此gray码保证的是在出现亚稳态的情形下,FIFO依然能够正常的工作。

-

异步FIFO的VHDL设计2010-07-16 824

-

异步FIFO设计之格雷码2023-11-01 2810

-

详细讨论异步FIFO的具体实现???2017-05-19 7437

-

异步FIFO用格雷码的原因有哪些2021-08-04 5361

全部0条评论

快来发表一下你的评论吧 !