如何简化光刻胶图形化过程呢?

描述

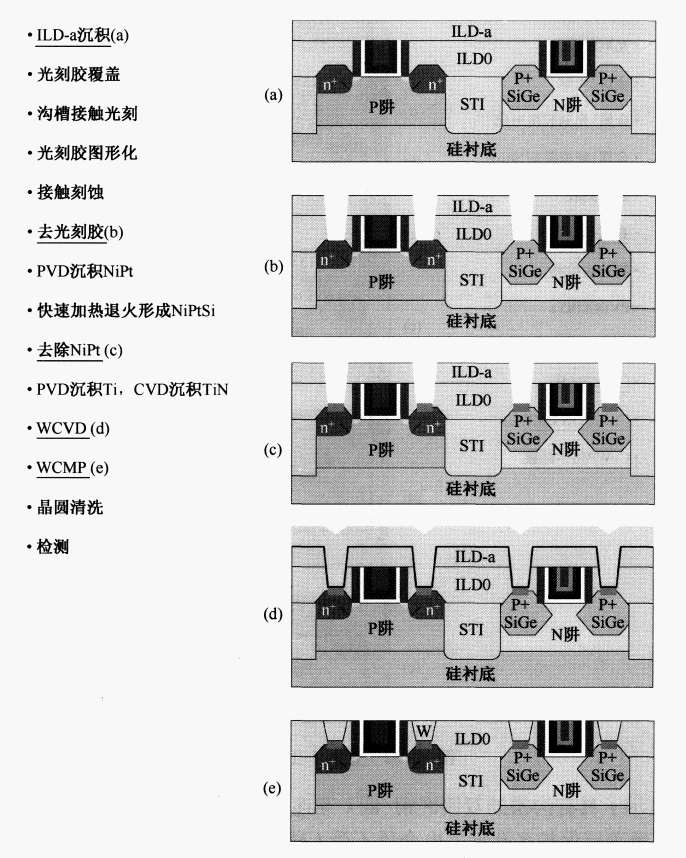

掺杂少量铂元素的镍硅化物的稳定性也不尽相同,还与物质的具体结构有关,举个例子来说,NiPtSi,比NiSi要稳定。

填充了接触沟槽的钨被研磨到金属栅极的同一平面,如下图e)所示。

由于接触沟槽只与凸起的源/漏极接触,所以接触沟槽深度很浅,这样使得过刻蚀的控制简单。

从版图的角度考虑,代替了圆形和椭圆形接触孔的沟槽式接触,简化了光刻胶图形化过程。

但是一项技术的改革往往会带来一些新的问题,比如说,这会在接触刻蚀中,过刻蚀到STI氧化层而导致W尖刺问题。

由于钨栓塞的长度显著缩短,所以栓塞的电阻大大降低(因为电阻的值与长度为正比关系)。

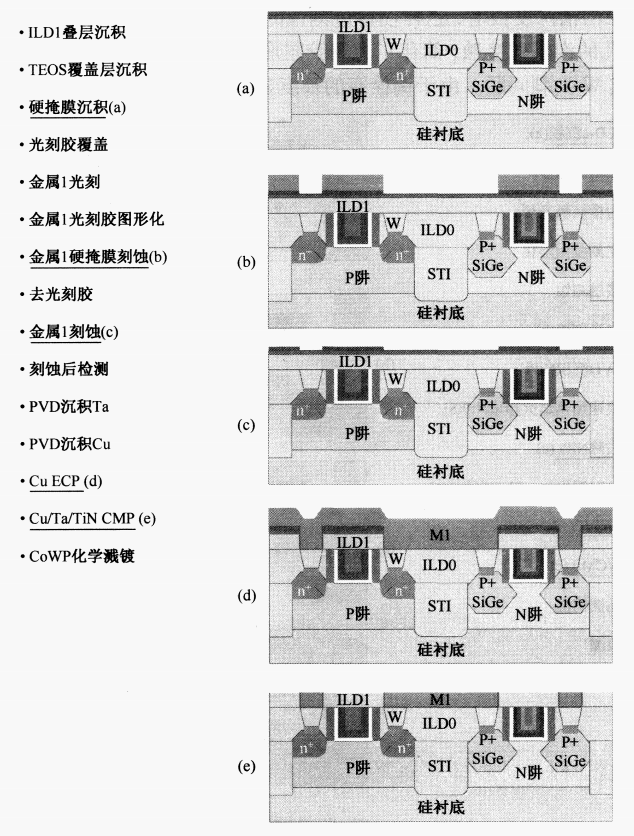

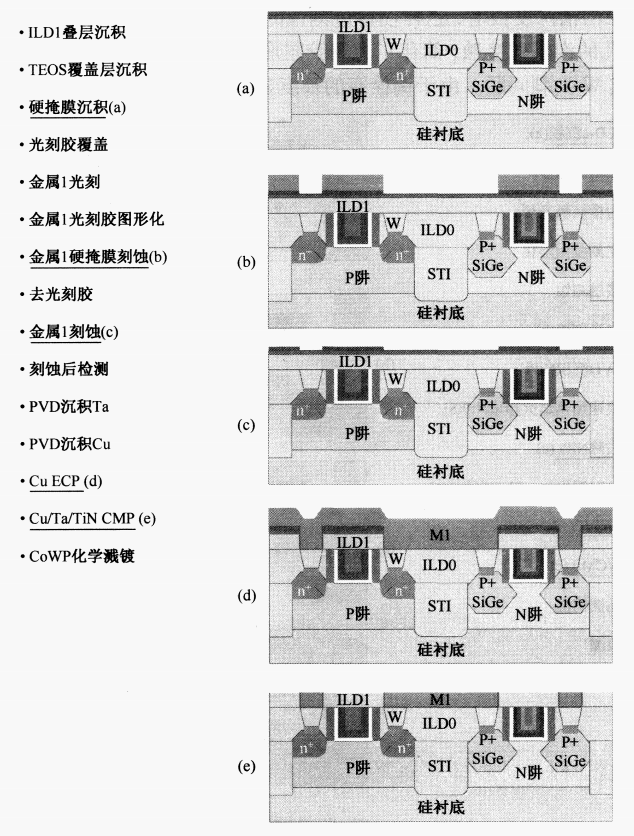

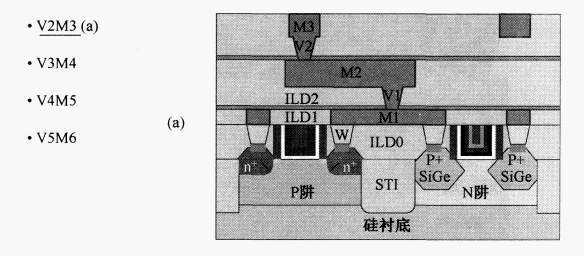

在下面的结构图中显示了金属1(M1)的形成工艺过程。

在这个过程当中,该工艺使用了覆盖在TEOS上的硬掩膜TiN保护了多孔低h介质不受光刻胶去除工艺过程的损伤。

多孔低k电介质的化值(2.2〜2.5)通常比碳硅酸盐玻璃的么值(CSG,k为2.7~2.9)低。

多孔低k电介质可以通过PECVD掺碳氧化硅电介质形成,通过将掺杂的浓度进行相应的精确控制,可以保证其中含有小于2nm的孔和高达40%的孔隙度。这些是在CVD时通过在气流中加入致孔剂实现的。

CVD预沉积,可以是三甲基硅烷或四甲基硅烷,致孔剂可以是冰片烯或a-松油烯。

钽阻挡层和铜籽晶层通过具有金属离化等离子体PVD工艺获得。

由于铜的沉积量非常大,所以传统的方法已经不再适用了,所以大量的铜沉积利用化学电镀(ECP)工艺。

在经过铜退火工艺后,利用金属CMP去除不需要的铜、钽阻挡层和TiN硬掩膜CMP研磨停止于TEOS覆盖层,这样可以保护多孔低k电介质不受CMP浆料的污染。

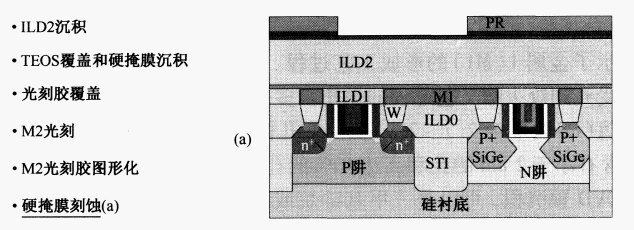

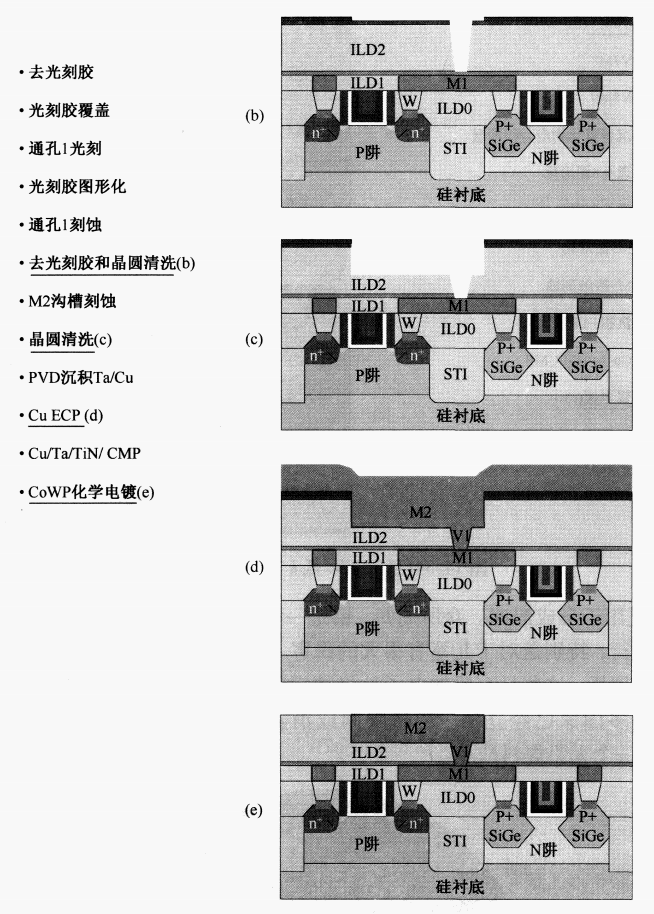

下图显示了具有沟槽的双镶嵌铜/低k互连工艺。

通常金属硬掩膜TiN、TEOSPECVD氧化物或TEOS覆盖层保护多孔低k电介质不受CMP浆料的污染。

因为这样相当于在多孔低k电介质的外表面加上了几层的保护膜,今儿产生了一个相对稳定的小环境。

并且在此基础上,可以利用自对准CoWP化学电镀的技术来防止铜的扩散并提高电迁移抵抗能力,通过这种技术从而提高了IC芯片的可靠性。

下图显示了从M3金属层(见下图(a))到M9金属层(见下图(c))的铜/低k互连工艺过程。该过程基本上是下图所示的通孔工艺过程的重复。

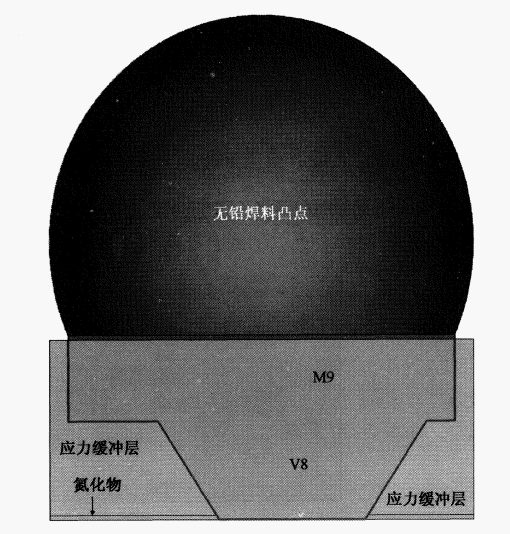

铅(Pb)广泛用于形成焊球。众所周知,铅是一种污染物,可以影响心脏、骨骼、肠、肾和神经系统的正常运行,特别是对于儿童有很大的伤害。

大量使用IC芯片的过时电子仪器形成每年万吨级的电子垃圾,这些具有铅的电子垃圾填埋给环境污染带来潜在风险,因此,像日本、欧洲和中国等许多国家已经立法,严格限制或消除铅在半导体和所有电子行业中的使用。下图显示了一个无铅焊料凸点。

审核编辑:刘清

-

Futurrex高端光刻胶2010-04-21 3988

-

光刻胶残留要怎么解决?2016-11-29 31542

-

Microchem SU-8光刻胶 2000系列2018-07-04 4814

-

光刻胶2018-07-12 2998

-

光刻胶在集成电路制造中的应用2018-08-23 7426

-

光刻胶有什么分类?生产流程是什么?2019-11-07 4377

-

光刻胶的原理和正负光刻胶的主要组分是什么2022-10-21 24493

-

光刻胶黏度如何测量?光刻胶需要稀释吗?2023-11-13 3227

-

匀胶速度影响光刻胶的哪些性质?2023-12-15 4469

-

关于光刻胶的关键参数介绍2024-03-20 5886

-

光刻胶的保存和老化失效2024-07-08 4245

-

光刻胶的图形反转工艺2024-07-09 2419

-

光刻胶的使用过程与原理2024-10-31 3337

-

光刻胶剥离液及其制备方法及白光干涉仪在光刻图形的测量2025-05-29 1524

-

减少光刻胶剥离工艺对器件性能影响的方法及白光干涉仪在光刻图形的测量2025-06-14 1052

全部0条评论

快来发表一下你的评论吧 !