数字前中后端都不得不熟练的clock switch设计

描述

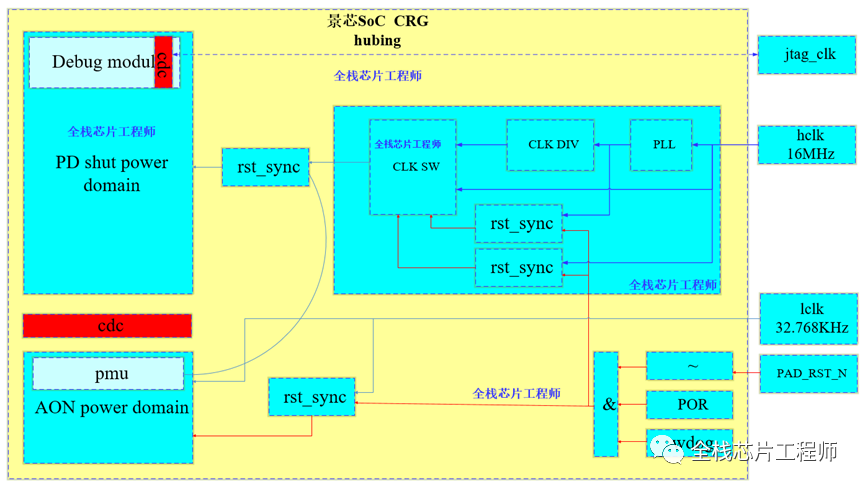

本章节讲解数字前中后端都不得不熟练的clock switch设计。

芯片运行过程中需要时钟切换时,要考虑到是否会产生glitch,小小的glitch有可能导致电路运行的错误。所以时钟切换时需要特别的处理。

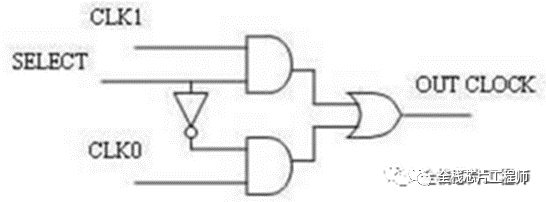

直接使用MUX进行时钟切换或者采用如下电路结构进行时钟切换:

assign outclock = select? clk1: clk0;assignoutclock= (clk1 & select) | (~select & clk0);

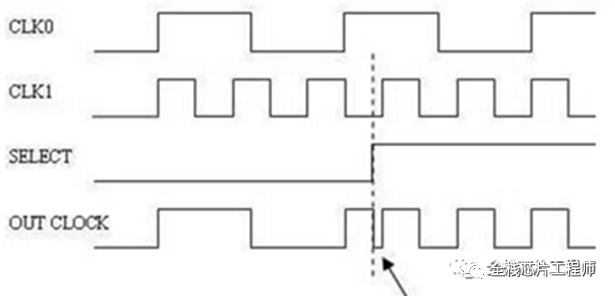

两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。

为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:

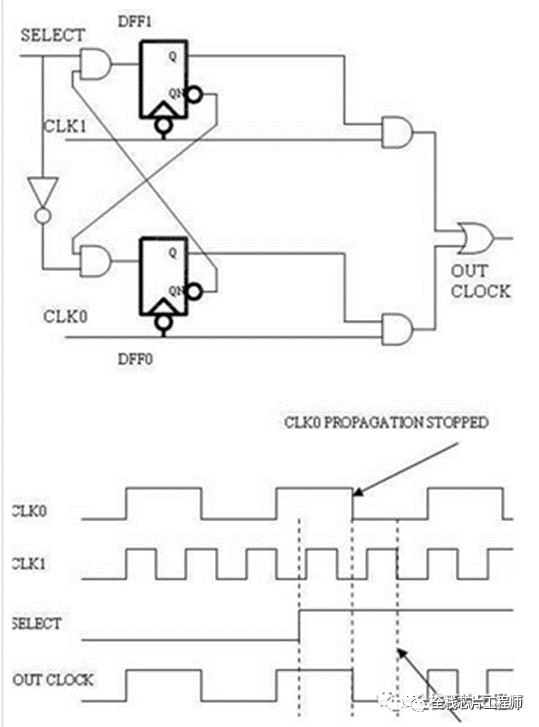

CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系

插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。

如下所示:从下图第二个箭头开始,实际发生时钟切换。

那么,请问CLK0与CLK1为异步时钟时,电路如何设计?

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

不论小白还是大佬,这篇PCB晶振设计都不得不看2022-12-06 1386

-

不得不收藏的PCB的Checklist!2022-02-09 1078

-

如何去实现一种数字前端的设计?包括哪些步骤?2021-06-18 1501

-

设计PCB不得不关注的重点2021-04-21 1592

-

在main函数运行之前,你不得不知的那些事2021-04-20 2512

-

总结使用 Vim 的过程中不得不了解的一些指令和注意事项2017-12-27 5518

-

死磕物联网低功耗设计,BOM中不得不知的五条“军规”2017-08-25 8750

-

Android系统开发环境搭建不得不说的的那些事(二)2016-07-30 5120

-

不得不看的蓝牙4.0组网实验教程2016-02-26 5650

-

智能终端战役打响 综合布线不得不动摇2014-04-04 1094

-

理解总线工作不得不看的几个经典电路!!!2013-05-19 10870

-

模电设计不得不看——模拟电路设计原则2012-08-17 7618

-

有关充电电池不得不说的几个问题2009-11-05 1438

-

笔记本电池不得不说的秘密2009-10-28 661

全部0条评论

快来发表一下你的评论吧 !