高速互连IBIS仿真模型

PCB设计

描述

IBIS(Input/Output Buffer Information Specification)模型是一种定义输入/输出缓冲器(I/O Buffer)V-I和v-r响应的一种模型,目的是提供一种集成电路制造商→EDA软件厂商→设计工程师之间相互交换电子元件仿真数据的标准格式。IBIS的版本发布情况为:1993年4月首次推出Version1.0版;1994年6月发布了Version2.0版;1997年6月发布了Version3.0版,并于同年9月被接纳为IEC 62012-1标准;1999年1月推出了Version3.2版,该版本为目前广泛使用的版本;而目前的版本为2006年6月推出的Version4.2版。

IBIS模型属于一种行为模型,它不是从要仿真的元件的结构出发进行定义的,而是从元件的行为出发进行定义的,描述了器件在特定负载、特定封装下的输入/输出行为,而不是实际的电气组成。IBIS模型主要用于板极的系统仿真,可以帮助设计者在存在高速设计规则约束的设计中获取准确的信息以进行分析和计算。由于它不涉及芯片内部的结构信息,因此得到了众多厂商的支持。

IBIS本身只是—种文件格式,它说明在标准的IBIS文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些参数如何使用,这些参数需要由支持IBIS模型的仿真工具来读取。

一个IBIS文件包括了从行为上模拟一个器件或一组器件的所有输入、输出和“I/O”等类型缓冲器所需要的数据,它以ASCII的格式保存。IBIS文件主要由以下3个部分组成。

· 文件头:这部分包含关于IBIS版本、文件名、版权等信启、:

· 器件描述:包含器件名称、制造商、封装和引脚等信思:

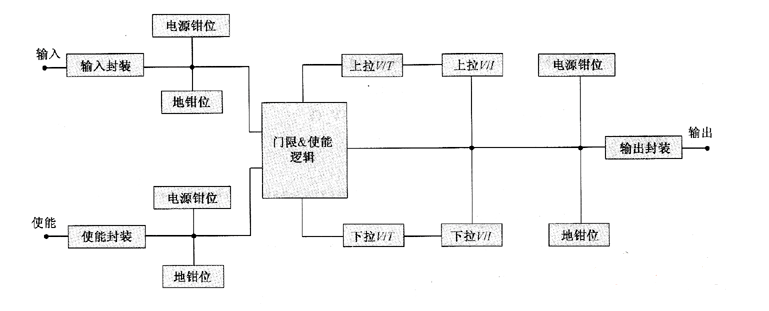

· 模型描述:这部分定义了模型对应的缓冲器类型:门限电平;描述Pulldown、Pullup、 Power_Clamp、Gnd_Clamp的IlV数据表;Ramp数据;描述波形上升/下降沿的VIT

数据表等。不同类型的缓冲器包含的数据有所不同,如图所示为IBIS模型的一般结构。

图 IBIS模型的一般结构

-

请问如何获得AD8000的IBIS模型?2025-03-24 2110

-

CH569/565能提供仿真文件IBIS模型吗?2022-06-15 836

-

请问ADP2300的IBIS模型在哪里能够得到2018-10-25 2374

-

Hyperlynx仿真:Xilinx官网下的Ibis模型里面怎么没有引脚的编号2018-10-15 4676

-

高速互连IBIS仿真模型概述2018-09-03 2976

-

高速互连SPICE仿真模型完成多类电路分析2018-08-31 2441

-

AM3892什么时候能提供IBIS仿真模型2018-05-14 2111

-

跪求ibis仿真模型2017-12-06 4905

-

请问有人知道IBIS模型怎么使用吗?2017-02-13 16234

-

IBIS模型库是怎么找到的?2015-01-12 13110

-

allegro布局仿真求助:布局仿真的IBIS模型去哪个网站下载2014-03-25 6440

-

IBIS模型2013-11-06 2892

-

什么是IBIS模型?以及IBIS模型的仿真及优缺点2009-03-20 5886

-

ibis模型理解说明2008-07-30 2054

全部0条评论

快来发表一下你的评论吧 !