FPGA的BRAM资源使用优化策略

描述

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

一般建议BRAM和LUT资源的消耗不要超过80%,当然高端一点的FPGA芯片也可以放宽到90%,超过这个限制,可能就会出现时序违例较严重的情况,导致上板运行出现异常的情况。

今天分享一下BRAM资源使用优化策略,以Vivado的 Block Memory Generator为例 。

1、Distribute BRAM或URAM 替代BRAM

存储深度和宽度较小,且LUT资源或URAM有富裕,可以用“Distribute BRAM”或“URAM”来替代。

这里需要注意使用的FPGA芯片型号,是否带URAM资源。

- (* ram_style = "block" *)表示用Block RAM实现

- (* ram_style = "reg" *)表示用寄存器实现

- (* ram_style = "distributed" *)表示用分布式 RAM实现

- (* ram_style = "uram" *)表示用uram实现

这里给出代码示例:

// FPGA 双口 RAM

module dual_port_ram(

input clk,

input [7:0] data_in,

input [5:0] wr_addr,

input wr_en,

input [5:0] rd_addr,

output reg [7:0] data_out

);

// 声明双口 RAM 存储器

(* ram_style = "block" *)reg [7:0] ram[63:0];

// 时钟上升沿写入

always @(posedge clk) begin

if (wr_en)

ram[wr_addr] <= data_in;

end

// 读取;

always @(posedge clk) begin

data_out <= ram[rd_addr];

end

endmodule

2、双口ROM替代单口ROM

如果工程中,有两个以上的ROM或RAM使用的是相同的数据,可以使用双口替代单口模式,资源消耗是一样的,这样就可以节省一个或多个ROM IP。

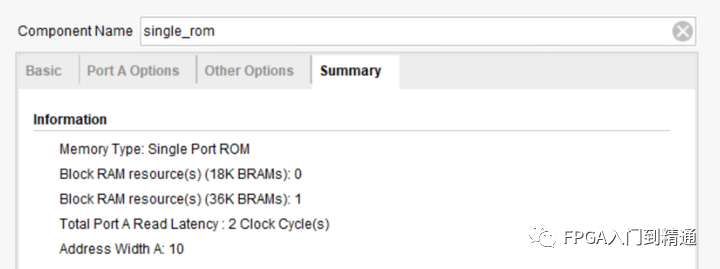

这里对比一下“数据宽度为32,存储深度为1024”的单口和双口模式下的资源消耗。

3、合理的数据宽度和深度设置

要想FPGA BRAM资源消耗优化,更关键的是优化FPGA工程的缓存大小设计,计算理论上缓存数据的位宽和最大深度,选择出合适的参数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HLS设计中的BRAM使用优势2026-01-28 394

-

基于FPGA设计的BRAM内部结构2024-04-25 1266

-

FPGA设计中BRAM的知识科普2023-08-15 8269

-

URAM和BRAM有哪些区别2022-07-25 7837

-

FPGA设计应用及优化策略有哪些?2021-04-15 1841

-

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互2021-02-22 10079

-

URAM和BRAM有什么区别2021-01-27 2304

-

时序分析的优化策略详细说明2021-01-14 1577

-

FPGA布局及资源优化2021-01-07 6009

-

使用FPGA调用RAM资源的详细说明2020-12-30 2125

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 13598

-

【InTime试用体验】使用简易、策略选择精确度高的一款时序优化软件2017-07-05 9901

-

FPGA资源优化方法2015-04-04 6308

全部0条评论

快来发表一下你的评论吧 !