FPGA到底是什么 FPGA的构成要素 FPGA怎么选型

可编程逻辑

描述

理解FPGA内部结构所需的基础知识

- 逻辑电路基础

- 逻辑/布尔代数

- 真值表

- 组合逻辑电路

- 时序逻辑电路

- 同步电路基础

- FF(触发器)

- 建立时间保持时间

- 时序分析(STA)

- 单相时钟同步电路

注:

1、fpga是一种可通过重新编程来实现用户所需要的逻辑电路的半导体器件。

2、构成数字逻辑最重要的部件是组合逻辑和时序逻辑,所以作为实现数字逻辑功能的FPGA的最重要组成部分就是组合逻辑和时序逻辑电路。

3、Flip Flop是一种只能存储1个二进制位的存储单元,在时钟边沿将输入信号送至输出端。

4、为了正确的从输入读取数据,并正确的将数据输出,FPGA内所有FF都要遵守建立和保持时间(理解D触发器的内部电路可以更好地理解建立时间和保持时间)。

5、FPGA的性能评估主要采用静态时序分析(STA),时序分析必须检查所有路径上逻辑延迟和布线延迟的时序裕量,确保满足建立和保持时间约束。

6、单相时钟同步:同一时钟、同一边沿、同步动作的电路类型

有以上数字电路基础,对理解FPGA底层结构很有帮助,不理解也没有太大关系,FPGA开发不需要理解其底层详细架构,但肯定有助于理解和优化电路设计。

FPGA到底是什么

FPGA(Field Programmable Gate Array):

- 门阵列

- 可”编程”

- 现场

FPGA:作为一种包含大量逻辑门阵列的芯片,可以在使用现场通过编程改变自身的硬件逻辑,并在理论上可以实现任何数字电路的功能。

注释:

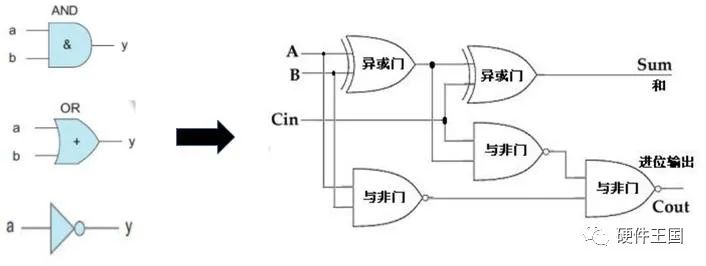

1、逻辑门是数字电路的基本单元。

2、逻辑门进行排列组合-->编程改变其逻辑结构-->不同功能的芯片。

3、FPGA可以通过在现场进行重新配置来实现逻辑的修改、优化和调整,而无需更改硬件电路设计。这种灵活性使得FPGA在各种应用中具有广泛的应用前景,尤其是在需要快速开发和验证新硬件系统的应用场景中。

如上图所示,最基本的逻辑门经过组合后构成一个带进位的加法器。

先抽象理解FPGA可构成任何数字电路,基于什么原理构成,请继续学习下文。

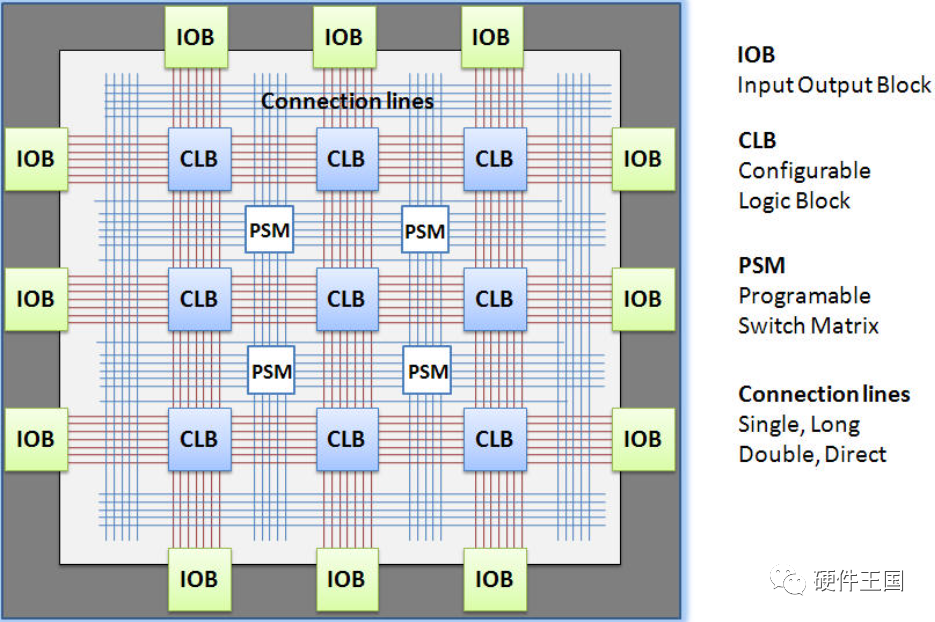

FPGA的构成要素

- 逻辑要素(可配置逻辑块-CLB)

- 输入/输出要素(IO块)

- 布线要素(开关块、连接块、布线通道)

- 其他要素(存储器块、PLL等硬核)

岛形结构

注:

1、前三种为主要的三大要素。

2、逻辑块利用查找表和数据选择器实现任意逻辑函数,不同的FPGA供应商叫法不同,xilinx:CLB,altera:LAB。(下文有详细介绍)。

3、IO块负责器件的I/O引脚与逻辑块之间的接口部分(除专用电源、时钟外)。

4、布线结构类型主流岛型结构,开关块位于横向和纵向布线通道的交叉处,通过可编程开关来控制布线路径。连接块是连接布线通道和逻辑块的输入/输出。需要对开关数量和连线自由度进行权衡。

5、其他要素主要包含FPGA内部嵌入的各种硬核资源。

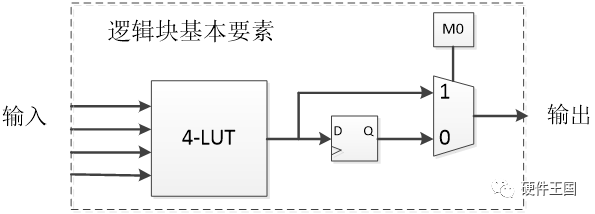

FPGA—逻辑块之基本要素

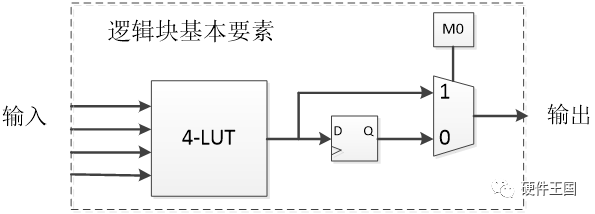

可配置逻辑块:xilinx称为CLB(configurable logic block),Altera称为LAB(logic array block), CLB是FPGA内的基本逻辑单元,是实现FPGA逻辑的基础。主要包括以下基本要素:

- 实现组合逻辑电路的查找表

- 实现时序电路的触发器

- 数据选择器在存储单元M0的控制下决定直接输出查找表的值还是输出触发器中存的值

注:

1、查找表:实现组合逻辑。

2、FPGA中多使用4/6输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM(LUT详细说明见下文)

3、当用户描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。(当看完下文的LUT,如果能理解本段话,说明你已经理解了FPGA的本质)

主流FPGA的逻辑块除最基本逻辑要素外,还有其他附加逻辑,比如进位、算术、移位、存储等。结构上包含多个基本逻辑要素,如7系列xilinx,一个CLB包含2个slice,一个slice包含4个LUTs。

FPGA—逻辑块之LUT

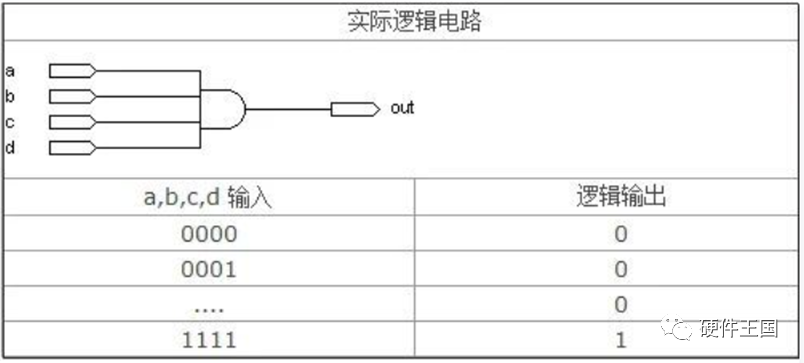

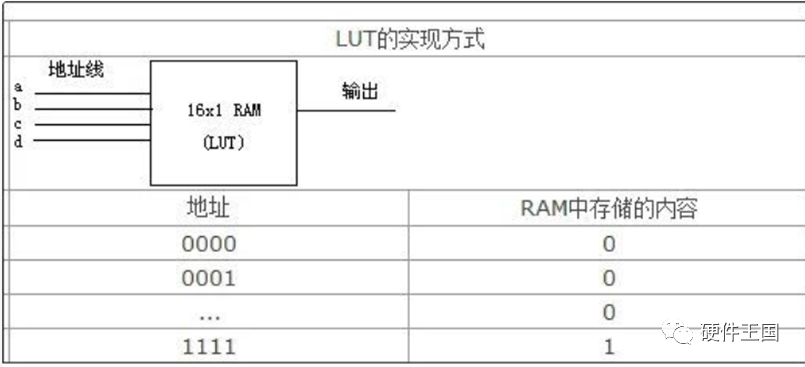

LUT(Look Up Table):通过将逻辑函数的真值表存放在少量内存单元中来实现组合逻辑电路功能的模块。也可以简单理解为实现真值表所定义的功能的电路称为查找表。LUT可以实现任意的布尔逻辑功能。

- 内存单元:主流SRAM

- 输入可看作为SRAM地址信号

- 输出可看作为该地址内存单元的1位数据

逻辑功能根据需要被重新编程写在SRAM里,从而实现不同的逻辑功能

注:

1、上图假设为一个实际4输入1输出的逻辑电路,对应LUT的实现方式。

2、FPGA中多使用4/6输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。当用户描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

3、亦可总结为:在LUT中,输入数据通过一组可编程的存储单元(通常为SRAM)进行存储,并在逻辑运算时被查找

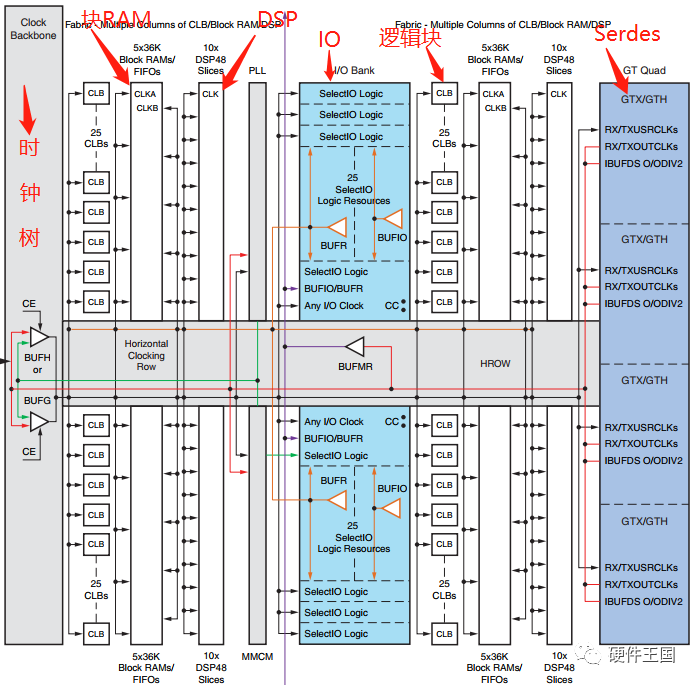

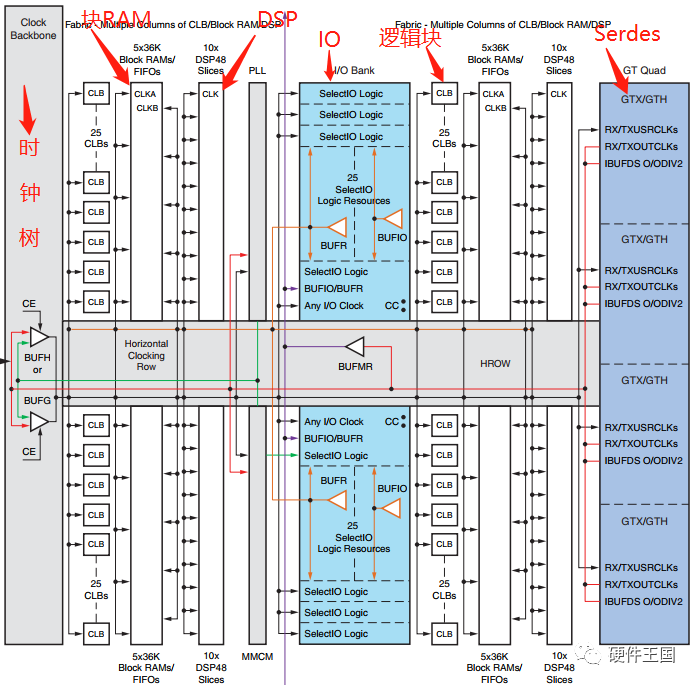

FPGA内部资源示例

- 除三大构成要素外,还有完整的时钟管理,嵌入式块RAM,内嵌的底层功能单元和专用硬件模块等。

- 主流FPGA逐渐变得越来越复杂,但仍是基于查找表技术,只是远远超出了先前版本的基本性能。

xilinx V7为例说明

注:

1、FPGA芯片内部包含多种硬核资源,这些资源可以实现各种不同的功能和任务,如上图所示:

数字信号处理 (DSP) 器件:可实现高速数字信号处理、滤波器和调制/解调器等应用。

快速片上存储器(Block RAM):可以作为存储器或FIFO使用。

数字时钟管理器(MMCM):可用于时钟的生成、延迟、相位调整和频率合成。

通用串行收发器(Serdes):用于实现高速串行通信,如PCI Express、SATA、USB3.0等。

2、随着不同用户的需求,最新工艺的变化等,FPGA芯片逐渐变得越来越复杂

FPGA—怎么设置工作状态

FPGA是由存放在片内的RAM来设置其工作状态的,因此工作时需要对片内RAM进行编程

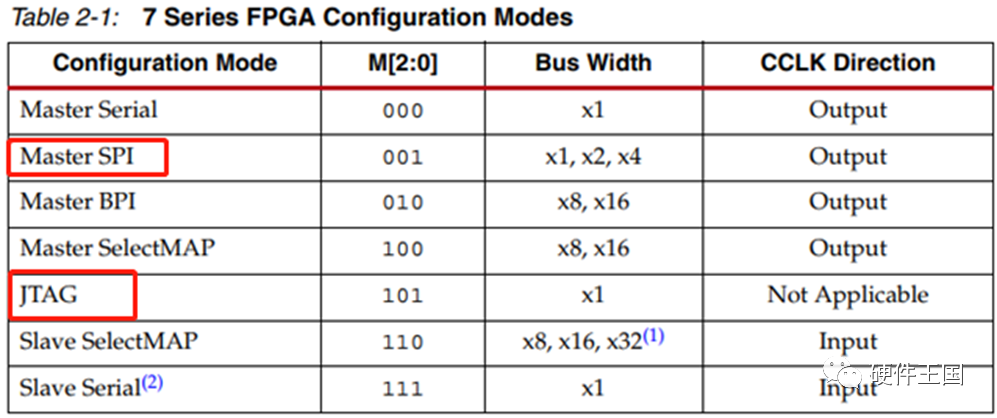

配置模式主要包含两种:

- 主模式:

- 自加载FPGA配置模式

- FPGA外部非易失性存储

- FPGA控制配置过程

以xilinx 7系列为例,SPI flash存储位流较为常用

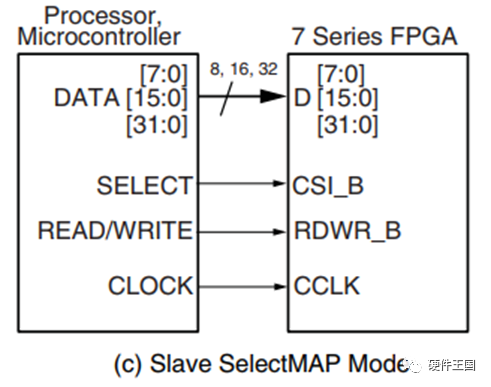

- 从模式

- 外部控制加载(处理器、MCU等)

- 位流可随意存放

外部处理器控制加载位流

注:

1、FPGA市场占有率最高的两大公司Xilinx和Altera(目前已分别被AMD和intel收购)生产的FPGA都是基于SRAM工艺的,需要在使用时外接一个片外存储器以保存程序。上电时,FPGA将外部存储器中的数据读入片内RAM,完成配置后,进入工作状态;掉电后FPGA恢复为白片,内部逻辑消失。

FPGA怎么选型

- 确定设计需求:首先需要明确设计的需求,包括设计功能、性能和时序要求等,这将对FPGA资源的选择和使用产生重要影响。

- 估算资源需求:根据设计需求,可以通过计算和仿真等手段估算所需的FPGA资源,如LUT、FF、RAM、DSP等,这些资源可以通过FPGA厂商提供的设计工具进行估算。

- 分析FPGA资源:选择合适的FPGA芯片后,需要分析FPGA资源的规格书,了解FPGA内部的硬核资源数量和性能,以及可用于自定义逻辑的逻辑单元数量等信息。

- 进行综合和布局布线:在使用FPGA设计工具进行综合和布局布线后,可以得到FPGA资源利用率的估计,以及所需资源与实际可用资源的比较,通过这个比较可以初步评估FPGA资源是否足够。

- 进行仿真和验证:在综合和布局布线后,需要进行逻辑仿真和时序验证,以确保FPGA资源的使用是正确和稳定的。

总的来说,评估FPGA资源是否足够需要考虑多个因素,包括设计需求、FPGA资源规格、综合和布局布线结果以及仿真验证等,通过这些手段可以进行初步的资源评估和调整。

-

FPGA到底是什么?FPGA为什么比GPU的延迟低?2023-01-17 2277

-

FPGA的基本构成2023-11-08 2078

-

FPGA讲解 FPGA到底是啥 FPGA里面有什么?2022-05-05 9189

-

Actel FPGA产品选型指南2010-11-17 833

-

Altera FPGA的选型及开发2012-08-15 1570

-

xilinxFPGA选型详解2018-03-15 727

-

FPGA的视频教程之Verilog模块的基本构成要素资料说明2019-03-26 1321

-

FPGA到底是什么?FPGA有哪些优势2020-01-25 6206

-

FPGA到底是什么?为什么要使用它2020-02-16 7814

-

使用FPGA设计的IO到底是什么2020-12-22 1265

-

FPGA到底是什么?FPGA的详细介绍2020-12-23 6520

-

FPGA的选型策略有哪些?2021-03-22 8369

-

FPGA到底是什么?,FPGA工程师核心竞争力是什么?2023-01-07 2623

-

FPGA是什么?2023-03-29 6092

-

FPGA/DSP/ARM选型手册2023-05-05 1087

全部0条评论

快来发表一下你的评论吧 !