基于FPGA的UDP千兆以太网光通信

描述

概述

本文介绍一个FPGA开源项目:UDP千兆以太网光通信。利用SFP接口,可以通过使用SFP转RJ45模块或者直接使用光纤进行以太网通信。

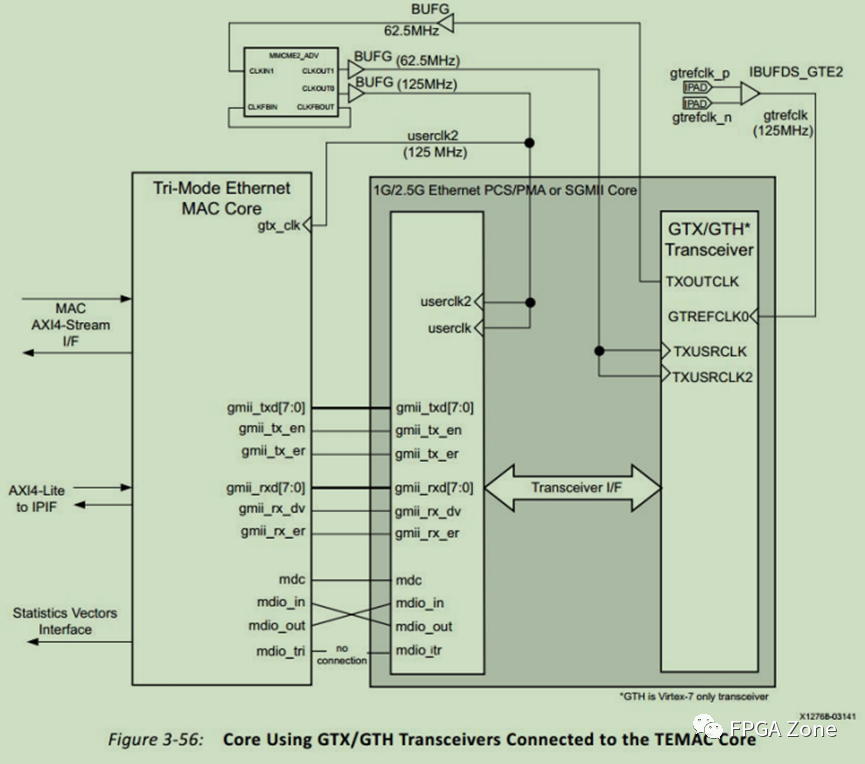

本工程主要是围绕“Tri Mode Ethernet MAC”IP核以及“1G/2.5G Ethernet PCS/PMA or SGMII”IP核建立。其中,“Tri Mode Ethernet MAC”IP作为以太网MAC,通过GMII接口与“1G/2.5G Ethernet PCS/PMA or SGMII”IP核进行核间通信。

软硬件平台

软件平台 :Vivado 2017.4;

硬件平台 :XC7Z035FFG676-2;

IP核参数配置

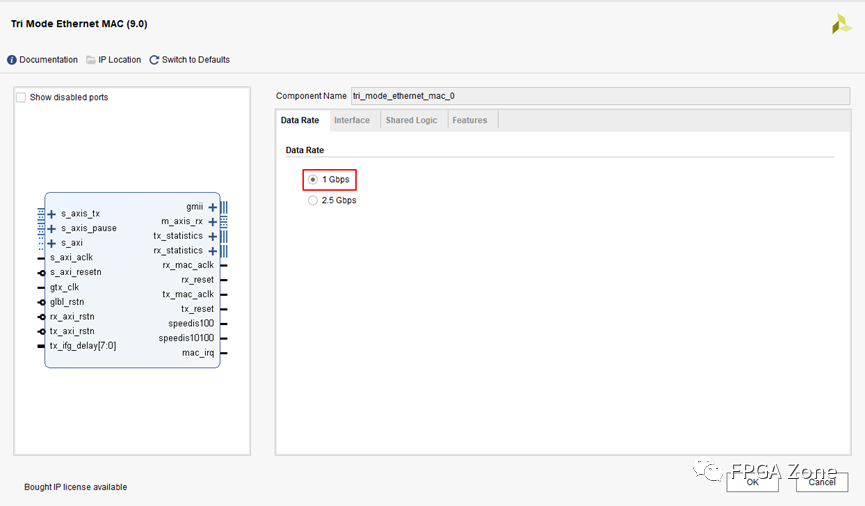

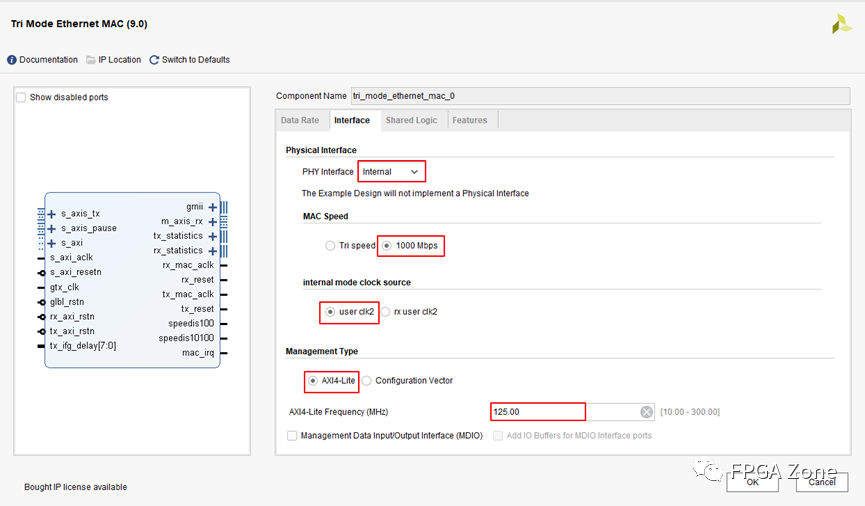

Tri Mode Ethernet MAC

- 该工程使用千兆速率,选择 1Gbps ;

- 接口选择 **Internal ** ,因为该IP核通过GMII接口与“1G/2.5G Ethernet PCS/PMA or SGMII”通信,不需要产生外部物理接口;

- MAC速率选择 1000Mbps ,与“1G/2.5G Ethernet PCS/PMA or SGMII”1000BASEX通信标准匹配;

- 内部时钟源选择1G/2.5G Ethernet PCS/PMA or SGMII IP核提供的user clk2;

- 选择 AXI-Lite 接口,对IP核参数进行配置;

- AXI-Lite接口时钟同样选择user_clk2,即 125Mhz ;

- Shared Logic与Features保持默认即可。

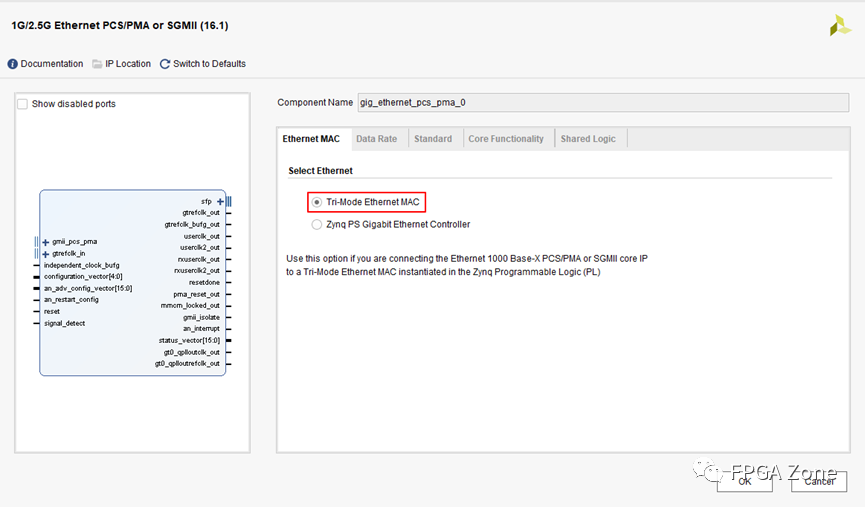

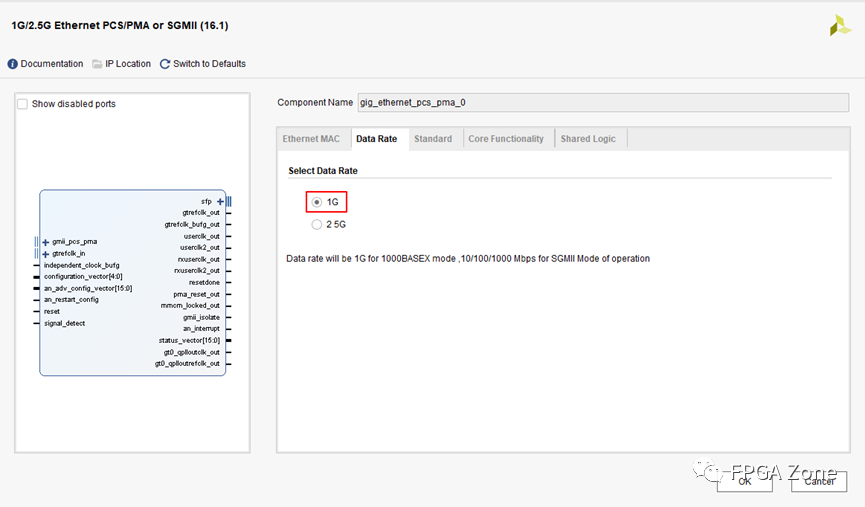

1G/2.5G Ethernet PCS/PMA or SGMII

- Ethernet MAC选择 Tri Mode Ethernet MAC ;

- 该IP核采用1000BASEX模式,因此将速度设为 1G ;

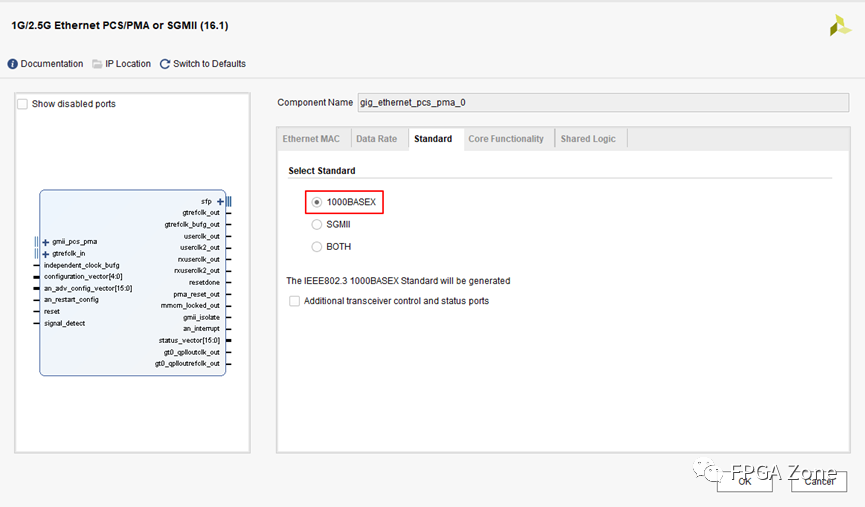

- 选择 **1000BASEX **标准;

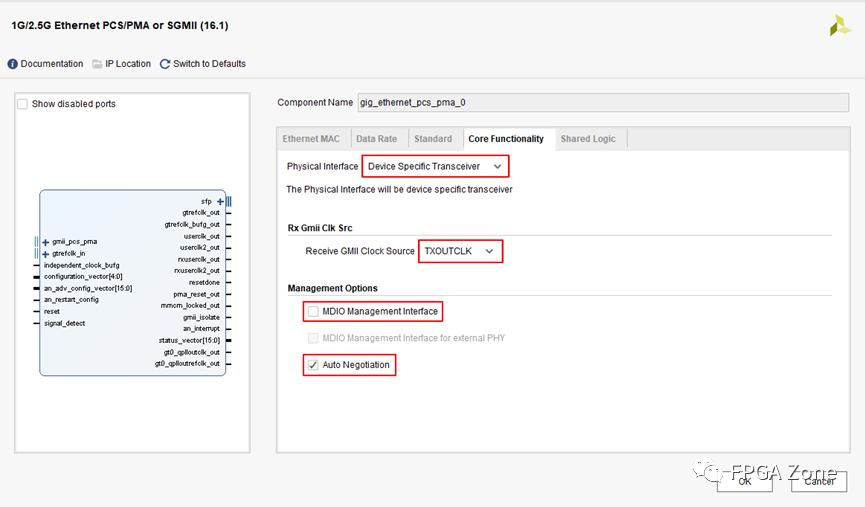

- 物理接口为 **GTX **收发器作为SFP接口;

- 时钟源选择GTX收发器的输出时钟 **TXOUTCLK ** ;

- 不使用MDIO接口配置IP核;

- 选择自协商功能;

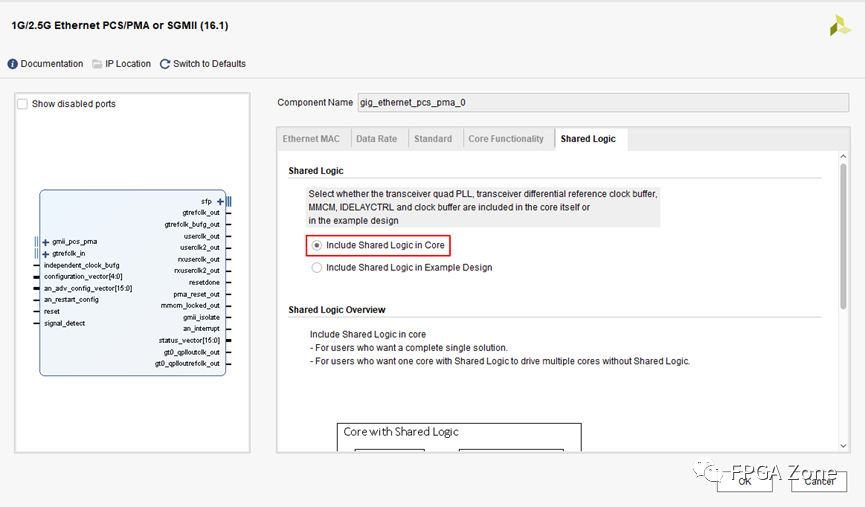

- Shared Logic选择将共享逻辑包含在IP核内;

接口互联

上述两个IP核之间通过GMII接口进行通信,Tri Mode Ethernet MAC工作时钟源采用1G/2.5G Ethernet PCS/PMA or SGMII输出的125Mhz的userclk2,GMII接口各信号与userclk2时钟同步。

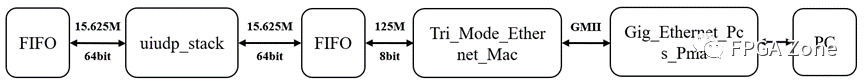

功能测试

该Vivado工程实现的功能为千兆以太网光纤数据回环传输。在电脑端通过网络调试助手向FPGA板卡发送长度小于1472字节的数据包,FPGA收到数据后解析、缓存用户数据,最后回传给电脑端,数据传输方案如下图所示:

其中uiudp_stack数据位宽为64bits,而Tri Mode Ethernet MAC数据位宽为8bits,因此二者之间需要插入FIFO进行数据位宽以及时钟域转换。

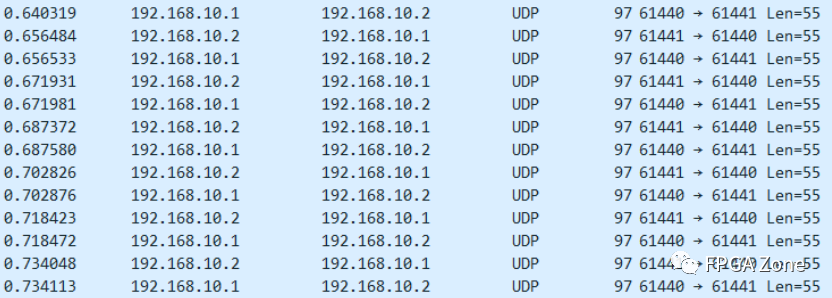

通过wireshark软件对电脑和FPGA之间传输的UDP数据包进行捕获,部分结果如下图所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于FPGA的UDP RGMII千兆以太网设计2023-09-06 5414

-

基于FPGA的UDP RGMII千兆以太网通信方案2023-09-04 3599

-

基于FPGA的UDP万兆光通信测试2023-09-01 5255

-

简谈基于FPGA的千兆以太网设计2023-06-01 1319

-

FPGA如何为以太网和千兆以太网解决低功耗问题2022-05-07 5994

-

如何快速分辨以太网与千兆以太网2022-05-06 6452

-

千兆以太网发展现状 千兆以太网技术优势2021-03-21 8883

-

如何实现以太网LED可见光通信技术的研究2020-04-08 1603

-

简谈基于FPGA的千兆以太网2018-02-03 7069

-

FPGA在光通信中的应用2016-11-05 7600

-

基于Xilinx FPGA的千兆以太网控制器的开发2015-01-23 31495

-

百兆以太网改千兆,要怎么修改程序?2013-10-03 6426

-

基于FPGA的十端口千兆以太网接口的设计与实现2009-08-29 730

全部0条评论

快来发表一下你的评论吧 !