实际底层的RAM尺寸到底是多少呢?就是32x119吗?

电子说

描述

在ASIC设计中,我们使用FIFO或者RAM的时候经常会用到校验位,例如奇偶校验或者ECC(海明码)校验,当然,也有可能不使用任何校验位。那么我们需要一个深度为32,数据位宽为119bit的ram(cfg_32x119_ram_wrapper),那么实际底层的ram尺寸到底是多少呢?就是32x119 吗?大概率不是。

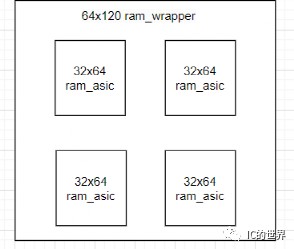

1.一个ram wrapper可能是拼接而成的

RAM的位宽和深度不是任意的,是根据设计人员的需求,然后由工具产生相应的ram。我们需要的是32x119的ram,实际分配给设计人员的可能是两个32x64的ram,深度和宽度都可能存在冗余。Ram的产生通常有两种方式,由设计人员或者中端人员提供ram信息列表。至少包含如下信息:Memory生成工具会根据实际需要的位宽,深度,读写时钟频率才进行决策,产生相应的Memory。

| RAM_NAME | RAM_TYPE | DEPTH | WIDTH | ECC/PARITY | Wclk_freq | Rdclk_req |

| afifo_16x72_wrapper | 1r1w | 16 | 72 | 1 | 1200 | 1000 |

一颗大的ram可能是有多个小的ram拼接起来的。在布局布线时,多个小的方形的ram大概率会比长条形状的ram更容易摆放(不绝对)。

2.ram/fifo 校验位需要额外的数据位宽

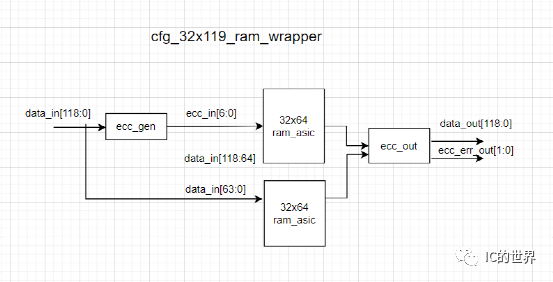

如图所示为1r1w的ram为例,cfg_32x119_ram_wrapper为verilog代码直接调用层次的ram_wrapper,表示了一个深度为32,数据位宽为119bit的ram。ram_asic.v为真实的ram IP。其中119bit的数据位宽紧张ECC计算需要7bit的校验位,因此物理IP最少需要126bit的ram IP。通常memory产生工具会更具时钟频率,深度位宽等因素对ram进行切分,因此本例中,使用了2个32x64的ram ip。

在data_in写入ram_asic模块之前,会经过ecc_gen模块,产生7bit的ecc校验位,随着数据一同写入ram_asic,其中data_in[63:0]写入第一个ram_asic,{2’b0,ecc_in[6:0],data_in[118:64]}写入第二个ram_asic。从ram_asic读出的数据会经过ecc_out模块经过ecc校验,输出校验后的data_out[118:0]和2bit的ecc_err_out告警。

审核编辑:刘清

-

暴利?一枚芯片的实际成本是多少?2016-04-25 28333

-

C语言中未初始化的局部变量到底是多少2022-10-21 2574

-

请问PCM2903C的温度范围到底是多少呢?2024-10-14 469

-

ADS1298ECG-FE原理图上看见很多NI的符号, 到底是什么意思呢?2025-02-05 734

-

PLC到底是什么呢?2014-10-10 5275

-

请问ADRF6612参考路径的分频到底是多少呢?2018-09-25 1335

-

请问Latch到底是什么呢?2018-12-06 12692

-

如果买了5G手机,能达到的理论速率到底是多少呢?2021-06-18 5093

-

时钟跑的到底是多少M呢2021-08-12 1507

-

请问一下ARM Cortex A9的核心(4核心) 到底是多少HZ呢?2022-08-25 2849

-

请问AD8603的电源供电范围到底是多少呢?2023-11-15 693

-

请问AD9684最低采样率到底是多少?2023-12-04 533

-

PCB走线之安全间距到底是多少2016-06-17 5608

-

芯片的成本如何计算一颗芯片的实际成本到底是多少?2020-02-06 32773

-

直插有源晶振DIP14封装到底是多少个脚2022-05-19 3953

全部0条评论

快来发表一下你的评论吧 !