内存芯片制造工艺 DRAM工艺流程 堆叠式DRAM工艺流程

描述

内存芯片制造工艺

内存芯片在驱动ic市场和ic技术发展方面发挥了重要作用。市场上两个主要的内存产品分别是DRAM和NAND。对于一台电脑,无论是台式个人电脑还是笔记本电脑,产生的数据被写入非挥发性存储器件,如磁性硬盘存储器(HDD)或固态硬盘存储器(SSD)之前,总是首先存储在DRAM中。台式个人电脑或笔记本电脑的内存容量短短几年间成倍增长。1993年的个人电脑台式机486仅有8兆字节(MB)的DRAM,这是从成本为100美元的4MB升级而成的。而在2009年,只需花费30美元左右就可以购买4千兆字节(GB)的DRAM。随着对图形化特性的需求,特别是三维图形需求不断增加,一台电脑的DRAM量需求将进一步增加,并继续推动DRAM制造技术的发展。

与保存数据一直需要电源供应的DRAM不同,NAND是一种非挥发性存储器,可以在无电源供应下保存数据许多年。NAND闪存被广泛应用于移动数字电子产品,如MP3播放器、数码相机、手机、高端笔记本电脑数据存储。随着移动电子设备应用更多的图形处理和视频,对NAND的需求将进一步增加。NAND也釆用混合形式,将固态硬盘存储器(SSD)的数据快速存储和磁性硬盘存储器(HDD)的低成本结合起来。

DRAM工艺流程

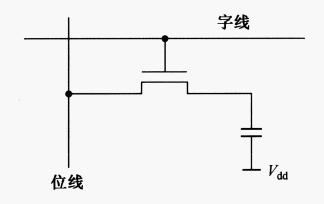

DRAM扮演着驱动IC市场和IC技术发展的重要作用。DRAM单元由一个NMOS和一个存储电容组成(见下图)。

有两种DRAM形成工艺:一种是堆叠DRAM,是将存储电容堆叠在晶体管(NMOS)上;另一种是深沟槽DRAM,这种结构是在NMOS旁边的硅表面上形成深沟槽式存储电容。

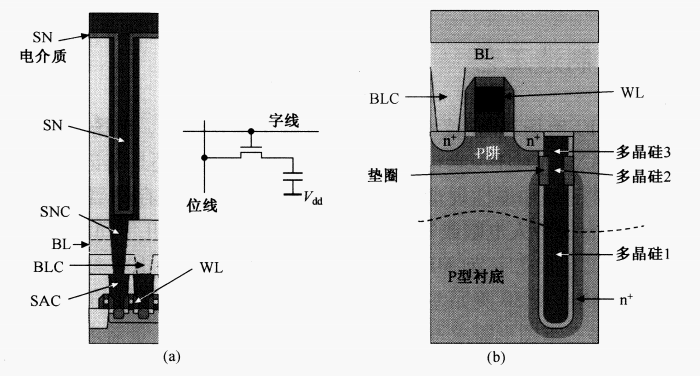

下图(a)显示了堆叠式DRAM。SAC代表自对准接触,BLC表示位线接触,WL代表字线,BL代表位线,SNC表示存储节点接触,SN表示存储节点,就是存储电容。下图(b)所示为一个深沟槽DRAM。由于沟槽电容的长宽比超过50,所以图示只是一部分。从图中可以看到,深沟槽DRAM的硅表面金属互连面积比较小,使得这种结构更容易和普通的CMOS后端工艺兼容,并成为片上系统(SoC)应用嵌入式DRAM的选择。然而,由于这种结构需要在有限的硅表面形成存储电容,沟槽式DRAM的堆积密度与堆叠DRAM不同,因为这种结构并不需要很大的硅表面构建存储电容。通用DRAM芯片对价格非常敏感。由于堆叠式DRAM比深沟槽DRAM成本低,所以它主导着DRAM市场。本章只讨论堆叠式DRAM工艺流程。

堆叠式DRAM工艺流程

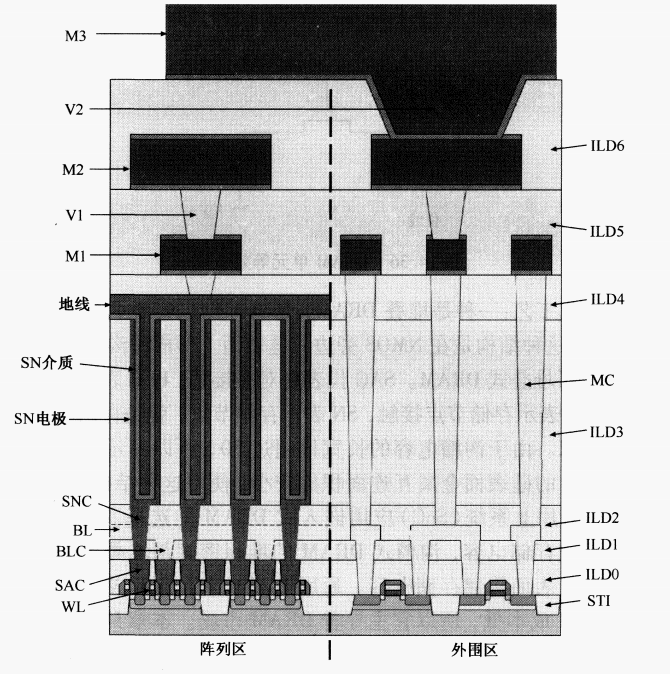

大多数电脑和其他数码电子产品使用的DRAM芯片是堆叠式DRAM。下图显示了堆叠式DRAM芯片横截面。下图左侧显示了具有4个存储单元的截面。3nm工艺技术的2GB DRAM芯片具有20亿个这样的单元。外围逻辑电路用于控制写入、读出和DRAM芯片的输入/输出操作。外围器件面积通常比阵列单元面积大,而且制作工艺与之前描述的CMOSI艺技术非常类似。后续将主要说明单元阵列的工艺流程。

审核编辑:刘清

-

INTEL芯片制作工艺流程2009-09-21 90035

-

PCB工艺流程详解2013-05-22 10145

-

SMT贴装基本工艺流程2018-08-31 3464

-

晶体管管芯的工艺流程?2019-05-26 3440

-

芯片制造全工艺流程解析2020-12-28 19163

-

关于黑孔化工艺流程和工艺说明,看完你就懂了2021-04-23 3504

-

样板贴片的工艺流程是什么2021-04-26 3461

-

芯片生产工艺流程是怎样的?2021-06-08 11902

-

PCB制造工艺流程是怎样的?2021-11-04 24505

-

芯片封装工艺流程-芯片封装工艺流程图2008-05-26 8640

-

pcb工艺流程2016-02-24 1381

-

半导体知识 芯片制造工艺流程讲解2019-01-26 41629

-

芯片制造工艺流程步骤2021-12-15 46665

-

芯片印刷工艺流程.zip2022-12-30 826

-

一文解析DARM工艺流程2024-04-05 11682

全部0条评论

快来发表一下你的评论吧 !