怎样使用AWR软件进行MMIC产品开发的设计?

描述

半导体器件为移动设备、通信基础设施和航空航天应用提供卓越的射频性能。实现性能需要可靠的电路仿真、电磁(EM)验证、通信测试平台以及将电气设计与物理实现联系起来的设计流程。Cadence AWR Design Environment软件提供从前到后单片微波集成电路(MMIC)设计流程,具有创新的用户界面以及设计输入、仿真和物理设计工具的完全集成,可提高工程生产力并确保一次性成功。

MMIC设计优势

AWR设计环境平台提供工艺设计套件(PDK)、仿真技术和设计自动化,以加速MMIC从概念到产品的开发,并能够灵活地应对任何设计挑战。设计向导和项目模板可帮助设计人员快速启动设计,并将现有设计提升到新的性能水平。

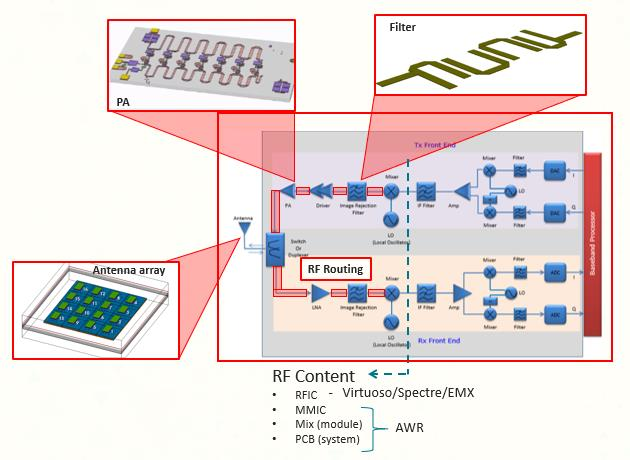

图1、以针对射频前端毫米波段应用为示例

设计管理

AWR可以提供先进的报告/测量管理使设计人员能够同时跟踪多个仿真结果,从单个位置管理测量数据源和参数,并在单个仪表板显示中创建一组链接的报告。简化的功率放大器(PA)测量可以轻松绘制非线性测量结果,例如增益压缩或效率与输出功率的关系,这是呈现放大器性能的常用方法。

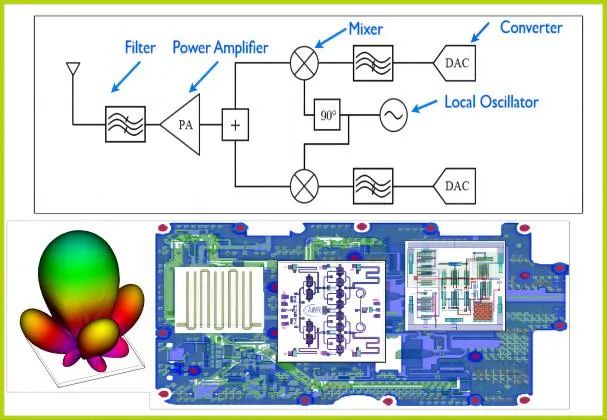

图2、针对射频模组的仿真实例

仿真

基于电路的注释提供电流密度和临界电压的即时仿真反馈,在布局之前就查明可靠性问题。统一数据库架构动态链接电气和物理设计,以实现原位EM验证和制造就绪布局。

CadenceAWRAPLAC谐波平衡(HB)仿真器将线性和非线性频域仿真与时域瞬态仿真相结合,以其在处理棘手问题时的速度和收敛性而闻名。它解决了高度非线性问题、具有大量活动设备的网络,以及可以针对高阶MMIC进行设计。

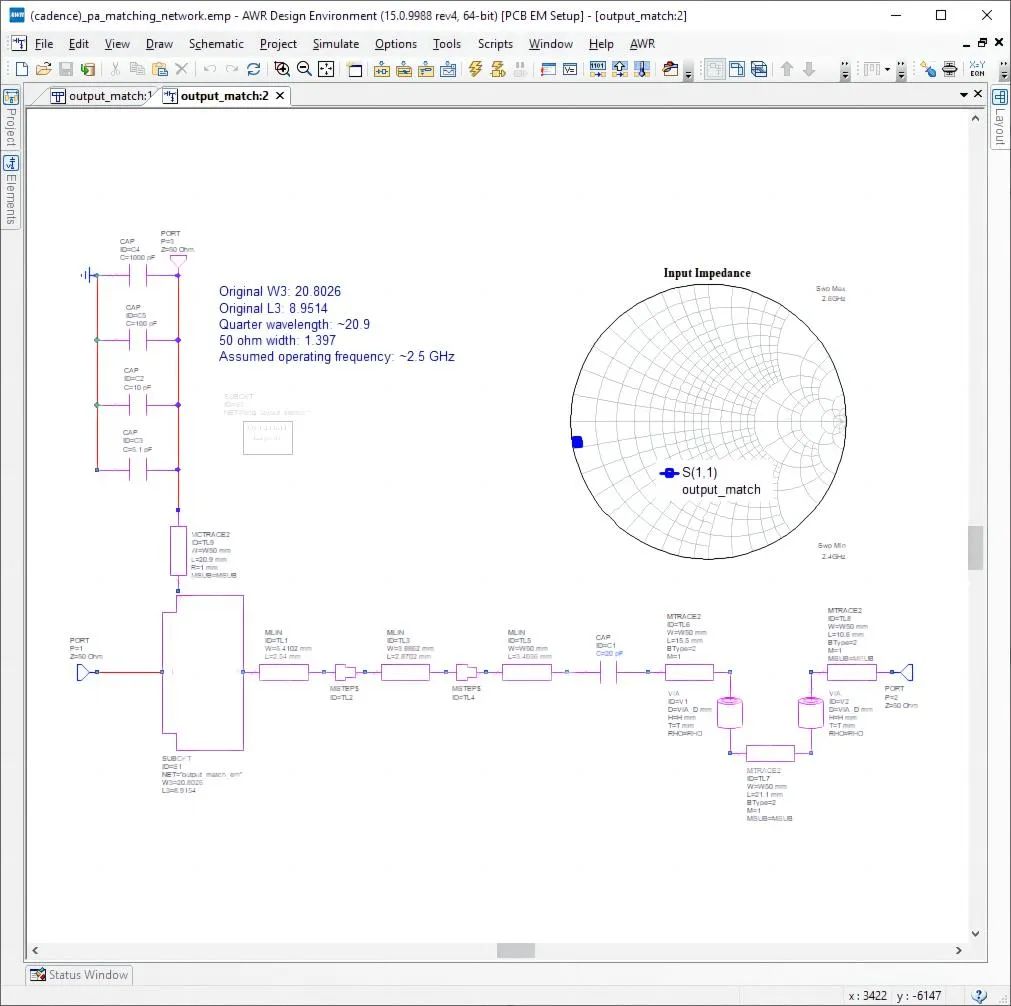

图3、AWR可以将电路和布局进行共享

制造设计

制造设计(DFM)是AWR软件平台所固有的,可对来自代工厂授权的PDK的特定工艺金属迹线和片上组件进行精确建模。GDSII布局文件的导出支持将设计信息传输到专用制造工具中。

与MMIC代工厂合作开发的PDK为使用AWR设计环境软件的工程师提供原理图、可扩展布局参数化单元(PCell)、高级布局实用程序和连接检查/突出显示,以及具有预定义基板叠层和预配置功能的精确EM仿真.

模拟设置。AWR软件客户通过减少设计失败来提高利润。软件中的良率和拐角分析可帮助设计人员研究电路性能的统计变化,并根据已知的工艺公差修改指定参数的标称值,从而优化制造良率。

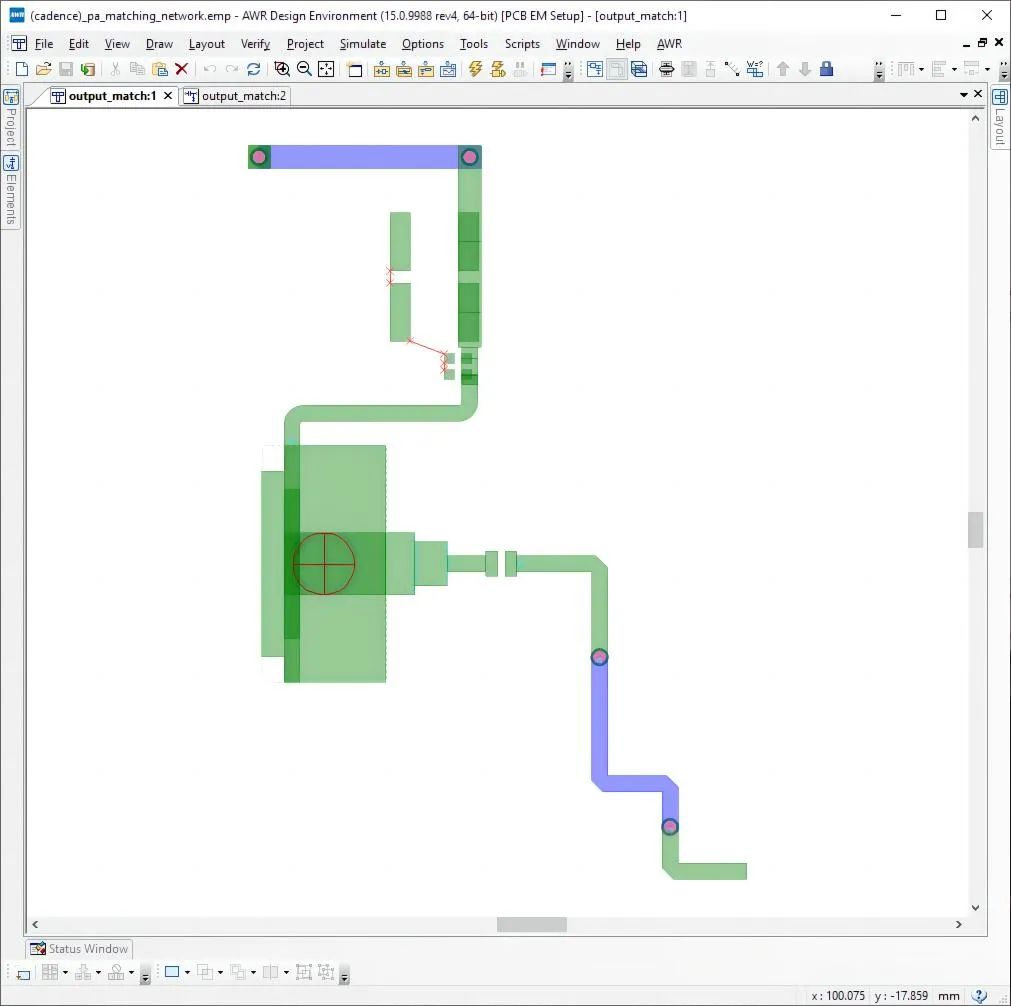

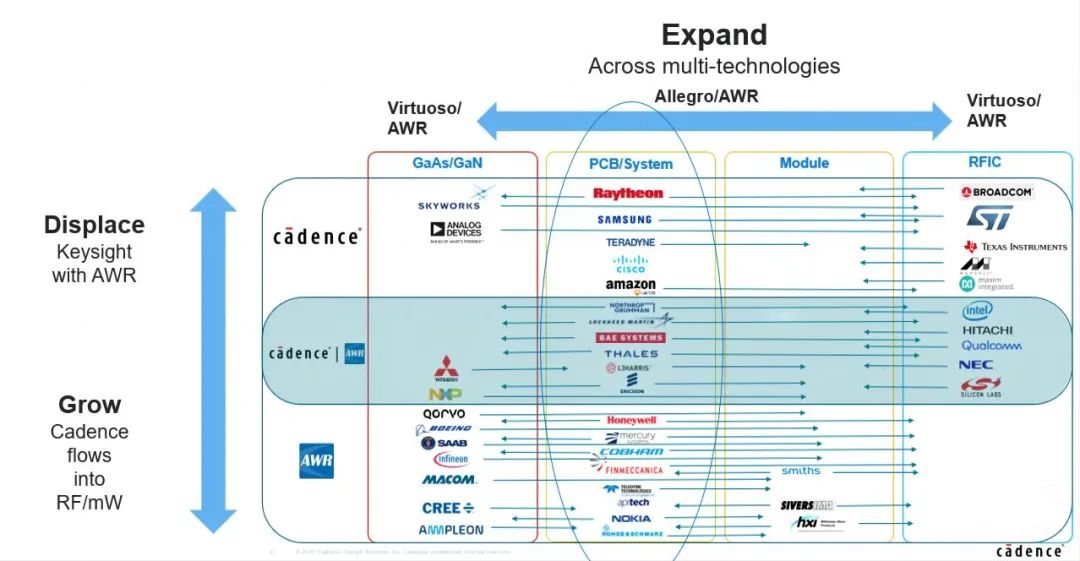

图4、针对产业链上下游的AWR应用范围

总结:AWR优势

具有特定于流程的模型和布局PCell的强大设计输入;

准确、快速且稳健的HB模拟;

用于III-V半导体代工厂的PDK;

用于互连建模的自动电路提取(ACE)技术;

Cadence AWR AXIEM EM模拟器,用于设计验证和寄生参数提取;

Cadence AWR Analyst EM模拟器,用于分析凸块、键合线和焊带;

EM Socket,可用于与第三方EM工具集成;

ERC、DRC和LVS支持生产就绪的GDSII导出;

用于电路包络分析和无线标准验证的系统协同仿真;

审核编辑:刘清

-

AWR2944P/AWR2E44P等雷达传感器芯片详解2026-01-26 2578

-

适用于AWR和IWR MMIC 的四路 8.8MHz 降压转换器LP876242-Q1数据表2024-03-28 409

-

电动汽车雷达-MMIC评估软件2021-06-01 696

-

适合NFC天线系统设计的AWR软件有哪些?2021-05-24 1709

-

AWR2011设计软件有什么亮点2020-09-01 828

-

AWR2011全新的AWR设计套件介绍2019-07-04 3419

-

MAMF-011015GaAs MMIC产品介绍2019-04-23 2001

-

AWR射频、微波设计软件及其应用对象分析2017-12-11 13297

-

南航使用AWR进行射频微波研究及教学2017-12-07 1176

-

最新的高频模块设计的AWR白皮书提供下载(你还等什么?)2017-12-06 1122

-

AWR发布V11版本的NI AWR设计套件2017-12-05 917

-

AWR官方软件下载2013-09-13 4328

全部0条评论

快来发表一下你的评论吧 !