基于FPGA的DDR3读写测试

描述

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

MIG控制器支持两种接口:(1)简单用户控制逻辑接口;(2)AXI接口。该工程采用前者,后面会整理DDR3的AXI总线访问方法。

下面简单介绍一下MIG控制器IP核的使用以及FPGA板上测试结果。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7A35TFTG256-1;

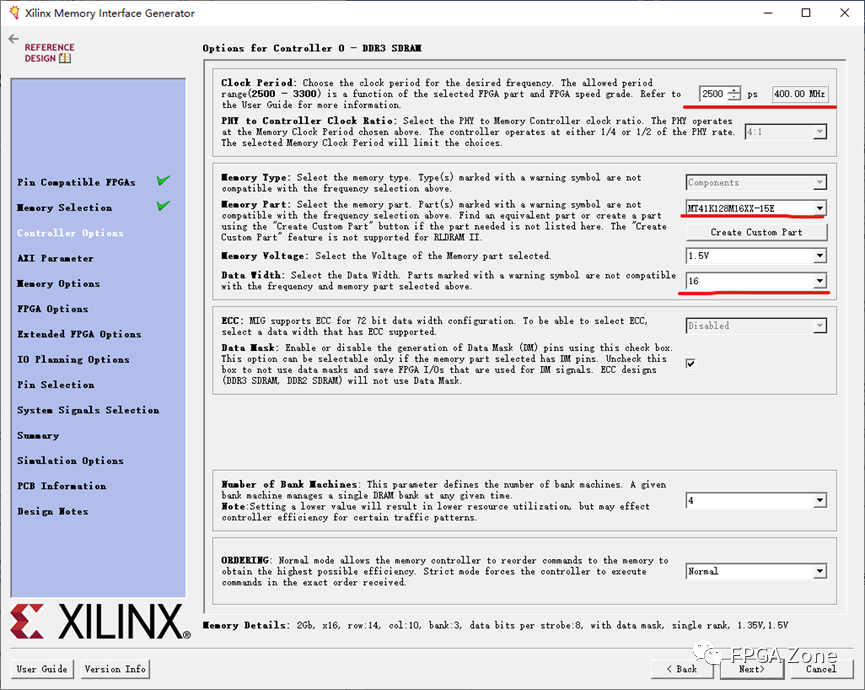

02IP核参数配置

MIG(Memory Interface Generator)IP核提供了用户接口逻辑,以便于实现对DDR的访问。有关MIG的详细描述,可以参考官方文档:ug586。这里不展开介绍。

接口配置界面,保持默认选项。

- Clock Period:配置主时钟频率,这里选择400M。由于DDR是双沿工作,所以读写速率为400M2Data Width(16bits);

- 主时钟频率和用户时钟频率比例:4:1,因此生成的用户时钟为100M;

- Memory Part:配置DDR参数,根据实际情况选择;

- Data Mask:如果选用的DDR带有data mask就选上,并将信号拉低,表示不屏蔽数据接口;

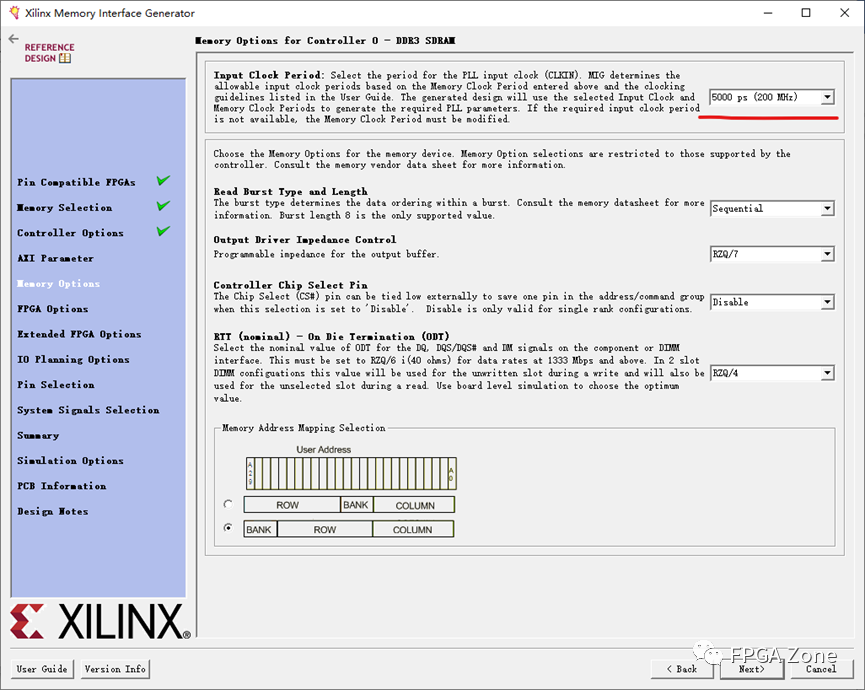

Input Clock Period:输入时钟,这里选择200M。

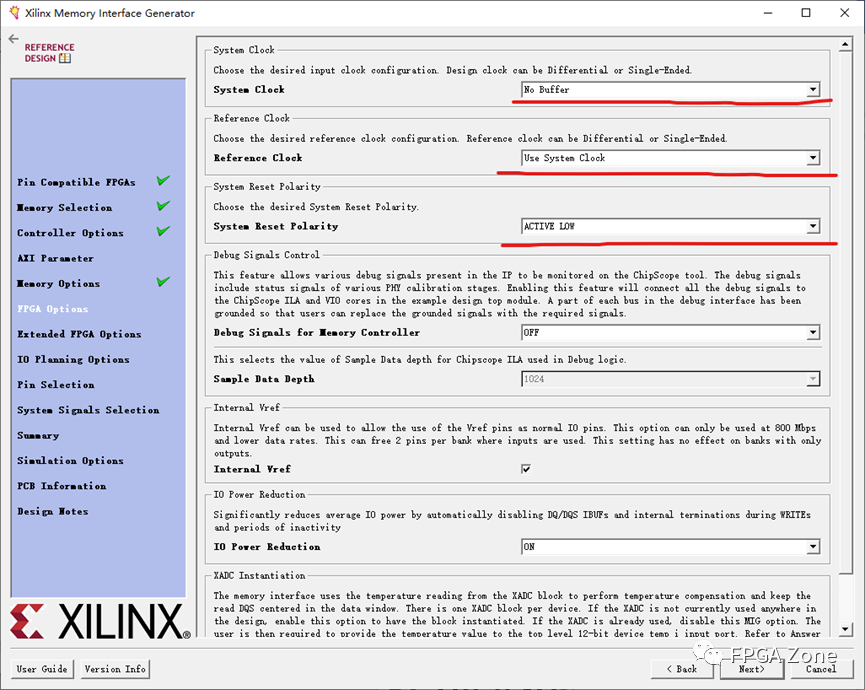

- System Clock:No Buffer;

- Reference Clock:使用系统时钟;

- 系统复位信号:低电平有效;

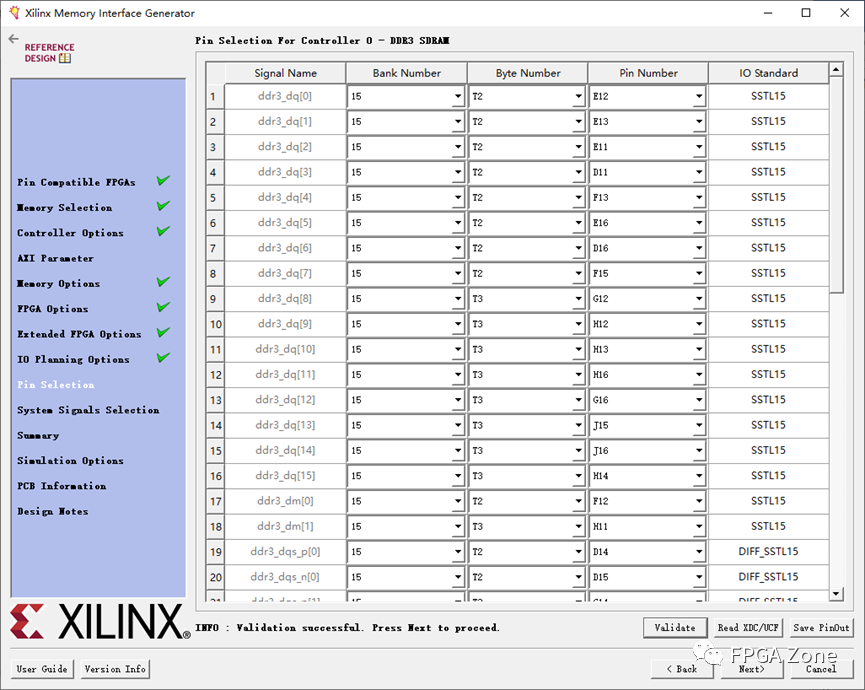

读取XDC文件管脚配置,并点击validate,进行校验。

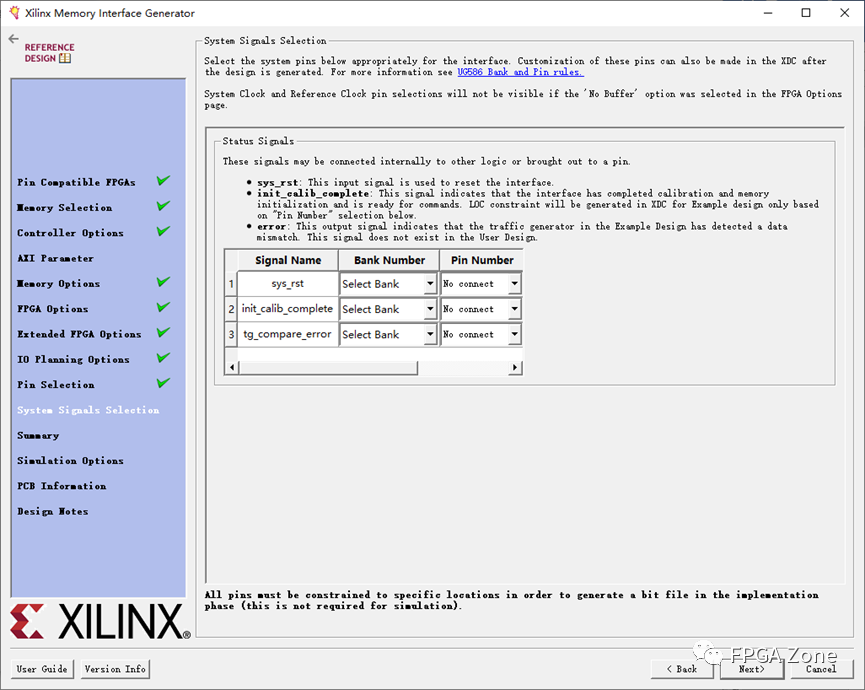

系统信号选择不用配置,保持默认选项即可。

03用户接口 & 读写时序

MIG IP产生的用户接口信号是以app_*格式命名:

input [127:0] app_rd_data; //读数据

input app_rd_data_end; //读数据结束

input app_rd_data_valid;//读数据有效

input app_rdy; //MIG控制器准备好读写

input app_wdf_rdy; //MIG控制器准备好写

output [27:0] app_addr; //读写地址

output [2:0] app_cmd; //读写命令

output app_en; //控制命令使能

output [127:0] app_wdf_data; //写数据

output app_wdf_end; //写数据结束

output app_wdf_wren; //写数据使能

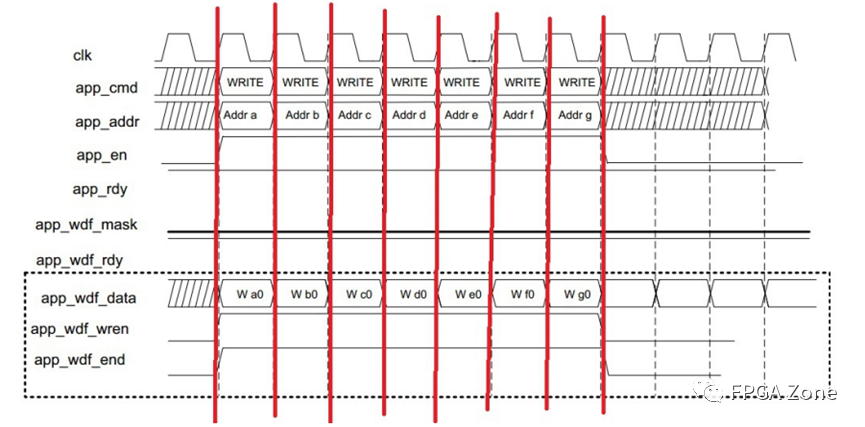

DDR写时序如下图所示。逻辑比较简单,将所有信号严格对齐即可。但有一个需要注意的地方,就是当 app_rdy 和 app_wdf_rdy 都为高的时候,才能同时拉高 app_en ,这时写入的数据才有效。

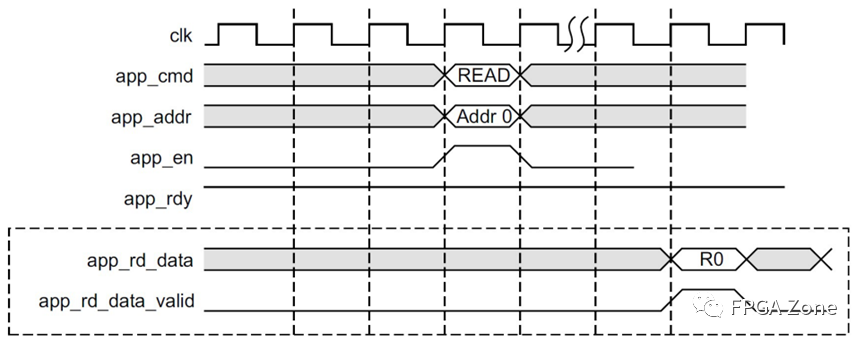

DDR读时序如下图所示。app_cmd、app_addr、app_en、app_rdy信号严格对齐即可,但是同样需要在 app_rdy 拉高的情况下,才能拉高 app_en 。另外,数据读出会略有延迟。

04Vivado工程源码结构

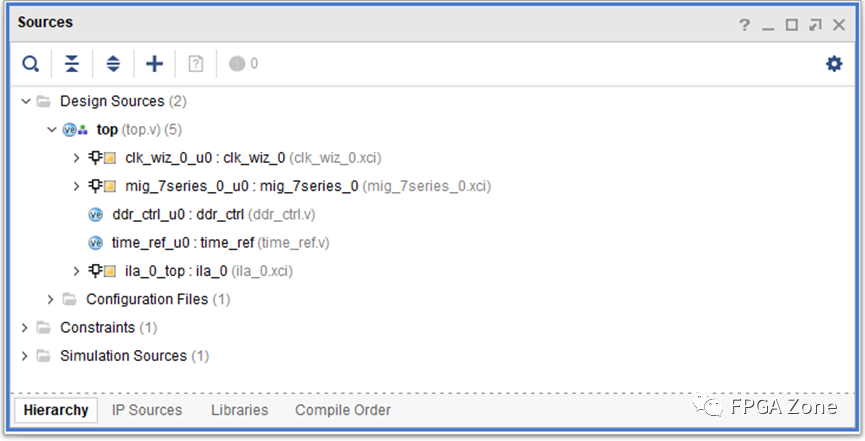

本工程源码结构如下图所示。

- ddr_ctrl:ddr用户接口读写控制模块;

- clk_wiz_0:产生200M时钟供MIG IP使用;

- time_ref:系统时间基准模块,以1s为周期计数;

05实现功能 & 测试结果

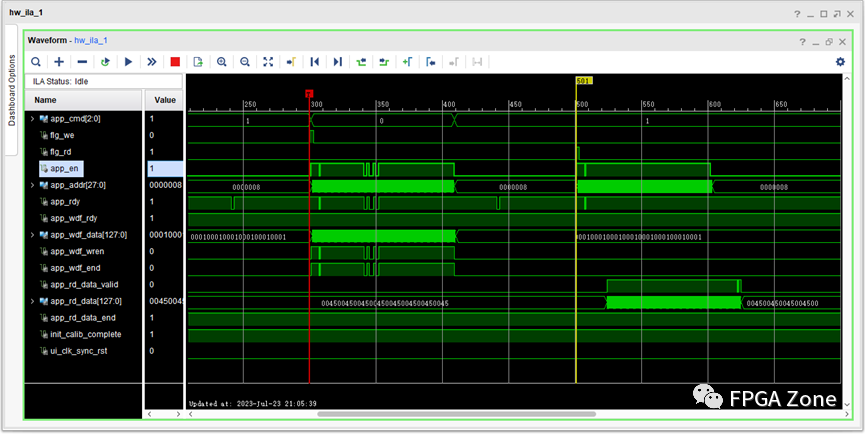

该Vivado工程主要用于FPGA DDR3读写功能测试。基于用户控制逻辑接口,以1s为周期,每周期内完成1次读写操作。板上测试1次读写操作的结果如下图所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于FPGA的DDR3多端口读写存储管理设计2024-06-26 843

-

阐述DDR3读写分离的方法2023-10-18 2241

-

基于AXI总线的DDR3读写测试2023-09-01 7785

-

FPGA学习-DDR32022-12-21 5631

-

Virtex7上DDR3的测试例程2022-08-16 3523

-

【紫光同创国产FPGA教程】【第十章】DDR3读写测试实验2021-02-05 11425

-

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍2021-01-01 5578

-

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制2020-12-15 3888

-

关于FPGA外部的DDR3 DRAM怎么回事2020-05-20 3188

-

基于FPGA的DDR3六通道读写防冲突设计2018-08-02 3676

-

基于FPGA的DDR3多端口读写存储管理的设计与实现2017-11-18 8177

-

ddr3的读写分离方法有哪些?2017-11-06 9639

-

基于FPGA的DDR3多端口读写存储管理系统设计2015-04-07 14152

全部0条评论

快来发表一下你的评论吧 !