英特尔将于明年推出一款新的数据中心芯片Sierra Forest

描述

在当今互联网和在线服务的驱动下,数据中心或许将成为不可或缺的动力引擎。

数据中心的高能耗已经成为一个令科技公司头痛的问题;为了应对保持或减少能源消耗的压力,各大芯片制造商都在努力提高芯片的计算效率。

然而,为了应对保持或减少能源消耗的压力,各大芯片制造商都在努力提高芯片的计算效率。

近日,英特尔将于明年推出一款新的数据中心芯片“Sierra Forest”,该芯片的每瓦性能将比当前一代数据中心芯片提高240%。

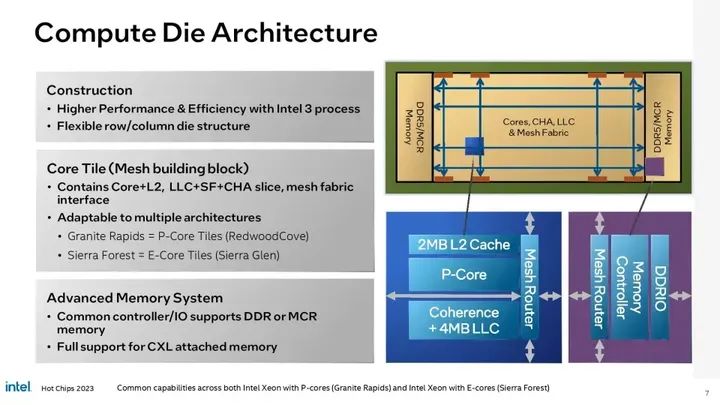

在 Hot Chips 2023 上,英特尔首次深入展示了其未来 144 核 Sierra Forest和 Granite Rapids 处理器:

前者由英特尔全新 Sierra Glen E 核心组成,后者则采用全新 Redwood Cove P 核心。

由英特尔所言,其即将与2024年上半年推出的下一代“Sierra Forest ”芯片;其采用新的基于区块的架构,该架构在“Intel 7”工艺上配备双 I/O Chiplet,并与“Intel 3”上蚀刻的不同配置的计算核心搭配使用过程。

其次,这种设计使英特尔能够基于不同类型的核心打造多种产品,同时保持相同的底层配置。

革旧鼎新的时代,英特尔将打造巨大性能提升的芯片,甚至超越上一代:

Sierra Forest 和 Granite Rapids 融入 Birch Stream 平台,具有插槽、内存、固件和 I/O 兼容性,可提供简化的硬件验证流程;它们还可以与相同的软件堆栈互操作,从而允许客户根据自己的需求使用任一芯片。

英特尔称:下一代 Sierra Forest 基于 E 核的设计将比第四代至强芯片提供高达 2.5 倍的机架密度和 2.4 倍的每瓦性能,而 P 核驱动的 Granite Rapids 将提供 2 倍的机架密度和 2.4 倍的每瓦性能;混合 AI 工作负载的性能提高了 3 倍,部分原因在于内存带宽“高达”2.8 倍的提升。

相比之下,英特尔在 Sapphire Rapids 中还采用了四芯片设计,每个芯片都包含一部分相关 I/O 功能:

例如,内存和 PCIe 控制器,新处理器将一些 I/O 功能完全分解为两个独立的 HSIO Chiplet,这些Chiplet蚀刻在 Intel 7 工艺上,从而为 I/O 提供成本、功耗和性能的最佳平衡,而 CPU 内核和内存控制器则独立存在专用计算Chiplet。

尤其,将两个 HSIO 裸片放置在芯片封装的顶部和底部,中间有一到三个计算裸片,所有裸片均通过未指定数量的EMIB(嵌入式多芯片互连桥)互连熔合在衬底内并连接到桥每一端的芯片到芯片互连。

与此同时,E 核心排列成两个或四个核心集群,共享 4MB 二级缓存片和 3MB 二级缓存。配备 E-Core 的处理器配备多达 144 个内核,并针对最高的功效、面积效率和性能密度进行了优化;对于高核心数型号,每个 E 核心计算芯片拥有 48 个核心。

图片来源:英特尔

众所周知,强大的性能提升才能足以支撑如今的数据中心,且所面临的工作负载性分为:

第一个:是以人工智能为代表的计算密集型工作负载。

第二个:是通用工作负载。

第三个:是高密度的横向扩展型工作负载。

特别需要注意的是:基于以上工作负载对数据中心的处理器提出的要求有所不同;其中,包括更高的性能、更高的密度、更高的带宽及内存,及更高的能效等。

综上所述,随着 AI 等技术的发展,数据中心是互联网和在线服务的重要支持;但由于平时消耗巨大量电力,科技公司正面临越来越大的压力;因此在保持算力稳定的同时,也减少能源使用量。

审核编辑:刘清

-

英特尔将在2014年推出14纳米处理器芯片2011-12-05 3619

-

英特尔将推数据中心节能芯片 获Facebook认可2012-12-12 2733

-

英特尔多款平板电脑CPU将于明年推出2013-12-19 3887

-

阿里巴巴携手英特尔开发一款基于FPGA的解决方案,以帮助客户提升业务应用的性能2017-03-15 3156

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 3059

-

苹果Mac弃用英特尔芯片的原因2020-06-23 5093

-

英特尔:芯片是整个数据中心的核心2012-03-08 3821

-

英特尔推出一款完备的硬件和软件平台解决方案2018-01-22 1243

-

英特尔推出全新FPGA全力打造数据中心2019-06-11 819

-

英特尔推出10nm+Agilex FPGA以全力打造数据中心2019-10-23 860

-

288核心,英特尔创新日公开Sierra Forest新规格2023-09-21 1177

-

英特尔144核至强Sierra Forest和Granite Rapids处理器的信息揭秘2023-09-25 1270

-

英特尔至强处理器新动态:Sierra Forest已进入通电验证阶段2024-01-30 1113

-

英特尔公布Clearwater Forest至强处理器由17个小芯片组成,包含计算能力2024-02-26 1347

-

英特尔 Clearwater Forest-AP处理器曝光2025-01-23 922

全部0条评论

快来发表一下你的评论吧 !