高速PCB设计调整走线长度

PCB设计

2585人已加入

描述

数字系统对时序要求严格,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。调整走线长度包括两个方面:相对的和的。

所谓相对的就是要求走线长度保持一致,保证信号同步到达若干个接收器。有时候在PCB上的一组信号线之间存在着相关性,比如总线,就需要对其长度进行校正,因为需要信号在接收端同步。其调整方法就是找出其中长的那根走线,然后将其他走线调整到等长。

而的要求是控制两个器件之间的走线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由高速电路设计者提出,而由PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要注意,信号传播速度是和PCB的材料、走线的结构、走线的宽度、过孔等因素相关的。知道了信号传播速度,就知道了要求的走线延迟对应的走线长度。

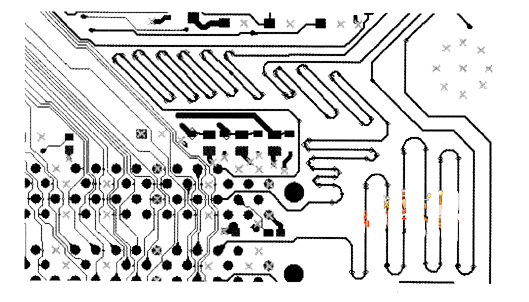

走线调整常采用蛇形线的方式,如图所示为某一款主板的顶层走线就是采用蛇形线的这种方式。

图 一款主板顶层走线的长度调整

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB设计高速模拟输入信号走线方法及规则2018-05-25 10211

-

高速信号的走线长度如何控制?2010-06-27 4828

-

高速PCB设计2015-05-05 6482

-

高速PCB设计解决EMI问题的九大规则2016-01-19 4199

-

解决高速PCB设计EMI(电磁干扰)的九大规则2017-11-02 2952

-

高速PCB设计调整走线长度2018-11-27 2783

-

9大硬件工程师谈高速PCB信号走线规则2018-11-28 2490

-

高速PCB设计常见问题2019-01-11 2342

-

为什么From To Editor无走线长度?2019-09-16 3480

-

PCB布局和走线的调整2019-10-17 3555

-

如何实现Altium PCB设计中的内部走线长度?2020-08-12 2540

-

高速pcb信号走线的经典规则让pcb设计不再难2017-11-25 9010

-

高速PCB设计中的走线技巧2019-07-01 6672

-

pcb如何在走线长度匹配中考虑整个信号带宽2021-01-05 5684

-

PCB布局的关键:尽量缩短开关节点走线长度?2023-08-07 1888

全部0条评论

快来发表一下你的评论吧 !