Codasip携CORDIC加速器技术白皮书亮相RISC-V中国峰会

EDA/IC设计

描述

始创于2018年的RISC-V峰会,从北美发展到中国再到欧洲大陆。自2023年起,北美,中国和欧洲三大峰会开始“三足鼎立”,进而辐射覆盖到全球RISC-V市场。Codasip自2018年起便作为北美峰会的赞助商与大家见面,2021年起也开始作为中国峰会的赞助商,助力RISC-V本土化进程,至今已经走过了三个年头。可以说我们是看着RISC-V中国峰会从无到有的,经历过疫情最为艰难的时期,从不放弃,从初始到壮大再到2023年的盛况空前。

逾2000的访客,18家企业展商,16家社区展位,16场同期活动,100余场主题报告,64个poster 和 31个poster预约。以及多达800余家的参会企业,50余家投资机构和70多个大学和科研机构,加上数量客观的RISC-V爱好者,共同组成了RISC-V峰会历史上规模最大、内容最丰富、影响最广泛的一届峰会。

在本届峰会中,Codasip中国区总经理胡征宇先生发表了主题为RISC-V • 定制计算 • 软/硬件协同设计的演讲,吸引了将近200人的关注。这十年来经过同仁们的不懈努力以及RISC-V的天然优势,科普和定义RISC-V已然无须赘述。这个开源的指令集架构由于其灵活性、可扩展性和模块化而越来越受欢迎。事实上,RISC-V的主要优点和主要 "存在理由 "之一是可定制的指令集(ISA)和可定制的处理器内部设计(微架构)以满足特定的应用要求。这种定制能力延伸到定制计算解决方案,使开发人员能够创建为其工作负载优化的硬件。定制计算使设计者能够为特定类型的工作负载创建优化的硬件。它可以实现任何工艺技术增益都无法带来的PPA收益,包括已经失效的摩尔定律。

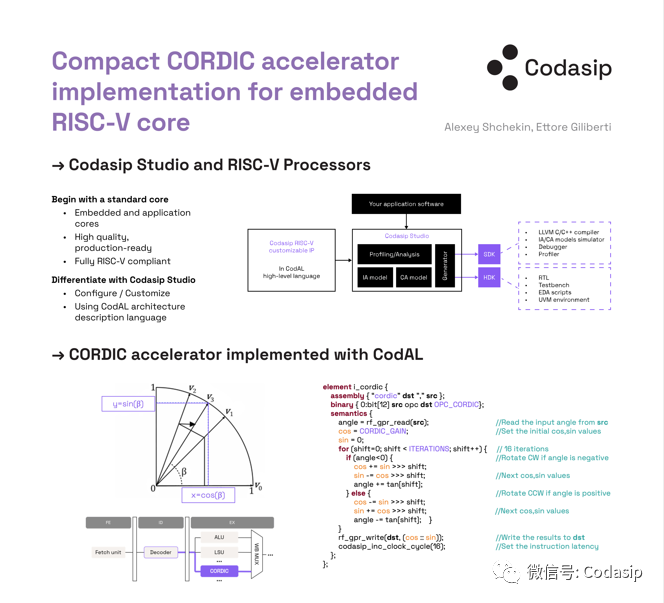

在本届峰会的海报展示环节,Codasip也展示了RISC-V在缩小代码方面做出的努力,并为观众展示了主题为 “用于嵌入式 RISC-V 内核的紧凑型 CORDIC 加速器实现” 的技术白皮书海报。

三角函数用于许多嵌入式系统应用,例如信号和图像处理、控制理论、通信系统和机器人技术等。利用 RISC-V ISA 灵活性和 Codasip 处理器设计技术的优势,我们提出了一种快速高效的 CORDIC 算法实现方案,该算法在嵌入式 RV32IMCB 内核中作为自定义指令实现,以便顺利计算三角函数。最后这种定制化解决方案的结果是提高了性能,将处理时间减少了 24 倍,能耗减少了 13.5 倍,但硅面积仅仅增加了 4%。CORDIC 加速器是用 210 行 CodAL 代码实现的。如此紧凑的实施以及自动生成的工具链显著缩短了 ASIP 上市的时间。

在最好的时节,Codasip遇见最好的RISC-V中国峰会,参与其中,荣幸至极。期待来年峰会再相见!

-

Andes晶心科技亮相2025 RISC-V中国峰会2025-07-23 1727

-

直播预告|智算时代下,RISC-V 安全技术在金融场景的探索与实践2025-03-14 1065

-

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!2024-08-26 1541

-

Codasip利用RISC-V向量扩展实现领域专用加速器2023-10-18 1932

-

Andes晶心科技将亮相RISC-V中国峰会2023-08-22 1236

-

2023 RISC-V中国峰会:深圳技术分享会(同期会议)2023-08-16 1440

-

2023 RISC-V中国峰会:RISC-V深圳技术分享会(同期会议)2023-08-15 1870

-

HDC 2022重磅首发《鸿蒙生态应用开发白皮书》,附全文2022-11-11 2688

-

5G射频测试技术白皮书解析2021-01-13 3770

-

中国市场Wifi白皮书2015-11-06 884

-

中国移动互联网白皮书2014-02-21 4274

-

ZigBee白皮书2012-08-20 10358

-

【PPT】ASIC安全管理技术白皮书2011-02-24 3240

-

【经典】智能电网白皮书资料汇编2010-12-23 4014

全部0条评论

快来发表一下你的评论吧 !