为什么signed_vector的-128结果中间有很多空格?

电子说

描述

练习一

有符号数据与无符号数据对比

代码:

module vector_transfer();

logic [7:0] logic_vector=8'b1000_0000;

bit [7:0] bit_vector=8'b1000_0000;

byte signed_vector=8'b1000_0000;

initial begin

$display("logic_vector=%d",logic_vector);

$display("bit_vector=%d",bit_vector);

$display("signed_vector=%d",signed_vector);

end

endmodule

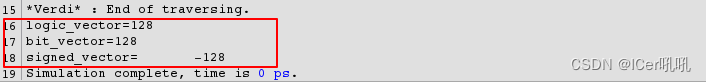

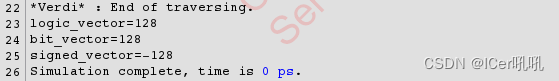

仿真结果:

相信各位小伙伴,都能理解该仿真结果的产生,但是可能有的小伙伴会有疑问,为什么signed_vector的-128结果中间有很多空格?你真的仔细,先为你竖起大拇指,接下来我们就讲解一下为什么输出结果会是这样。

这里是解释

首先,在开始阶段,声明变量logic_vector为8位,bit_vector为8位,signed_vector没有明确给出具体位宽,默认32位。是不是看到区别了,别激动,接着往下看,8位二进制数转换位十进制数最大值为2^8-1=255,位宽为3,同样道理,32位二进制数转换位十进制数最大值为2^32-1=42_6496_7295,位宽为10,理解了这个接下来就是重点了哦!!!在使用到display时,我们经常需要考虑到显示数据的对齐方式,一般会在%和指定基数之间通过指定域宽来实现显示数据的对齐,格式一般为:%(域宽值)(进制)

域宽值:即为显示数据的个数;

进制:可以是二进制b,十进制d,八进制o,十六进制h;

%(进制)默认为最大位宽

理解了这些,我们接着分析上边的代码:

$display("logic_vector=%d",logic_vector) 显示的logic_vector默认为最大位宽3

$display("bit_vector=%d",bit_vector) 显示的logic_vector默认为最大位宽3

$display("signed_vector=%d",signed_vector) 显示的logic_vector默认为最大位宽10

所以显示结果 logic_vector=128;bit_vector=128;signed_vector= -128(中间空7个位宽);如果想实现signed_vector= -128,可以修改代码:$display("signed_vector=%0d", signed_vector);%0表示按照实际位宽进行解释。

练习二

有符号数据与无符号数据转换

代码:

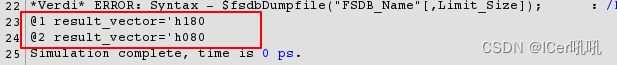

module vector_transfer1();

byte signed_vector=8'b1000_0000;

bit [8:0] result_vector;

initial begin

result_vector=signed_vector;

$display("@1 result_vector='h%x",result_vector);

result_vector=unsigned'(signed_vector);

$display("@2 result_vector='h%x",result_vector);

end

endmodule

仿真结果:

练习三

数据截取

代码:

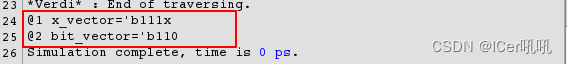

module vector_transfer2();

logic [3:0] x_vector=4'b111x;

bit [2:0] bit_vector;

initial begin

$fsdbDumpfile("vector_transfer2.fsdb");

$fsdbDumpvars;

end

initial begin

$display("@1 x_vector='b%b",x_vector);

bit_vector=x_vector;

$display("@2 bit_vector='b%b",bit_vector);

end

endmodule

仿真结果:

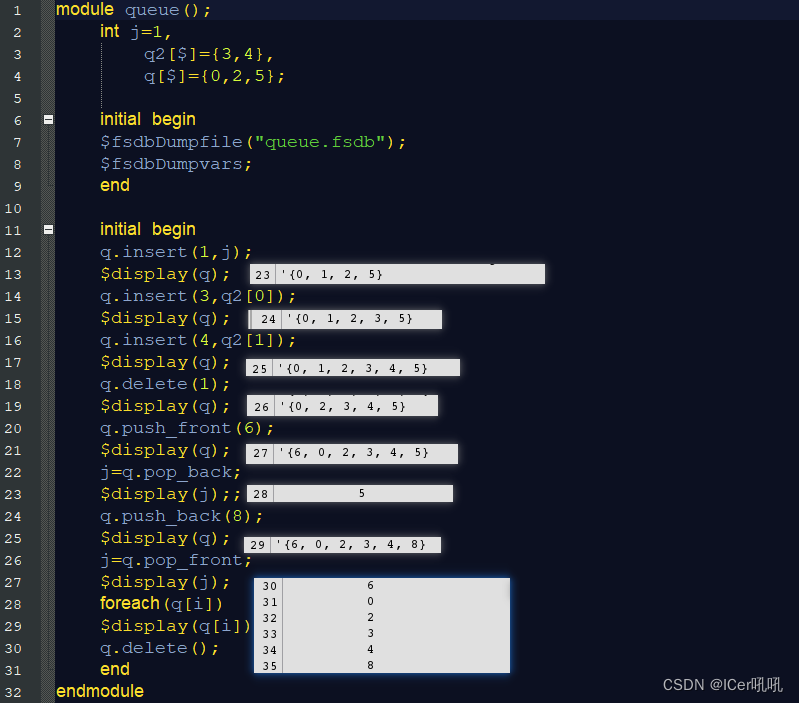

练习四

队列的基本用法

代码:

module queue();

int j=1,

q2[$]={3,4},

q[$]={0,2,5};

initial begin

$fsdbDumpfile("queue.fsdb");

$fsdbDumpvars;

end

initial begin

q.insert(1,j);

$display(q);

q.insert(3,q2[0]);

$display(q);

q.insert(4,q2[1]);

$display(q);

q.delete(1);

$display(q);

q.push_front(6);

$display(q);

j=q.pop_back;

$display(j);;

q.push_back(8);

$display(q);

j=q.pop_front;

$display(j);

foreach(q[i])

$display(q[i]);

q.delete();

end

endmodule

仿真结果:

审核编辑:刘清

-

Vector Team Services中国服务正式上线2025-06-11 1061

-

Verilog中signed和$signed()的用法2025-02-17 1628

-

中间继电器的型号有哪些2024-06-28 5402

-

python中如何用空格分隔2023-11-24 4797

-

c++之vector容器2023-07-13 2459

-

中间继电器的原理是什么 用途有哪些2021-08-30 11225

-

中间继电器的原理及用途有哪些2021-08-16 43442

-

C++中vector的定义与初始化2021-02-02 10042

-

vector用法总结(转载)2016-05-01 3004

-

Vector2016-04-15 741

-

字符串的列是由若干个空格隔开的,怎么读取成数组?2015-04-01 5786

-

Agilent Vector Signal Analysis2010-07-23 889

-

空格的ascii码,空格键的ascii码是多少2009-06-30 118732

全部0条评论

快来发表一下你的评论吧 !