国产RF-FPGA芯片宽带射频采集卡指标测试

可编程逻辑

描述

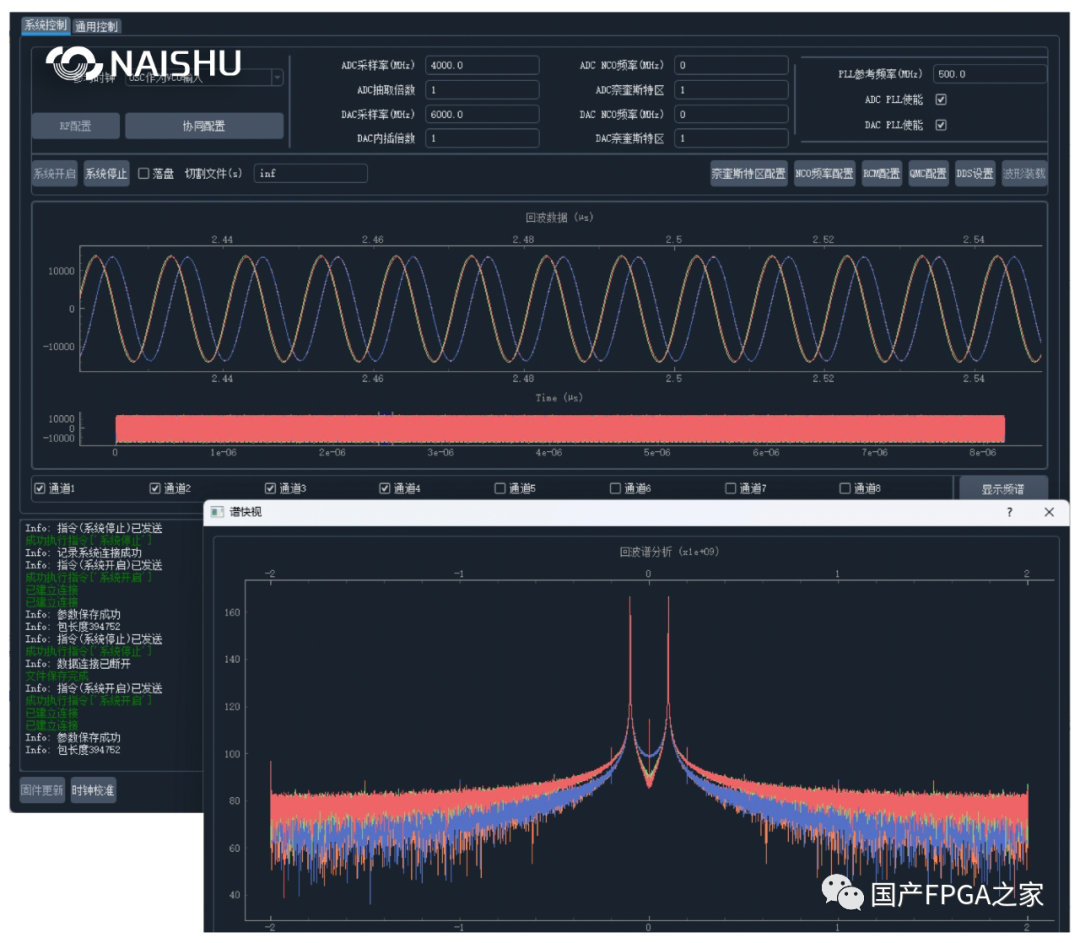

八月初,耐数电子怀着激动的心情发布了围绕国产RF-FPGA芯片的多通道宽带射频信号采集和播放板卡CSA-2T6R“干将”。正所谓“春风得意马蹄疾,一日看尽长安花”,团队的小伙伴们在过去三周里没有停歇片刻。逻辑部完成了集成RF-ADC、RF-DAC、DDR控制器、PCIe接口、千兆以太网以及软核CPU的通用测试工程;软件部发布了基于Python的PC端图形操控界面;测试部搭建了阵列A/D和D/A自动化性能测试环境;系统部提供了测试数据分析处理工具包。

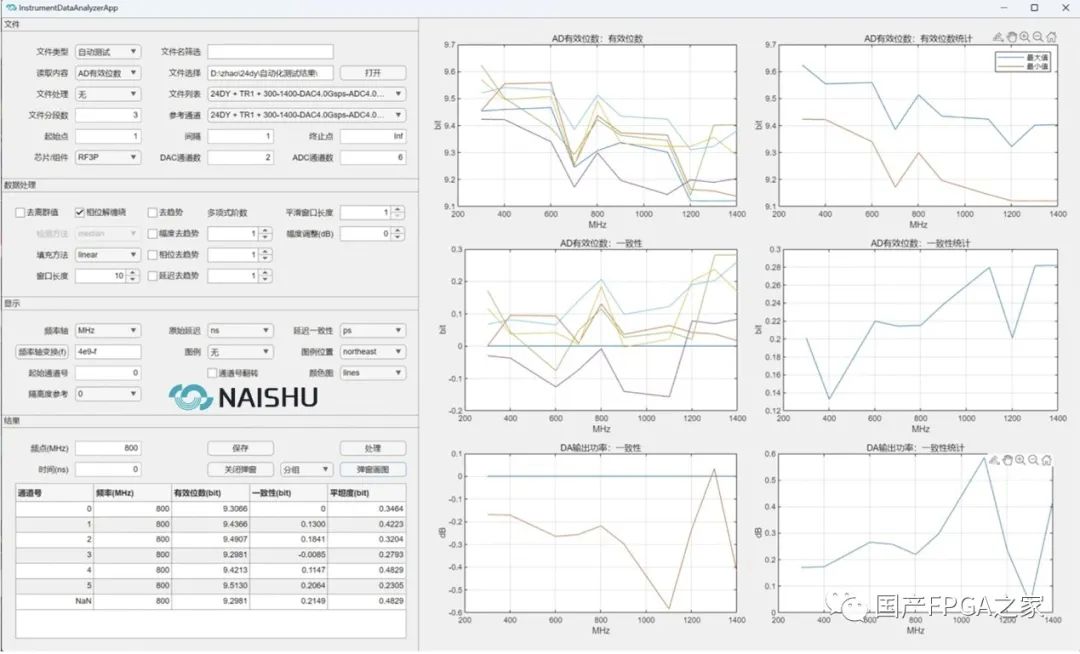

经过这一系列的工作,我们终于可以完整深入一气呵成的对干将的性能开展测试。主控软件根据脚本预设的测试序列自动控制信号源、频谱仪和矩阵开关、向板卡发出操作命令并获取测试数据。测试结果导入数据处理分析工具形成可视化输出。

测试数据表明,新款RF-FPGA内置的ADC和DAC具有令人满意的性能表现。各路ADC在4Gsps采样率、100MHz信号输入时,平均有效位数达到约10bit。ADC在4Gsps采样率下,输入信号频率在240MHz到1900MHz范围内,去除谐波成分后的SFDR达到-80dBc以上。DAC在6Gsps采样率下,输出信号的噪声谱密度(NSD)可低至-162dBm/Hz。

多路高速ADC和DAC集成在单芯片内,隔离度指标也是大家非常关心的问题。RF-FPGA芯片本身宣布了相当不错的隔离度实测指标,电路板级设计的水平必须要与之相配。实测表明,CSA-2T6R“干将”相邻通道ADC隔离度,在100-3900MHz范围内,均优于-60dBc;在800MHz以下的低频段则优于-70dBc。板上所选2路DAC的隔离度,在100-5900MHz范围内,均优于-70dBc。可见在核心器件自身能力的保障下,通过合理的板级设计,阵列化高密度的多路ADC和DAC可以做到相对优秀的通道隔离水平,有力支撑了该方案在相控阵、MIMO等领域的应用。

耐数测试部的小伙伴还饶有兴趣的测试了CSA-2T6R“干将”功耗表现。整板上电未加载FPGA程序时的静态功耗约为9.5W;FPGA加载ADC和DAC测试程序,开启RF-FPGA所有6路ADC采集和8路DAC播放,采样率分别是4Gsps和6Gsps,整板功耗约为30W;此时再关闭所有ADC和DAC,则功耗降至约16W。所以,14路ADC/DAC的总动态功耗约为14W,平均每通道仅1瓦,相当的省油呀。当然,这些功耗都会集中在RF-FPGA单芯片上,发热不可避免,优良的散热设计将会是RF-FPGA板卡或模块级设计的要点之一。干将的正式发售版将配套专门的散热结构套件。

当然,作为首板,一系列的测试也总能发现板级设计的一些不足之处。眼尖的看官一定注意到了配图中频谱通带内的由于接口驻波导致的波动。硬件部迅速定位了相关问题并制定了改进方案。在接下来的日子里,耐数电子的小伙伴们将继续砥砺前行,改进电路设计、完善逻辑和软件、提高生产和测试效率、补齐技术文档,迎接CSA-2T6R“干将”的正式发售。

One more thing:干将作为一款标准PCIe板型,主要适用于实验室或桌面环境。为了满足各种环境和平台对订制化多通道射频处理算力的需求,耐数基于RF-FPGA的下一款产品将是“龙泉”全国产智能阵列载荷平台。龙泉将在极小的体积内集成RF-FPGA与飞腾多核CPU,一步到位打通阵列射频采/播、可编程逻辑处理和通用CPU软件处理。整板投影面积小于150x150mm。高性能高紧凑的特性使得龙泉可以成为各种小型化应用平台的数字射频和软件处理核心。让我们拭目以待龙泉以及后续更多产品的好消息。

编辑:黄飞

-

基于AD9371射频集成芯片的多通道宽带同步采集系统2018-08-09 4765

-

一种FPGA高速数据采集卡的硬件设计2011-09-01 1032

-

1394卡与视频采集卡的区别2012-02-13 1871

-

基于FPGA_CPLD和USB技术的无损图像采集卡2016-06-07 1059

-

基于FPGA的图像数据采集卡及其驱动设计2016-08-29 838

-

如何使用DSP和FPGA进行高精度数据采集卡的设计资料说明2019-02-21 1670

-

如何使用FPGA实现图像数据采集卡及其驱动设计2021-02-03 1669

-

国产芯片替换进口stm32芯片,国产工业数据采集卡性价比高2022-03-18 7145

-

关于图像采集卡的一些基本知识2023-05-25 2619

-

基于国产RF-FPGA宽带射频采集卡2023-08-03 4787

-

AD采集卡设计方案:630-基于PCIe的高速模拟AD采集卡2023-12-25 1861

-

高速视频采集卡设计方案:620-基于PCIe的高速视频采集卡2024-01-05 1818

-

如何使用图像采集卡2024-12-13 2381

-

如何选择适合您需求的采集卡2024-12-23 1744

-

国产替代进口图像采集卡:机遇、挑战与策略2025-04-07 1273

全部0条评论

快来发表一下你的评论吧 !