基于FPGA的SRIO协议设计

描述

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

由于Vivado中RapidIO IP核需要付费才能使用,因此本文提供完整工程源码。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7K410T...;

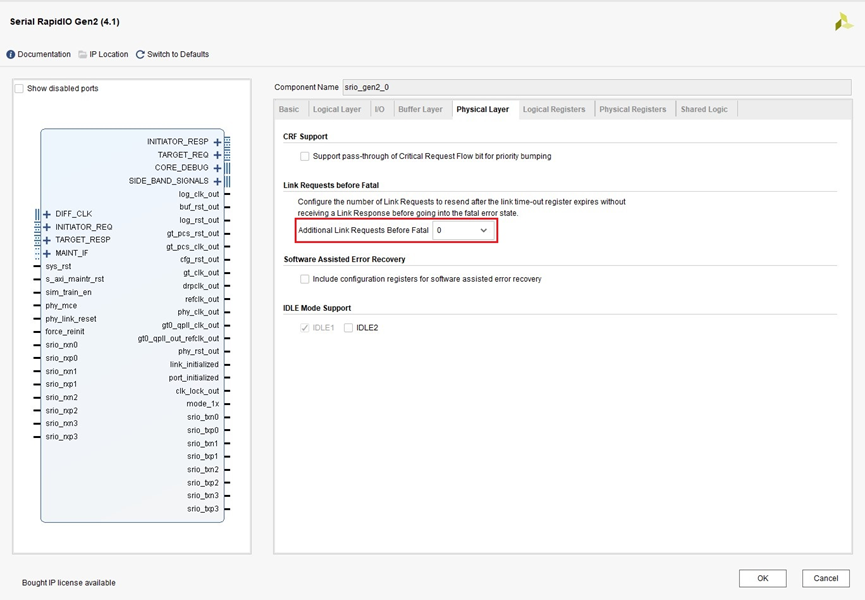

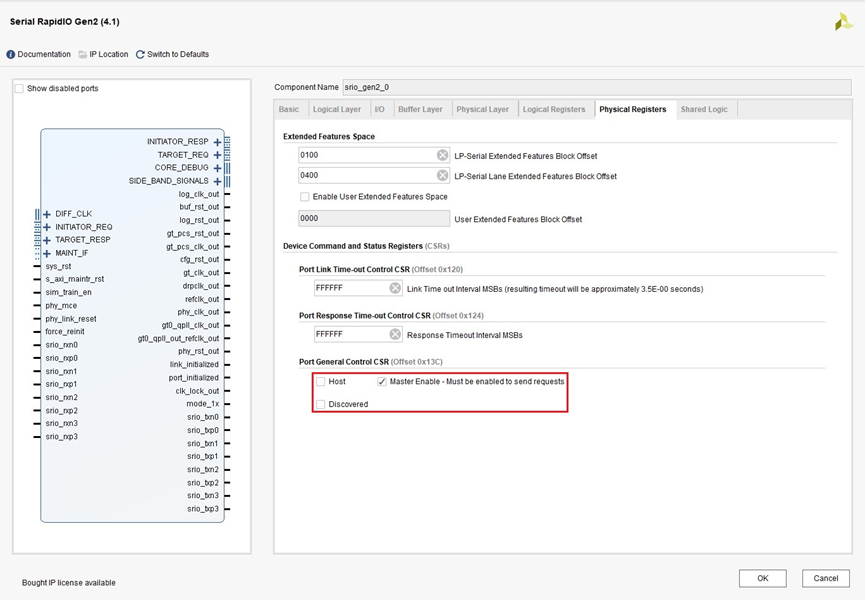

02IP核参数配置

本工程SRIO IP核参数配置如下图所示,仅供参考:

03工程源码结构

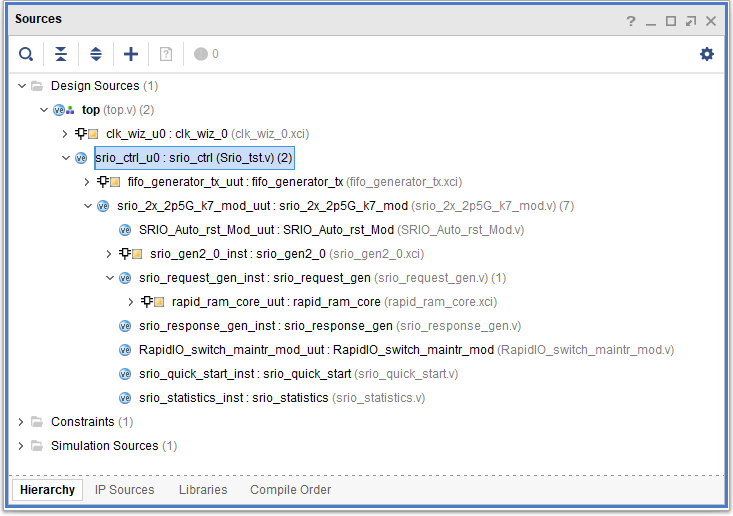

下图是SRIO工程源码结构:

其中,

- SRIO_Auto_rst_Mod:SRIO自动复位模块;

- srio_request_gen:SRIO请求事务生成模块;

- srio_response_gen:SRIO响应事务生成模块;

- RapidIO_switch_maintr_mod & srio_quick_start:SRIO维护事务生成模块。

04实现功能

该FPGA SRIO模块采用NWRITE类型事务往DSP目的地址传输数据,每包数据大小为256字节。数据写入完毕后,通过DOORBELL事务给DSP发送数据接收中断。另外FPGA端通过RapidIO IP核m_axis_treq接口接收来自DSP的数据。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何使用FPGA实现SRIO通信协议2025-11-12 6104

-

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释2024-12-10 5282

-

FPGA的SRIO接口使用应注意的事项2024-06-27 6542

-

FPGA与SRIO调试步骤2024-04-19 2917

-

srio交换芯片是什么?srio交换芯片的原理和作用2024-03-16 5928

-

FPGA优质开源模块-SRIO IP核的使用2023-12-12 4037

-

SRIO IP核的三层协议的作用解析2023-04-25 2797

-

在FPGA和DSP两种处理器之间实现SRIO协议的方法2023-03-20 4205

-

SRIO IP核的三层协议的作用?2023-03-03 1821

-

可用的SRIO RapidIO (SRIO)验证平台2022-11-08 3017

-

基于C66x+FPGA的SRIO开发视频教程2020-07-01 2505

-

srio协议将数据从我的模块发送到其他模块怎么实现?2020-04-30 2057

-

用SRIO实现DSP与FPGA通信2018-06-21 5809

-

基于SRIO协议的板级芯片互联技术2012-01-10 4704

全部0条评论

快来发表一下你的评论吧 !