基于FPGA搭建一个通用的图像处理平台

描述

本文介绍如何搭建一个通用的图像处理平台,采用HDMI接口进行输入、输出,可用于测试基于HLS的FPGA图像处理项目。

01硬件平台

Zynq-700 ARM/FPGA SoC开发板套件。

02操作步骤

概述

本文演示如何搭建一个简单的基于Xilinx FPGA的图像处理平台,可用于后续基于HLS(高层次综合)的项目,并且可以采用标准的OpenCV库辅助开发。

该项目采用Zybo Z7型号FPGA进行开发,该开发板上集成了HDMI输入输出接口,以及可以连接MIPI相机的CSI-2接口,便于后续开发使用。除了FPGA板卡外,还需要:1. HDMI相机;2. HDMI输入输出相关线缆;3. HDMI接口显示屏。

软件开发方面,采用:1. Vivado 2017.4;2. Xilinx SDK 2017.4;3. Digilent Vivado库。

创建该项目,需要准备以下工作:1. 下载并解压Digilent Vivado库;2. 配置Digilent 板卡参数;3. 新建Zybo-Z7型号Vivado block 工程。

创建工程

在Vivado block design中添加以下IP核:

- ZY NQ处理系统 (用于图像处理系统的配置核控制),PL时钟0设为200MHZ,PL时钟1设为100MHZ,启用HP0总线(用于和PS端DDR传输图像数据),启用GP0总线(用于系统参数配置)。

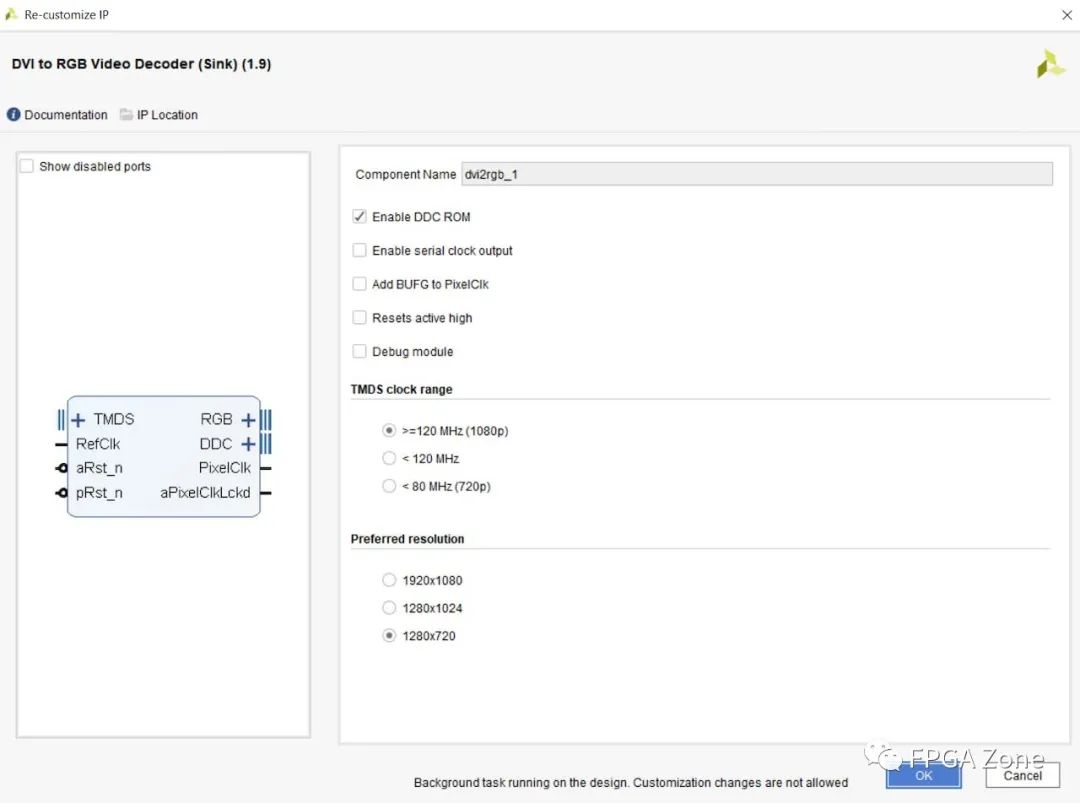

- DV I2RGB,将HDMI视频流转化为24位宽的RGB数据流。

图2 配置DVI2RGB IP核

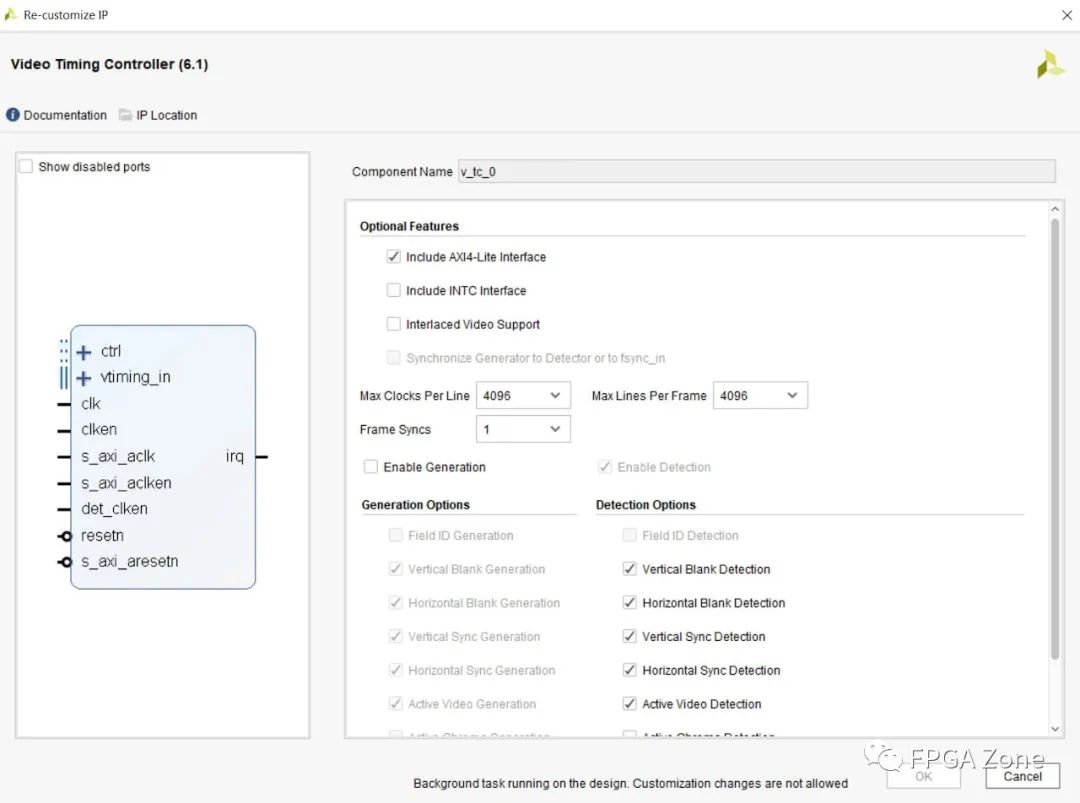

- Video Timing Controller,用于检测接收的HDMI视频模式。

图3 配置VTC IP核

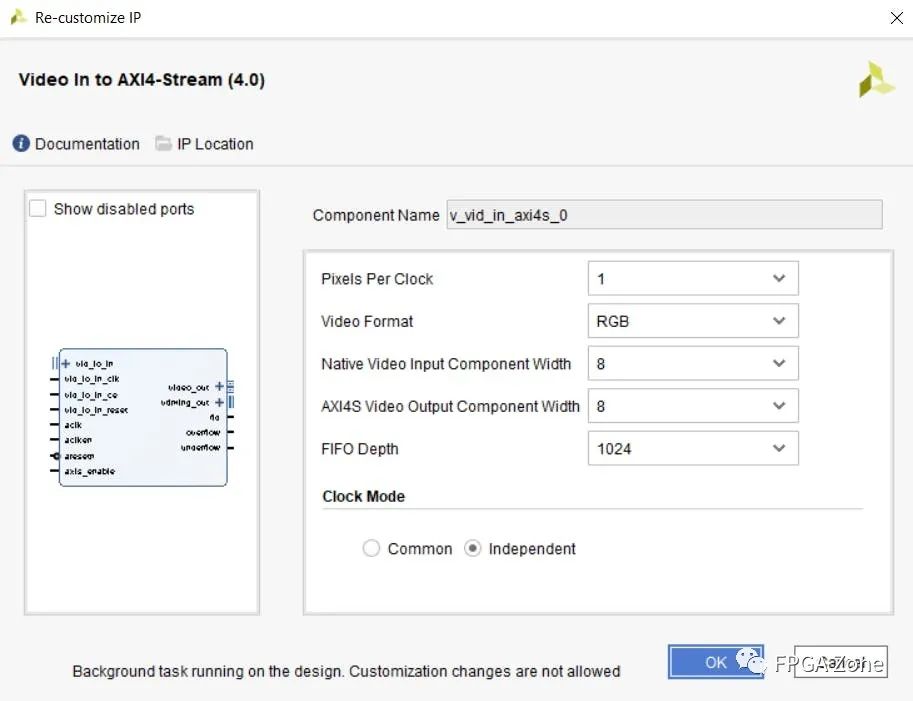

- Video In to AXI4-Stream,将视频数据转换为AXI数据流。

图4 配置VIA IP核

- AXI4-Stream Subset Converter ,将24位视频数据转换为RGB格式,分别在VDMA前后使用。

图5 配置AXI4-Stream Subset Converter IP

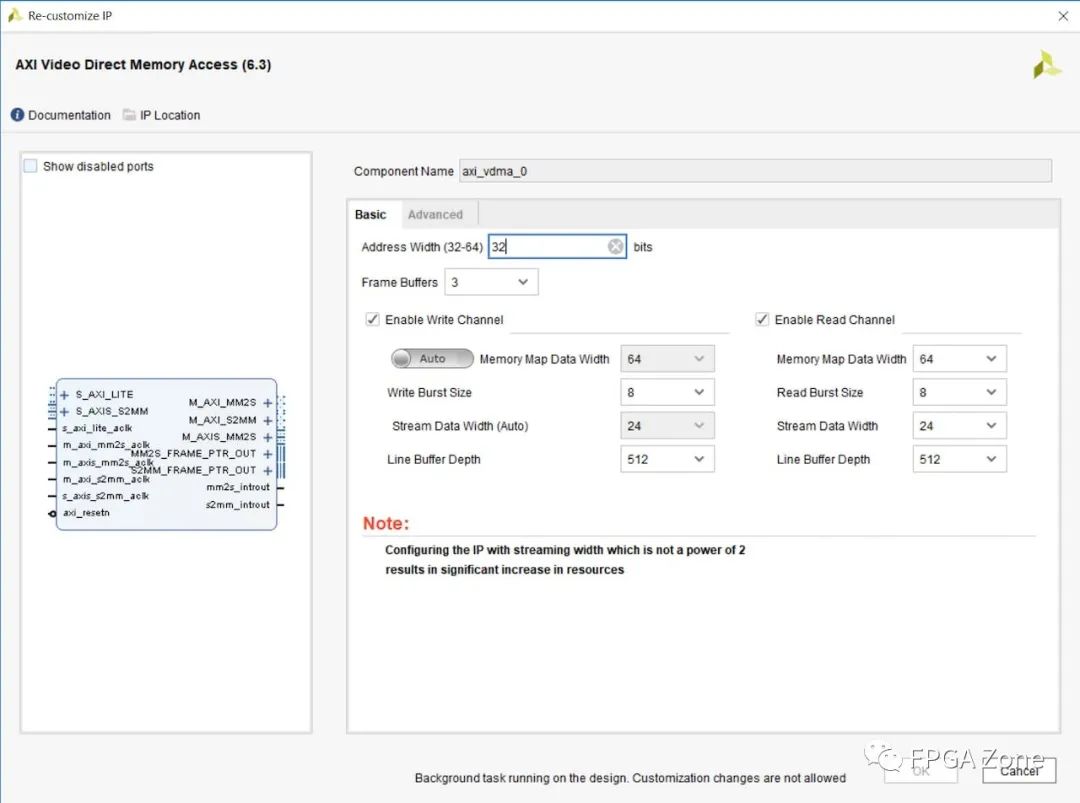

- VDMA ,配置如下:

图6 配置VDMA IP

- VTC,视频时序控制器配置如下:

图7 配置VTC IP

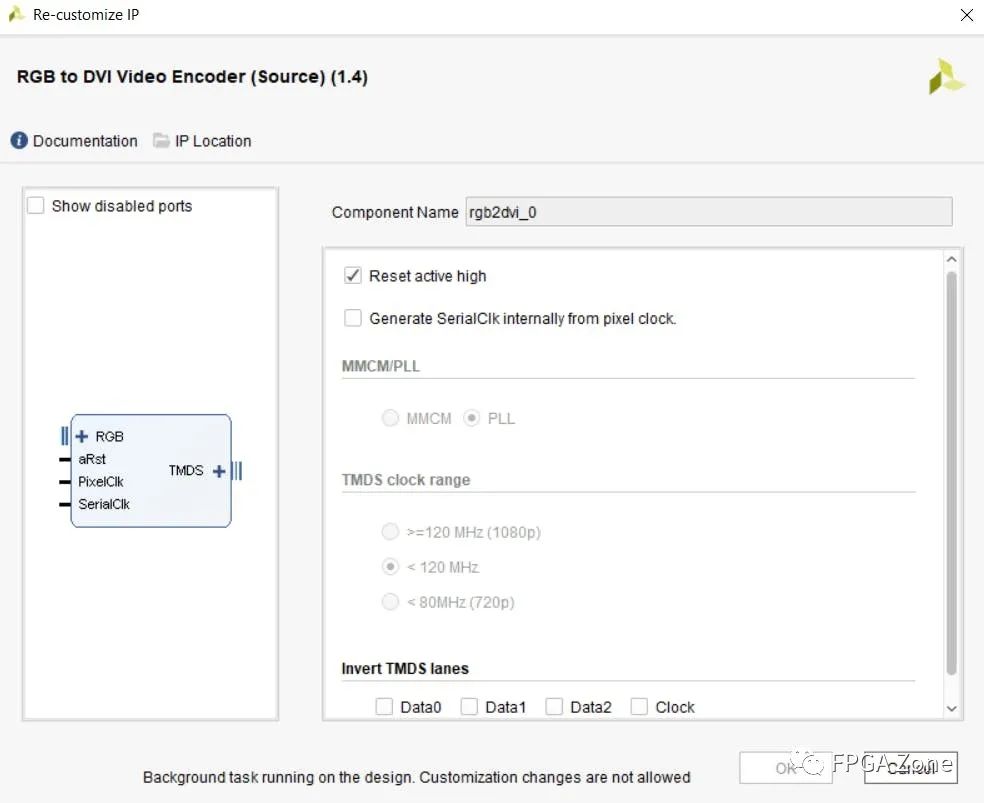

- RGB2DVI,用于将视频流转换为HDMI数据:

图8 配置RGB2DVI IP

完整Vivado工程

将上述IP组合在一起,完整Vivado工程如下图所示:

图9 完整工程框图

然后将上述工程导入Xilinx SDK中,以创建应用软件。软件里编写以下程序:1. 检测HDMI视频信号,2. 配置视频时序控制器,3. 配置VDMA从PS DDR读出和写入视频数据。

最后,运行上述写好的软件,可以看到相机采集的视频。

-

FPGA图像处理平台搭建方案2026-04-22 479

-

FPGA 实时信号处理应用 FPGA在图像处理中的优势2024-12-02 2908

-

基于FPGA的实时边缘检测系统设计,Sobel图像边缘检测,FPGA图像处理2024-05-24 3437

-

Vitis HLS图像处理平台搭建2022-11-21 2267

-

基于ARM与FPGA的嵌入式实时图像处理平台2021-07-30 1339

-

采用FPGA和通用DSP相结合实现视频图像采集系统的设计2020-07-28 1904

-

略谈FPGA图像处理2018-05-09 4690

-

一文详解FPGA的图像处理技术2018-05-06 8576

-

FPGA图像处理2016-12-14 1056

-

基于FPGA的图像采集与处理2016-03-04 1162

-

基于FPGA的高分辨率全景图像处理平台2015-11-04 773

-

实时图像边缘检测的设计及FPGA实现2011-12-22 596

-

基于FPGA的LCoS驱动和图像处理系统设计2011-06-28 2531

-

基于DSP和FPGA的通用图像处理平台设计2010-02-01 1762

全部0条评论

快来发表一下你的评论吧 !