FPGA数字图像显示原理与实现设计

可编程逻辑

描述

01

视频图像接口概述

视频图像经过数十年的发展,已形成了一系列的规范,以VGA和HDMI为主的视频图像接口协议也得到定义与推广。尽管DP、DVI、Type-C等图像接口技术近年来得到了推广与应用,且VGA传输性能发展逐渐落后于时代,但作为显示器和显卡等设备的通用显示接口,VGA和HDMI仍是当前主流的视频图像接口技术。

1.1 VGA视频接口

视频图形阵列(VGA,Video Graphics Array),也可称作D-Sub,是IBM于1987年提出的一个使用模拟信号的电脑显示标准,因此VGA传输信号为模拟信号,并且只能传输视频信号,不能传输音频信号。

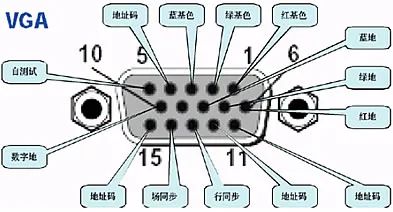

VGA接口共有15针,分成3排,每排5个孔,是显卡上应用最为广泛的接口类型,绝大多数显卡都带有此种接口。它传输红、绿、蓝模拟信号以及同步信号(水平和垂直信号)。

VGA各针脚定义如下:

VGA支持在640×480的较高分辨率下同时显示16种色彩或256种灰度,同时在320×240分辨率下可以同时显示256种颜色。使用VGA连接设备时,线缆长度通常不超过10米,而且要注意接头是否安装牢固,否则可能引起图像中出现虚影。

1.2 HDMI视频接口

高清晰度多媒体接口(High Definition Multimedia Interface,HDMI)是一种数字化视频/音频接口技术,是适合影像传输的专用型数字化接口,HDMI可同时传送音频和影音信号,且在信号传送前无需进行数/模或者模/数转换,是当前视音频主选接口。

HDMI自2002年提出以来,已发展到HDMI 2.1标准。该标准能够支持4K 120Hz、8K 60Hz以及高动态范围成像(HDR),能够针对场景或帧数进行优化,并向后兼容HDMI 2.0和HDMI 1.4,其中HDMI 1.4最高数据传输速度为10.2Gbps,HDMI 2.0最高数据传输速度为18Gbps。

HDMI在物理接口上主要包括以下几种类型:标准HDMI接口、mini HDMI接口和Micro HDMI接口。长距离传输通常线材较硬 ,采用标准HDMI接口以确保稳固连接;而小设备通常采用mini HDMI接口和Micro HDMI接口。

1.3 VGA与HDMI对比

VGA与HDMI的对比如下:

- VGA传输模拟信号,传输过程需要转换和缓存,存在一定损失;HDMI传输数字信号,数据需要无压缩,短距离无转换无损失;

- VGA仅支持视频传输;HDMI同时支持音频传输;

- VGA采用PC标准,色阶从0至255;HDMI采用TV标准,色阶默认从15至255;

- VGA在高分辨率下会存在失真虚化的问题;HDMI支持4K高清分辨率;

- VGA不存在兼容顾虑;HDMI在PC上兼容性一般,通常不支持三屏以上多屏显示。

随着数字图像的发展,VGA接口被淘汰已成为趋势,目前大部分新生产的PC和显示器设备都不再支持VGA接口。然而,由于VGA标准早期的影响较大,大量投影仪等设备仍采用VGA,因此VGA接口目前仍被大量使用。

02

图像显示时序分析

尽管HDMI接口为减少干扰、增强传输可靠性采用了TMDS编码,但其图像扫描的本质方法与VGA相同:通过行同步与场同步进行扫描控制。在设计过程中通常采用专用芯片(例如SIL9134 HDMI编码芯片与SIL9013 HDMI解码芯片)完成TMDS编码操作,因此掌握行同步与场同步的控制时序,就可以完成视频图像的显示。

2.1 图像显示时序

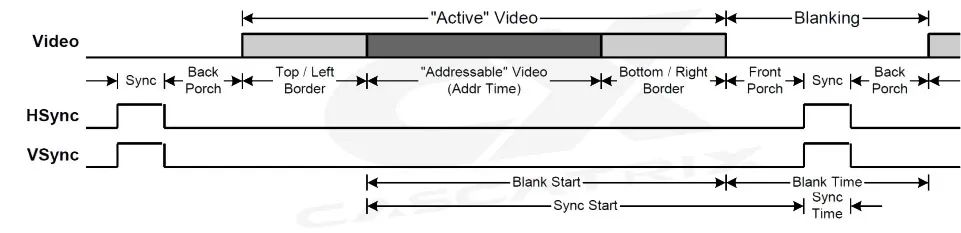

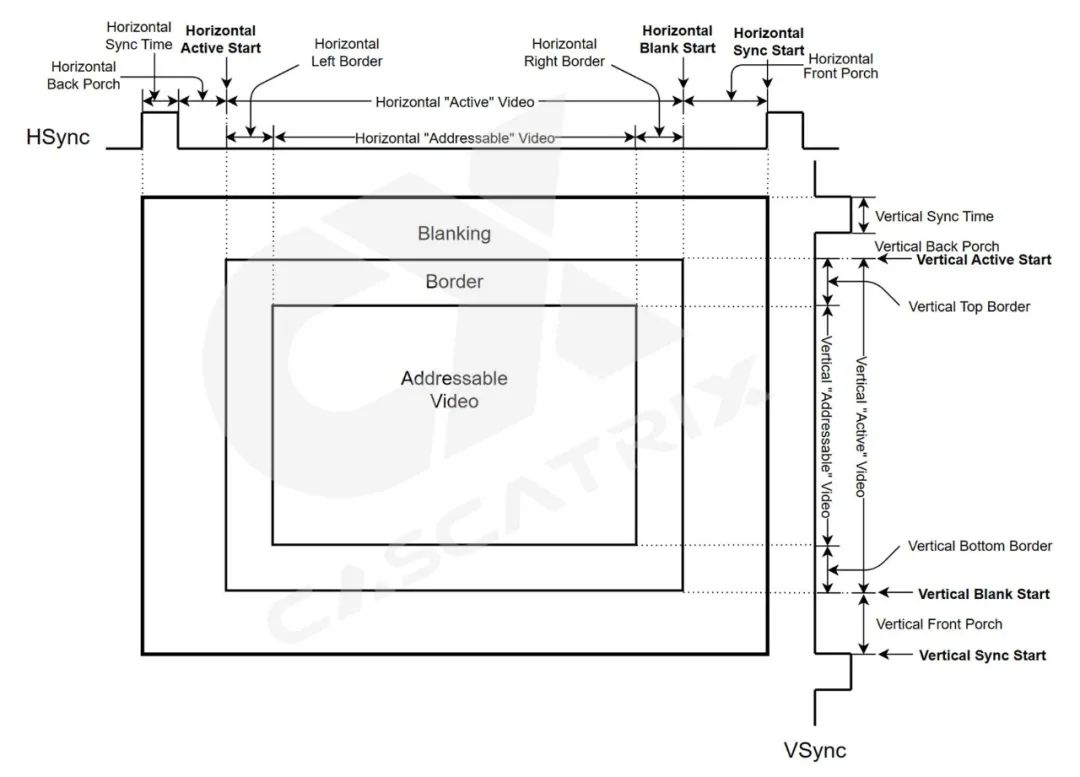

视频图像显示通常采用逐行扫描的方法:从屏幕左上方开始,从左向右逐点扫描。每行扫描完成时,用行同步信号HSYNC进行同步,电子束回到下一行最左侧起始位置,同时CRT对电子束进行行消隐;每帧所有行扫描完成时,用场同步信号VSYNC进行帧同步,电子束回到屏幕左上方,同时CRT对电子束进行进行场消隐,开始下一帧扫描。

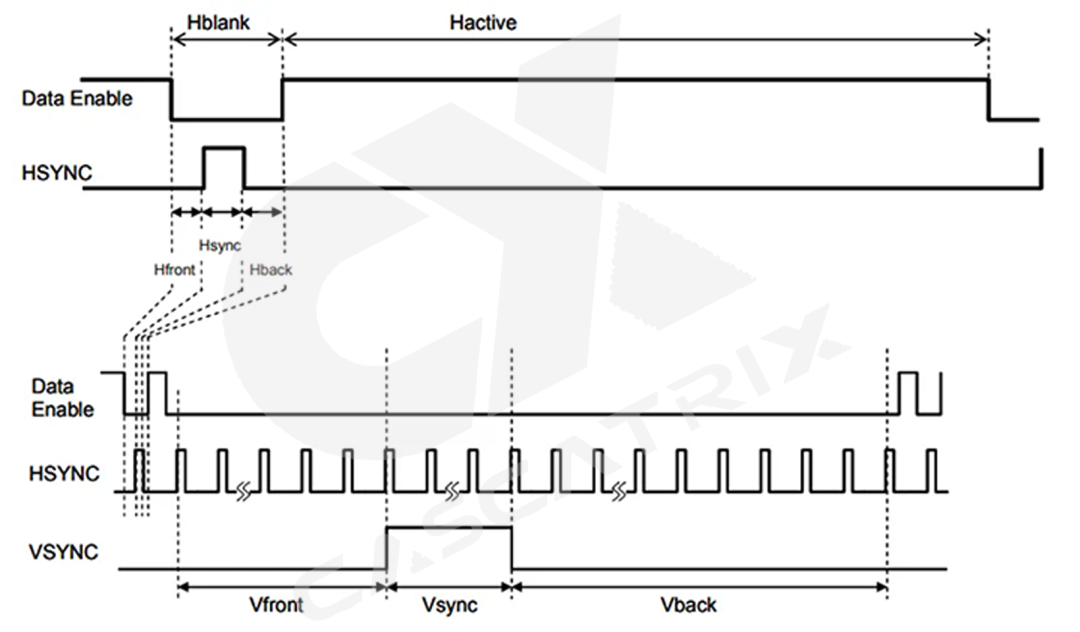

HSYNC为行同步信号(Horizontal Synchronization),低电平时完成图像行数据扫描,高电平时进行行同步;VSYNC为场同步信号(Vertical Synchronization),低电平时进行图像数据扫描,高电平时进行帧同步。

行同步信号HSYNC和场同步信号VSYNC均由四部分组成:Sync同步脉冲 + Back Porch消隐后肩时间 + Active Video数据有效时间 + Front Porch消隐前肩时间。

一幅图片的显示包括有效数据部分和消隐区部分,Blanking为图像的消隐区,Border和Addressable Video部分为图像的有效数据部分,在800×600及以上分辨率中Horizontal Left Border、Horizontal Right Border、Vertical Top Border、Vertical Bottom Border四个参数为0,即不存在Border区域。

行同步时序以像素为单位,场同步时序以行为单位。例如1920×1080分辨率的图像,行时序以每行1920个像素进行同步和有效传输,场时序以每帧1080行进行同步和有效传输。

2.2 不同分辨率显示参数

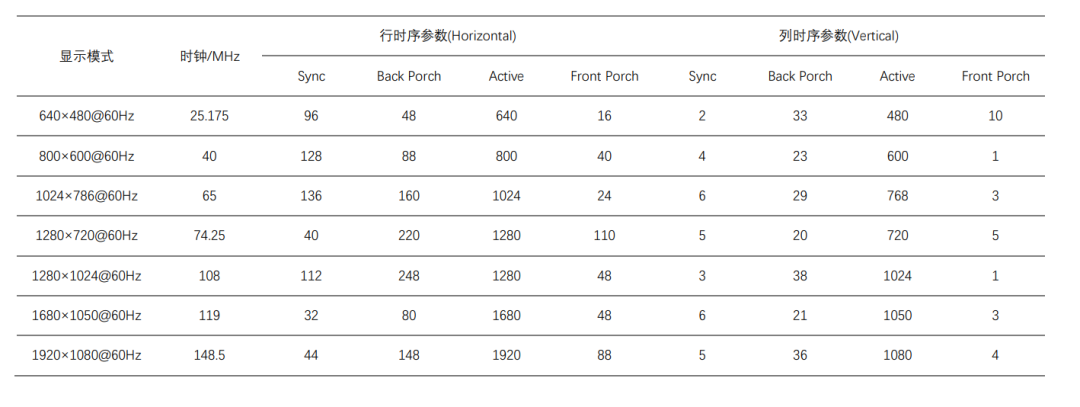

通过行场同步时序分析可知,对于图像分辨率为1920×1080@60Hz的图像显示,时钟传输频率并非仅考虑有效数据像素1920×1080×60=124.416MHz,而应当同时考虑有效数据和消隐区数据2200×1125×60=148.5MHz。

不同分辨率图像有效数据和消隐区像素分布如下:

03

图像显示代码实现

3.1 Verilog代码

通过HDMI接口显示图像信息,主要包括两部分:行场同步等信号生成模块与IIC配置TMDS编码芯片模块。由于IIC协议配置芯片寄存器实现方法已在IIC协议中介绍,所以这里给出不同分辨率下HDMI行场同步信号的生成代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Cascatrix

// Engineer: Carson

//

// Create Date: 2023/01/15

// Design Name: Image_Base

// Module Name: cx_image

// Tool Versions: v1.0

// Description: Image read and generate display parameters

//

//////////////////////////////////////////////////////////////////////////////////

`define PIXEL_1920_1080

//`define PIXEL_1680_1050

//`define PIXEL_1280_1024

//`define PIXEL_1280_720

//`define PIXEL_1024_768

//`define PIXEL_800_600

//`define PIXEL_640_480

module cx_image(

inputwireclk,

outputreghs,

outputregvs,

outputwireen,

outputwire [23:0]data

);

//1920x1080 148.5Mhz

`ifdef PIXEL_1920_1080

parameter H_ACTIVE = 1920;// 行数据有效时间

parameter H_FRONT_PORCH = 88; // 行消隐前肩时间

parameter H_SYNC_TIME = 44; // 行同步信号时间

parameter H_BACK_PORCH = 148; // 行消隐后肩时间

parameter V_ACTIVE = 1080;// 列数据有效时间

parameter V_FRONT_PORCH = 4; // 列消隐前肩时间

parameter V_SYNC_TIME = 5; // 列同步信号时间

parameter V_BACK_PORCH = 36; // 列消隐后肩时间

`endif

//1680x1050 119Mhz

`ifdef PIXEL_1680_1050

parameter H_ACTIVE = 1680;// 行数据有效时间

parameter H_FRONT_PORCH = 48; // 行消隐前肩时间

parameter H_SYNC_TIME = 32; // 行同步信号时间

parameter H_BACK_PORCH = 80; // 行消隐后肩时间

parameter V_ACTIVE = 1050;// 列数据有效时间

parameter V_FRONT_PORCH = 3; // 列消隐前肩时间

parameter V_SYNC_TIME = 6; // 列同步信号时间

parameter V_BACK_PORCH = 21; // 列消隐后肩时间

`endif

//1280x1024 108Mhz

`ifdef PIXEL_1280_1024

parameter H_ACTIVE = 1280;// 行数据有效时间

parameter H_FRONT_PORCH = 48; // 行消隐前肩时间

parameter H_SYNC_TIME = 112; // 行同步信号时间

parameter H_BACK_PORCH = 248; // 行消隐后肩时间

parameter V_ACTIVE = 1024;// 列数据有效时间

parameter V_FRONT_PORCH = 1; // 列消隐前肩时间

parameter V_SYNC_TIME = 3; // 列同步信号时间

parameter V_BACK_PORCH = 38; // 列消隐后肩时间

`endif

//1280X720 74.25MHZ

`ifdef PIXEL_1280_720

parameter H_ACTIVE = 1280;// 行数据有效时间

parameter H_FRONT_PORCH = 110; // 行消隐前肩时间

parameter H_SYNC_TIME = 40; // 行同步信号时间

parameter H_BACK_PORCH = 220; // 行消隐后肩时间

parameter V_ACTIVE = 720; // 列数据有效时间

parameter V_FRONT_PORCH = 5; // 列消隐前肩时间

parameter V_SYNC_TIME = 5; // 列同步信号时间

parameter V_BACK_PORCH = 20; // 列消隐后肩时间

`endif

//1024x768 65Mhz

`ifdef PIXEL_1024_768

parameter H_ACTIVE = 1024;// 行数据有效时间

parameter H_FRONT_PORCH = 24; // 行消隐前肩时间

parameter H_SYNC_TIME = 136; // 行同步信号时间

parameter H_BACK_PORCH = 160; // 行消隐后肩时间

parameter V_ACTIVE = 768; // 列数据有效时间

parameter V_FRONT_PORCH = 3; // 列消隐前肩时间

parameter V_SYNC_TIME = 6; // 列同步信号时间

parameter V_BACK_PORCH = 29; // 列消隐后肩时间

`endif

//800x600 40Mhz

`ifdef PIXEL_800_600

parameter H_ACTIVE = 800;// 行数据有效时间

parameter H_FRONT_PORCH = 40 ;// 行消隐前肩时间

parameter H_SYNC_TIME = 128;// 行同步信号时间

parameter H_BACK_PORCH = 88 ;// 行消隐后肩时间

parameter V_ACTIVE = 600;// 列数据有效时间

parameter V_FRONT_PORCH = 1 ;// 列消隐前肩时间

parameter V_SYNC_TIME = 4 ;// 列同步信号时间

parameter V_BACK_PORCH = 23 ;// 列消隐后肩时间

`endif

//640x480 25.175Mhz

`ifdef PIXEL_640_480

parameter H_ACTIVE = 640; // 行数据有效时间

parameter H_FRONT_PORCH = 16 ; // 行消隐前肩时间

parameter H_SYNC_TIME = 96 ; // 行同步信号时间

parameter H_BACK_PORCH = 48 ; // 行消隐后肩时间

parameter V_ACTIVE = 480; // 列数据有效时间

parameter V_FRONT_PORCH = 10 ; // 列消隐前肩时间

parameter V_SYNC_TIME = 2 ; // 列同步信号时间

parameter V_BACK_PORCH = 33 ; // 列消隐后肩时间

`endif

parameter H_TOTAL_TIME = H_ACTIVE + H_FRONT_PORCH + H_SYNC_TIME + H_BACK_PORCH;

parameter V_TOTAL_TIME = V_ACTIVE + V_FRONT_PORCH + V_SYNC_TIME + V_BACK_PORCH;

reg h_act;

reg v_act;

reg [12:0] h_syn_cnt;

reg [12:0] v_syn_cnt;

reg [31:0] image_cnt;

// 有效数据控制

assign en = h_act & v_act;

// 行扫描计数器

always@(posedge clk)

begin

if(h_syn_cnt == H_TOTAL_TIME - 1)

h_syn_cnt <= 13'b0;

else

h_syn_cnt <= h_syn_cnt + 1'b1;

end

// 列扫描计数器

always@(posedge clk)

begin

if(h_syn_cnt == H_TOTAL_TIME - 1)

begin

if(v_syn_cnt == V_TOTAL_TIME-1)

v_syn_cnt <= 13'b0;

else

v_syn_cnt <= v_syn_cnt + 1'b1;

end

end

// 行同步控制

always@(posedge clk)

begin

if(h_syn_cnt < H_SYNC_TIME)

hs <= 1'b0;

else

hs <= 1'b1;

end

// 场同步控制

always@(posedge clk)

begin

if(v_syn_cnt < V_SYNC_TIME)

vs <= 1'b0;

else

vs <= 1'b1;

end

// 行有效控制

always@(posedge clk)

begin

if(h_syn_cnt == H_SYNC_TIME + H_BACK_PORCH - 1)

h_act = 1'b1;

else if(h_syn_cnt == H_SYNC_TIME + H_BACK_PORCH + H_ACTIVE - 1)

h_act = 1'b0;

end

// 列有效控制

always@(posedge clk)

begin

if(v_syn_cnt == V_SYNC_TIME + V_BACK_PORCH - 1 && h_syn_cnt == 0)

v_act = 1'b1;

else if(v_syn_cnt == V_SYNC_TIME + V_BACK_PORCH + V_ACTIVE - 1 && h_syn_cnt == 0)

v_act = 1'b0;

end

// 像素数计数器

always@(posedge clk)

begin

if(image_cnt == H_ACTIVE*V_ACTIVE - 1)

image_cnt <= 'd0;

else if(h_act & v_act)

image_cnt <= image_cnt + 1;

end

// 图像像素值存储rom

rom_image inst_rom_image

(

.clk (clk),

.en (h_act & v_act),

.addr (image_cnt),

.dout (data)

);

endmodule

rom_image为图像像素数据存储模块,根据不同地址依次存入对应像素的像素值。该模块可通过Matlab生成,具体方法将在后续FPGA数字图像仿真中介绍。部分代码如下:

module rom_image

(

input clk,

input[31:0] addr,

input en,

output[23:0]dout

);

reg [23:0] DATA;

assigndout = DATA;

always@(*)

begin

if(en)

case(addr)

0 : DATA<=24'hB18D81;

1 : DATA<=24'h967266;

2 : DATA<=24'h987468;

...

2073597 : DATA<=24'hAE8070;

2073598 : DATA<=24'hAE8070;

2073599 : DATA<=24'hC79989;

default: DATA<= 0;

endcase

else

DATA <= 0;

end

endmodule

3.2 实现效果分析

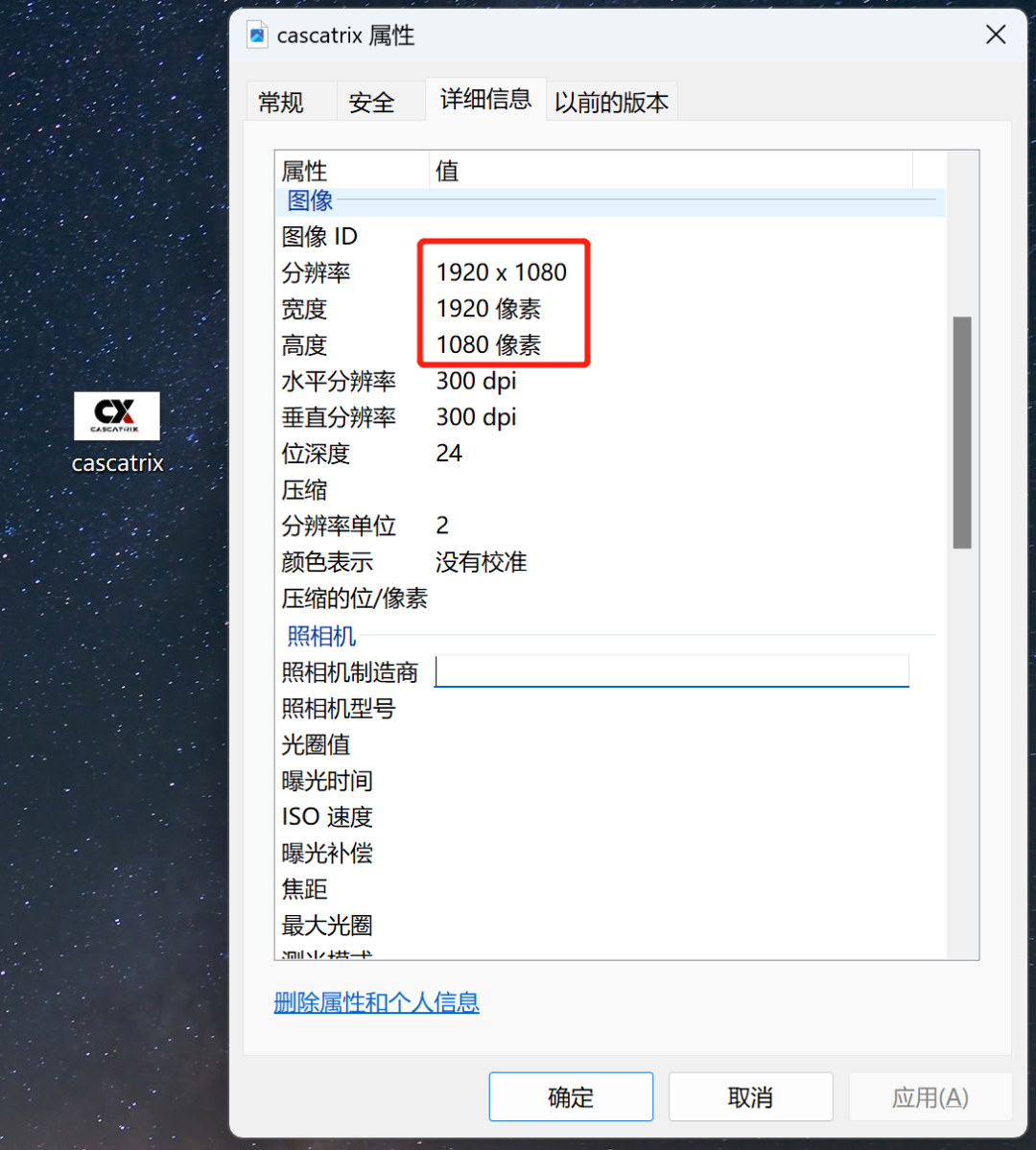

选择分辨率为1920×1080的图像:

-

FPGA数字图像处理的基础知识2023-09-06 2880

-

FPGA数字图像显示原理与实现(Verilog)2023-01-29 4818

-

怎么利用FPGA实现数字图像的空域滤波算法?2021-04-30 1522

-

【电子书】基于FPGA的数字图像处理2021-03-29 2634

-

基于FPGA的数字图像处理2017-03-05 10008

-

数字图像边缘检测的FPGA实现2016-01-04 822

-

有谁用FPGA做过数字图像直方图统计2013-08-21 3263

-

基于FPGA的数字图像处理中的边缘检测系统2013-06-26 6301

-

基于FPGA的B超数字图像实时采集系统2012-08-17 2849

-

数字图像空域滤波算法的FPGA设计2011-02-24 4342

-

RGB数字图像显示中错误图像分析2009-06-13 12793

-

基于FPGA 的数字图像显示系统2009-05-14 542

-

基于FPGA的数字图像显示系统2009-04-16 698

全部0条评论

快来发表一下你的评论吧 !