14条高速信号布局设计规则

电子说

描述

今天给大家分享的是:高速信号、14条高速信号布局设计规则。

在低频(<50 MHz)下,信号保持在数据特性限制范围内,并且电路板按预期运行。当速度增加时,阻抗不匹配串扰、反射、振铃和地弹问题会因更高频率的影响而出现,这些因素不仅影响系统的数字特性,还会影响系统的模拟特性。由于I/O 和内存接口的数据速率不断提高,上面说的这些问题很常见。但目前采用高速布局设计规则或者更好的PCB设计来避免吗这些问题。

一、什么是高速信号?

通常来说,频率高于50 MHz的信号被认为是高速信号。

理想情况下,时钟信号是方波,但实际上不可能立马就将一个“低”电平改为“高”电平,这里有一个特定上升和下降时间,因此在时域中看起来是一个梯形。

但需要注意的是频域中时钟信号较高的频率谐波的幅度取决于其上升和下降时间,如果上升时间较长,则谐波的幅度会变小。

二、高速布局设计规则是什么?

在高速PCB设计时,重点关注布局。下面介绍14个布局设计规则,不仅可以满足设计要求,还可以降低制造成本。

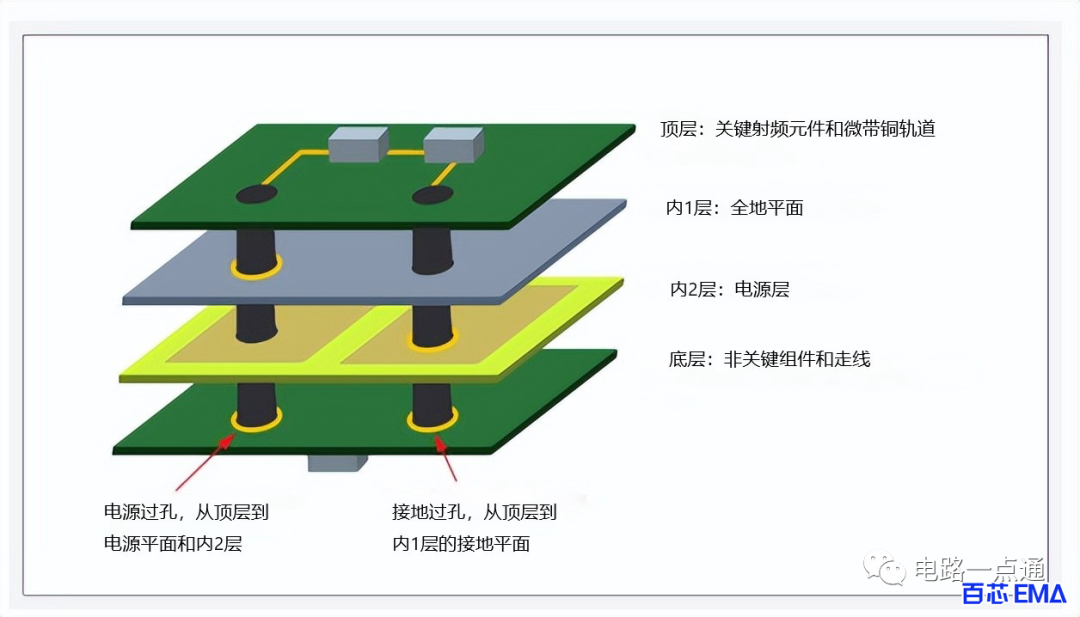

1、在信号走线下方放置一个公共接地层

这样可以确保电路板中任意2个接地点之间的阻抗最小,不应该通过布线其中的任何走线来破坏地平面。

信号走线下方的公共接地层

当需要在同一区域的电路板两侧布线走线时,就无法保证良好的接地层。在这种情况下,唯一的解决方案是在通过大量过孔互连的迹线两侧实现接地平面。

PCB两侧的布线轨道需要更多数量的过孔

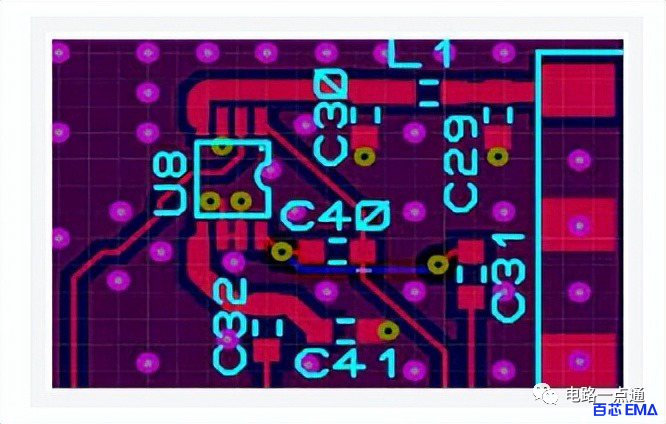

2、过孔放置

过孔定位不当会产生平面区域,其中过孔会阻挡电流流动或缩小铜空间,从而导致高电流密度,从而导致电压降,最好放置形成网格的过孔,在过孔之间留出足够的空间以包含电源平面。

通过放置发出信号

3、对称放置过孔以消除阻抗不连续性

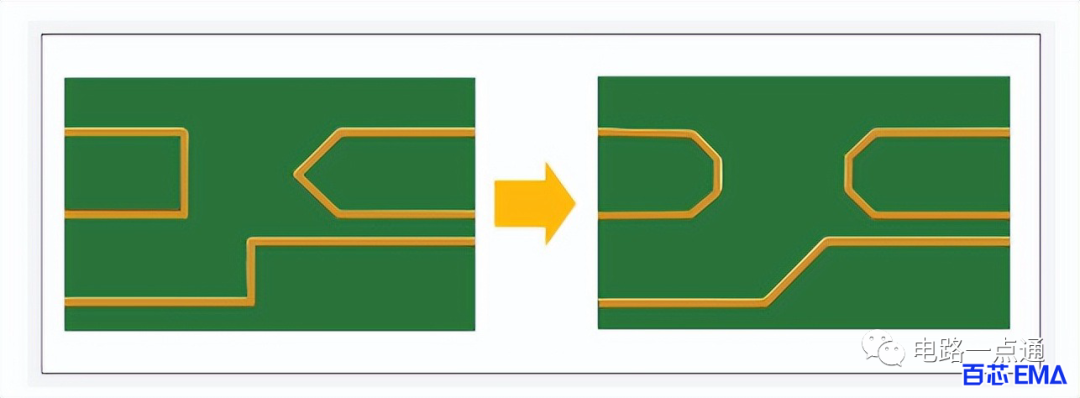

4、布线时保持最小弯曲

如果需要弯曲,则应实施135°弯曲,而不是如图 (左侧)所示的 90°。

布线时选择最小弯曲

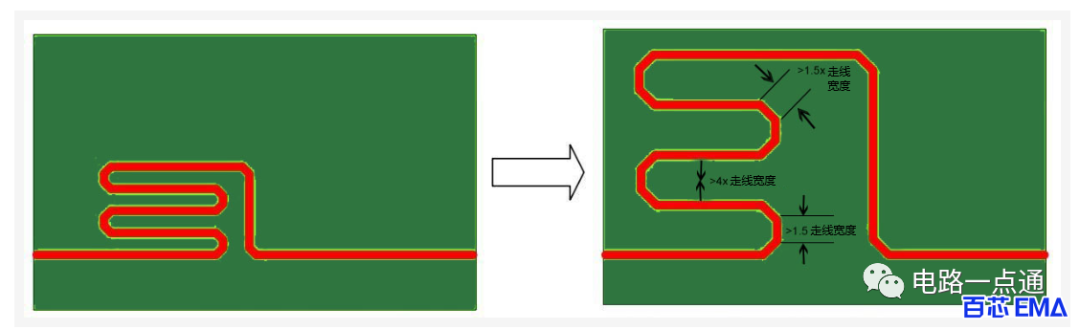

5、添加蛇形走线以实现特定的走线长度

特定长度的蛇形走线

6、在信号走线之间保持至少 3W 的间距

可以最大限度地减少串扰。

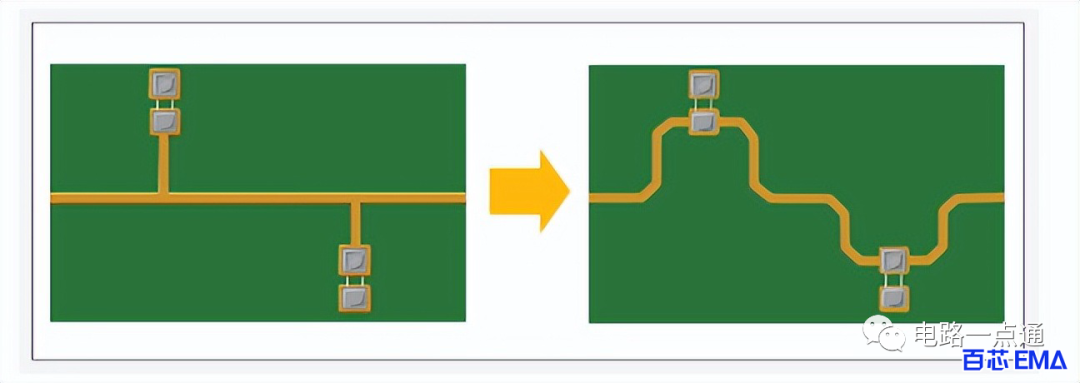

7、实施菊花链布线以避免长存根

长短截线可能会充当天线,从而增加 EMC 标准合规性问题。

长存根的菊花链布线

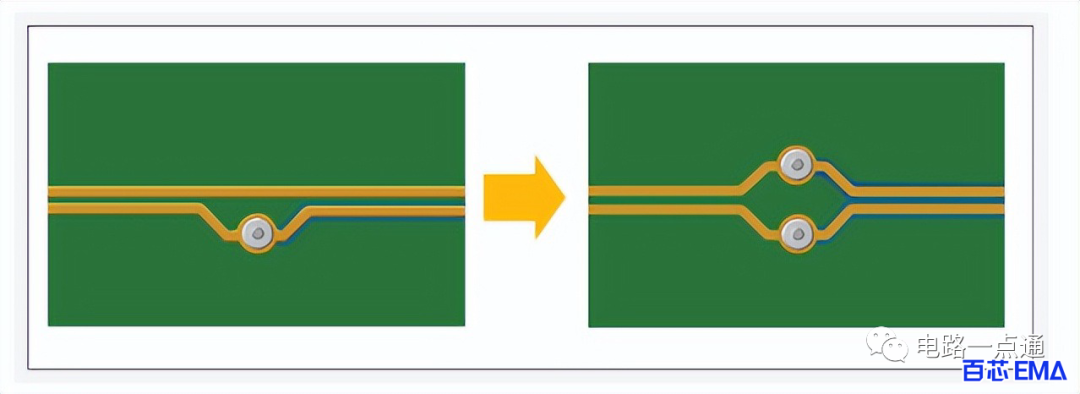

8、避免在差分对之间放置元器件和过孔

有助于减轻阻抗不连续性和EMI 问题

9、对称布置差分对并保持信号平行

10、差分对走线时,两条走线应走线在同一层它确保了阻抗要求的实现

在差分对中,走线应该在同一层上布线

11、使用蛇形线实现长度匹配

用来保持不同迹线和信号对之间到达目的地的时间 (时钟偏差)。

12、将蛇形走线放置在长度不匹配的位置

确保了正负信号分量通过连接同步传播。

13、在靠近弯曲处添加补偿,最大距离为 15 毫米

14、差分对连接的每一段中的失配应单独匹配

过孔用于将差分对分成两段,它可以通过过孔同步传播正信号和负信号。

在高速布局设计中,信号完整性和 EMC法规实施起着重要作用。

审核编辑:汤梓红

-

高速接口布局指南2023-04-14 1390

-

RF电路寄生信号布局的八条黄金规则2023-02-22 1630

-

PCB布局布线的规则2022-10-28 3500

-

元器件布局的10条规则2022-02-12 9435

-

10条布局规则+18条布线规则,让你画出美而高性能的板子2021-12-10 2123

-

使用高速转换器时有哪些PCB布局布线规则?2021-04-21 1857

-

关于PCB布局的布线规则:元器件布局的10条规则2020-12-31 6311

-

高速PCB信号走线规则概述2019-09-16 1715

-

PCB布局布线规则是什么2019-08-19 7527

-

高速信号的走线规则汇总2018-09-12 1835

-

降低RF-PCB电路布局寄生信号的8条规则2018-09-10 5039

-

PCB设计中元器件布局的10条规则,布线的规则是什么?2018-07-17 17536

-

设计规则13条:旁路电容设计指南2012-04-12 3957

-

高速信号走线规则教程2009-04-15 3282

全部0条评论

快来发表一下你的评论吧 !