FPGA设计中这两种情形该怎么约束

描述

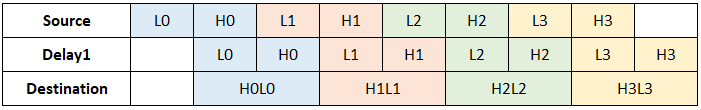

在FPGA设计中,我们经常会碰到这样的情形:从快时钟域到慢时钟域完成位宽转换,这时,这两个时钟是同步的。例如:源时钟是400MHz,数据位宽为4;目的时钟为200MHz,数据位宽为8,这样源时钟域和目的时钟域的吞吐率是一致的。这种位宽转换可直接通过寄存器采样实现,时序关系如下图所示。

图中Source为源时钟域(400MHz)4位数据,L0代码0号数据的低4位,H0代表0号数据的高4位,L1代表1号数据的低4位,H1代表1号数据的高4位,依此类推。Delay1为源时钟域经一级流水寄存器的输出结果。Destination为目的时钟域(200MHz)8位数据。

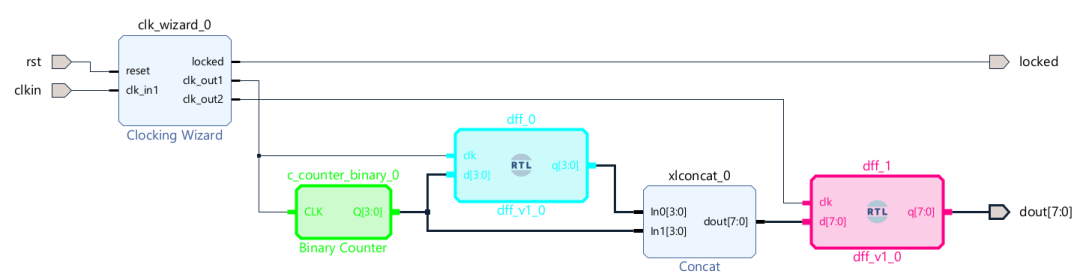

我们很容易搭建此电路,如下图所示。图中绿色计数器为400MHz时钟域计数器,产生源端4位数据,蓝色模块为源端流水寄存器,红色模块为目的端采样寄存器。

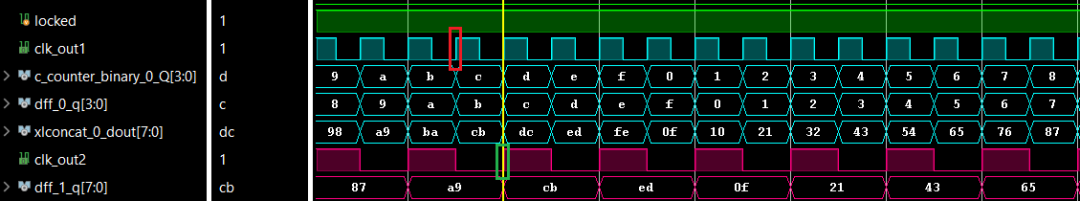

在这种情况下,能否使用多周期路径约束呢?这里我们看一下数据的发起沿和捕获沿的位置,如下图所示。图中红色方框为数据发起沿(400MHz),绿色方框(黄色标记线所在位置)为捕获沿,两者相差一个400MHz时钟对应的时钟周期。因此,并不满足多周期规则。这时,我们只用做常规的时钟周期约束即可,工具会自动将这里的跨时钟域按400MHz进行约束。

那么快时钟域到慢时钟域在什么情况下可以用多周期路径进行约束呢?本质上,多周期路径是指数据的采样率(SampleRate)是按慢时钟域的速率进行变化,其变化周期在慢时钟域是单周期(一个时钟周期变化一次),而在快时钟域是多周期(多个时钟周期变化一次)。满足这种情形就可以判断为多周期路径。

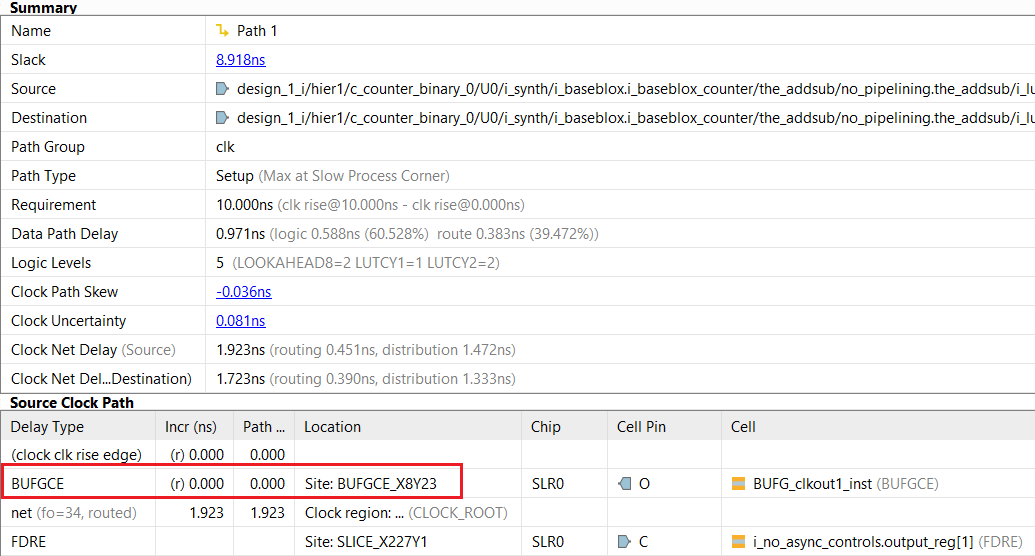

有时在设计中会有测试模块,或者出现这样的状况:模块1和模块2都工作在相同的时钟下,该时钟会根据设计的需要频率会发生变化,但无论怎么变化模块2只要满足最低时钟频率的要求即可。因此,这时可对模块2放松时序要求。只按照最低时钟频率约束即可。问题是只要定义了全局时钟(通过create_clock创建),该时钟就会在模块2中发生作用。如何覆盖这个约束呢?如果仍通过create_clock创建时钟,选项-period的值为时钟周期最大值(对应最低频率),但以模块2作为顶层,指定该约束针对的对象为模块2是否可行呢?答案是否定的,因为这时时序分析工具会把BUFG作为时钟的起点,而不是把全局时钟管脚作为起点。

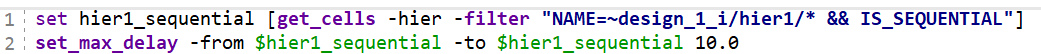

一种可行的方法是用set_max_delay,其对象是模块2内的所有时序单元(模块2内只有一个时钟),采用如下方式约束。第一条Tcl命令用于获取模块2内所有的时序单元。

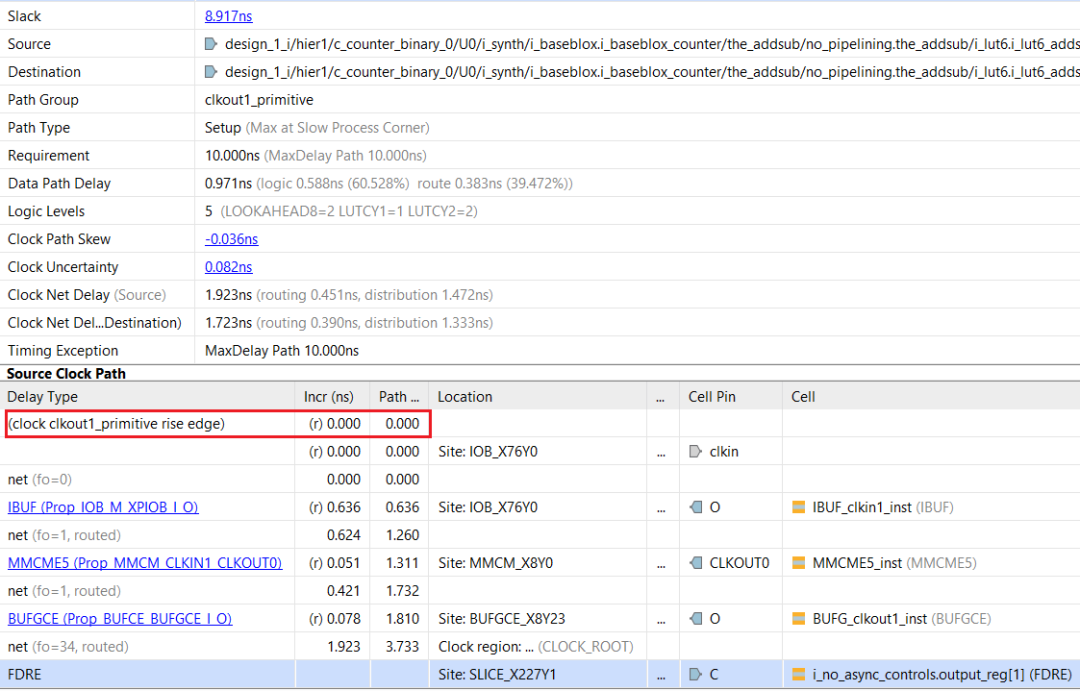

这时就可以看到时钟的起点是期望的位置了。这里可以看到set_max_delay的一个用法就是覆盖create_clock创建的约束。

审核编辑:汤梓红

-

常见的ARM架构分为两种一种是M系列另外一种是A系列,这两种有什么区别啊?2023-10-26 777

-

在MATLAB/simulink中建模时的两种不同实现方式2022-09-15 3109

-

如何使HDMI和VGA这两种接口互连?2021-05-11 17141

-

多路电子负载在这两种电源测试中的优势是什么2021-05-10 2021

-

FPGA设计中两种IO约束:管脚约束,延迟约束2020-10-30 17805

-

Vivado进行时序约束的两种方式2020-03-08 20719

-

FPGA时序约束分析余量2019-11-10 5417

-

为什么我的Altium中只有这两种模式?2019-09-09 1661

-

请问TPS74201和TPS74301这两种LDO的主要区别是什么?2019-07-16 3577

-

这两种放大电路有什么区别呢2019-07-06 4383

-

FPGA中的时序约束设计2017-11-17 3095

-

终于看懂了iic与spi这两种通讯协议了2017-11-02 178349

-

大家看看这两种电路接法对吗?哪个好点?2016-10-15 3963

-

蜂鸣器驱动电路,下面这两种有什么区别?2013-11-18 2500

全部0条评论

快来发表一下你的评论吧 !