异步复位寄存器的0时刻是如何进行赋值的呢?

电子说

1.4w人已加入

描述

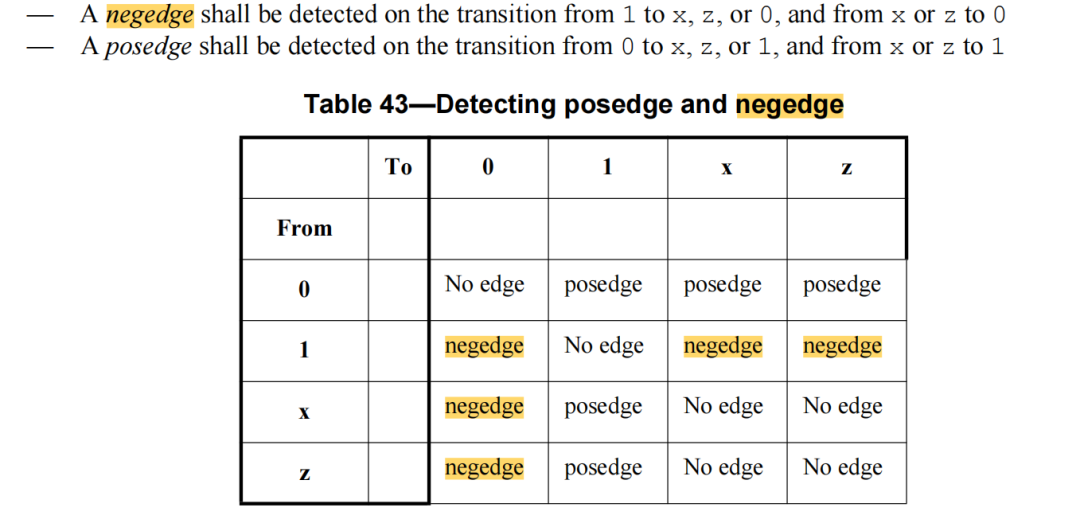

Verilog规范告诉我们:negedge 事件指的是如表43所示的跳变,发生negedge事件时才会执行操作。那么0时刻,是如何执行操作的呢?

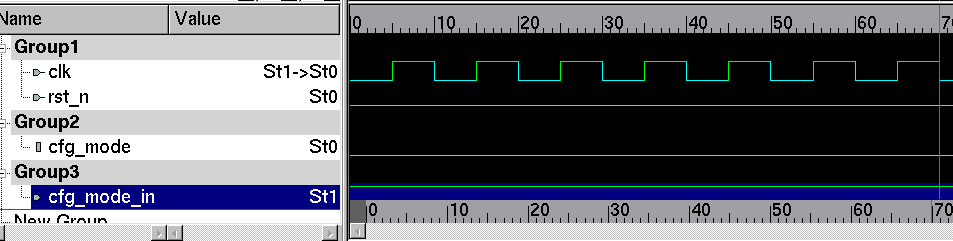

鸽子在Verilog标准中并没有找到0时刻赋值明确的说明。如下代码中,0时刻,rst_n为0,clk 处于低电平,那么cfg_mode的数值是多少呢?

always @(posedge clk or negedge rst_n)

if (!rst_n) begin

cfg_mode <= 1'b0;

end else begin

cfg_mode <= cfg_mode_in ;

end

实际电路中:

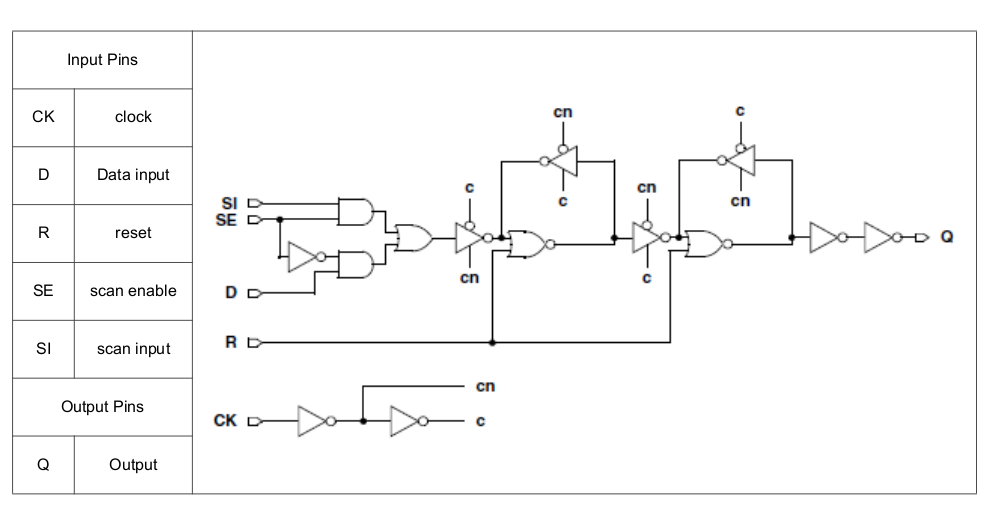

在芯片上电之前,芯片的chip_reset一直处于复位状态,因此导致芯片内部的rst_n一直为0,且芯片内部PLL还没有工作,也没有产生clk,此时没有任何信号的跳变,即clk没有跳变,rst_n一直为0也没有跳变。在实际电路中,从D触发器的结构图可以看到,当复位R一直是1时,即使时钟信号不跳变,Q端输出也是0。

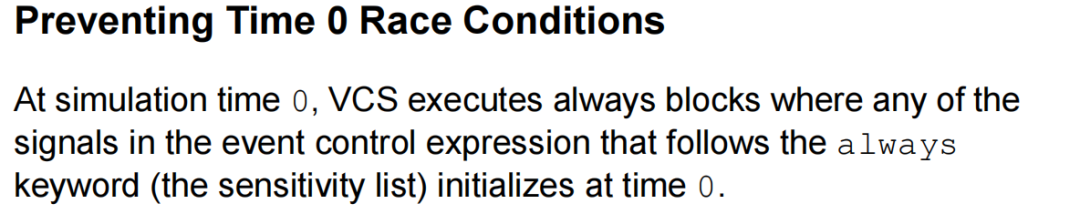

VCS在0时刻赋值

VCS 在0时刻会执行一次always块的赋值,而不是等到信号跳变。

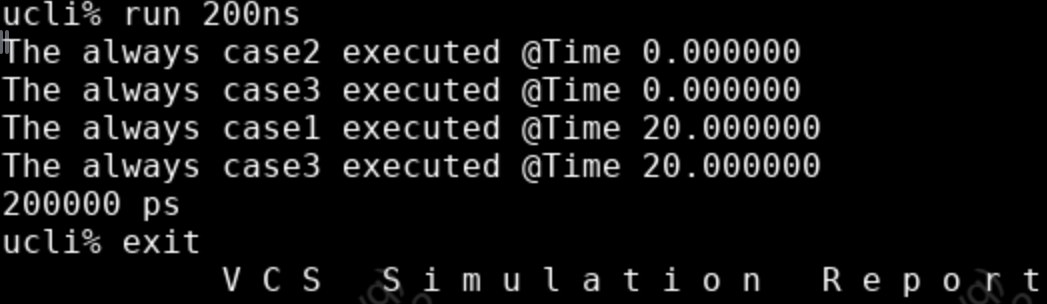

module zero_time_test;

reg rst_n;

initial begin

rst_n = 0;

#20 rst_n = 1;

end

always@(posedge rst_n) begin: always_case1

$display("The always case1 executed @Time %f", $time());

end

always@(negedge rst_n) begin: always_case2

$display("The always case2 executed @Time %f", $time());

end

always@(rst_n) begin: always_case3

$display("The always case3 executed @Time %f", $time());

end

endmodule

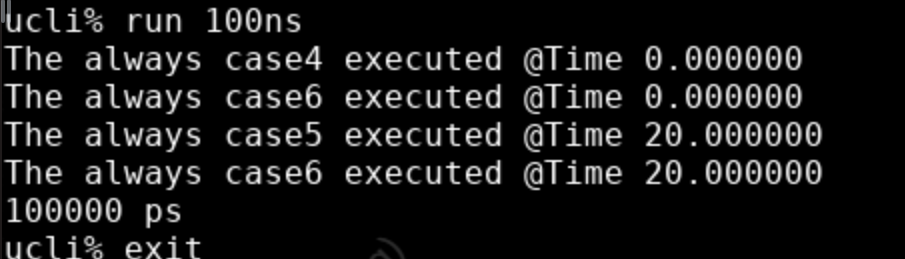

module zero_time_test;

reg rst_n;

initial begin

rst_n = 1;

#20 rst_n = 0;

end

always@(posedge rst_n) begin: always_case4

$display("The always case4 executed @Time %f", $time());

end

always@(negedge rst_n) begin: always_case5

$display("The always case5 executed @Time %f", $time());

end

always@(rst_n) begin: always_case6

$display("The always case6 executed @Time %f", $time());

end

endmodule

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析22025-10-14 901

-

对于多位的异步信号如何进行同步呢?2023-09-12 2396

-

异步复位同步释放问题解析2023-06-26 2510

-

常见的FPGA复位设计2023-05-14 3303

-

什么样的寄存器不需要复位呢?哪些寄存器是CPU能够访问的2022-07-08 13539

-

单片机如何给寄存器赋值呢2022-01-24 2353

-

配置STM32寄存器控制GPIO点亮LED2022-01-13 1150

-

Cortex-M3 内部寄存器2021-11-26 848

-

STM32复位来源(寄存器版)2020-03-14 13290

-

如何进行寄存器名称和地址的映射分析2019-06-21 1125

-

AD5410使用菊花链工作方式时,上电后如何进行软件复位和控制寄存器配置?2018-08-06 3095

-

简谈同步复位和异步复位2018-01-30 5791

-

寄存器reg延迟问题2014-11-14 14805

-

U0IIR寄存器原理下载2010-03-10 985

全部0条评论

快来发表一下你的评论吧 !