阈值电压对传播延迟和跃迁延迟的影响

电子说

1.4w人已加入

描述

阈值电压对传播延迟和跃迁延迟的影响:

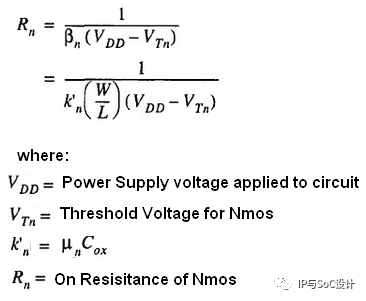

如果你能看到下面的方程式-我相信你可以很容易地弄清楚阈值电压对电池延迟的影响。(注:以下电阻公式是关于NMOS的。您也可以为PMOS导出类似的公式(只需将下标“n”替换为“p”)。

从上面的方程我们有以下几点

MOS的导通电阻与“VDD-VTn”(其中VTn是阈值电压)成反比。

对于恒定的VDD,减小阈值电压(低VTn)增加“VDD-VTn”。

增大“VDD-VTn”意味着减小“导通电阻”“ Rn.

减小Rn,则RC减小。

意味着大的驱动能力(源电流或吸收电流的能力)

减少对输出负载(电容)充电的时间(由驱动栅极的源极/漏极电容、导线的布线电容和驱动栅极的栅极电容组成)**

意味着“门A的输出转换时间”和“门B的输入转换时间”减少。

减少转换时间意味着减少传播时间。

所以我们可以说。。。

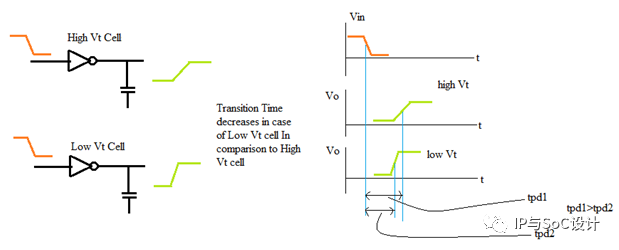

“使用低Vt单元可以减少延迟,但所付出的代价是高泄漏功率”

直接影响是低Vt单元通常更易泄漏,即泄漏功率增加。

如果你还有什么疑惑,下面的图应该能澄清你的疑惑。

我希望上面的图表可以消除你对阈值电压对延迟的影响的疑虑。

在下一篇文章中,我们将总结/列出所有修复设置和保持违规的方法。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MOSFET栅极阈值电压Vth2025-12-16 220

-

MOS管的阈值电压是什么2024-10-29 8583

-

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?2024-07-23 26138

-

浅谈影响MOSFET阈值电压的因素2024-05-30 7299

-

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?2024-03-27 8040

-

IGBT中的MOS器件电压、电流与阈值电压之间的关系2023-11-29 5513

-

影响MOSFET阈值电压的因素2023-09-17 17367

-

EDA探索之控制阈值电压2023-02-09 2565

-

影响比较器传播延迟测量的参数2023-01-08 5280

-

allegro软件的绝对传输延迟是什么,绝对传输延迟应该怎么设置呢?2020-04-15 4989

-

导线的传播延迟与其周围介质关系2019-05-21 2746

-

MOS管阈值电压的问题2018-11-15 14194

-

解答74HC14中正向阈值电压和负向阈值电压是什么/电压为多少2018-10-24 19697

-

阈值电压的计算2017-11-27 75282

全部0条评论

快来发表一下你的评论吧 !