XILINX FPGA IP之FIFO Generator

描述

在数字设计中,fifo是数据操作任务所需的普遍结构,如跨时钟域、低延迟内存缓冲和总线宽度转换。

XILINX FIFO Generator IP生成先进先出(FIFO)存储器队列,特别适于需要按次序进行数据存储和检索的应用。该IP为 FIFO 配置提供优化的解决方案,使用少量资源实现最高的性能(高达 500MHz)。用户可自定义:宽度、深度、状态标志、存储器类型以及读写端口长宽比等。

该IP的主要特性为:

- FIFO 深度可达 4,194,304 个字

- 原生 FIFO 配置支持从 1 到 1,024 位的 FIFO 数据宽度,而 AXI FIFO 配置的该数据宽度则高达 4,096 位

- 非对称长宽比(读写端口比可从 1:8 到 8:1)

- 支持独立或通用时钟域

- 可选存储器类型(Block RAM、分布式 RAM、移位寄存器或内建 FIFO)

- 原生接口或 AXI 接口(AXI4、AXI4-Lite 或 AXI4-Stream)

- 同步或异步复位选项

- 支持数据包模式

- 支持纠错 (ECC) 和注入特性,适用于特定配置

- 支持首字直接通过 (FWFT)

- 支持嵌入式寄存器选项,适用于基于 Block RAM 和内建 FIFO 原语的实现方案

- 支持 — 空/满、基本空/满和可编程空/满信号

原始接口下该IP的接口为:

AXI 接口派生自本来接口fifo,因此它们之间的许多行为是共同的。ready信号是基于FIFO中空间的可用性生成的,并且 保持高位以允许对FIFO进行写操作。只有在FIFO中没有剩余空间来执行额外的写操作时,ready信号才会被拉低。根据FIFO中数据的可用性生成vaild信号,并保持高电平以允许从 FIFO执行读取。只有当没有数据可从 FIFO读取时,vaild信号才被拉低。AXI接口如下图:

将information信号映射到Native 接口fifo的din和dout总线上。AXI FIFO的宽度是通过连接AXI接口的所有information信号来确定的。information信号包括所有的AXI 信号,除了有效的和准备好的握手信号。

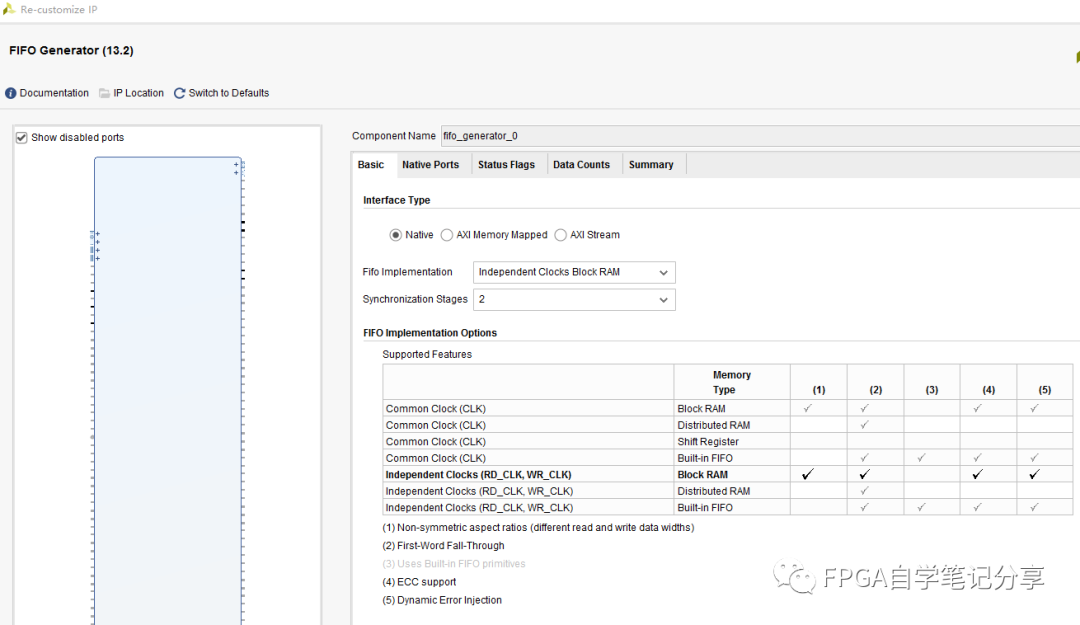

XILINX FIFO Generator IP支持Block RAM、分布式 RAM、移位寄存器或内建 FIFO,每种ram够成特性如下:

在ip的gui界面上同样有上述信息的详细描述如下图,在实际使用时根据需要使用的特性,选择一种合适的底层资源即可。

FPGA使用FIFO最常用的就是跨时钟域处理,处理流程如下图。写时钟域,根据限写使能wr_en产生写数据计数器然后将其转换为gray码,多bit跨时钟域到读侧。读时钟域,根据限读使能rd_en产生读数据计数器然后将其转换为gray码,多bit跨时钟域到读侧。读侧根据自己时钟域产生的读计数器和跨时钟域过来的写计数器值,得到fifo内的数据量,从而产生相应的empty/almost empty/prog empty/rd_data_count.写侧根据自己时钟域产生的写计数器和跨时钟域过来的读计数器值,得到fifo内的数据量,从而产生相应的full/almost full/prog full/wr_data_count.

-

智多晶FIFO_Generator IP介绍2025-04-25 2008

-

FIFO Generator的Xilinx官方手册2024-11-12 3152

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 5615

-

Xilinx FPGA IP之Block Memory Generator功能概述2023-11-14 5096

-

XILINX FPGA IP之FIFO Generator例化仿真2023-09-07 3696

-

XILINX FPGA IP之Clocking Wizard详解2023-06-12 9377

-

FPGA零基础学习:IP CORE 之 FIFO设计2023-03-15 980

-

利用XILINX提供的FIFO IP进行读写测试2022-02-08 4873

-

【正点原子FPGA连载】第十三章IP核之FIFO实验-领航者ZYNQ之FPGA开发指南2020-09-23 2389

-

Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置2016-03-09 4295

-

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置2016-02-29 4808

-

Xilinx FPGA无痛入门,海量教程免费下载2015-07-22 11668

-

Xilinx FIFO IP 使用2013-05-11 10812

全部0条评论

快来发表一下你的评论吧 !