堆叠式DRAM存储节点相关部分的结构分析

存储技术

描述

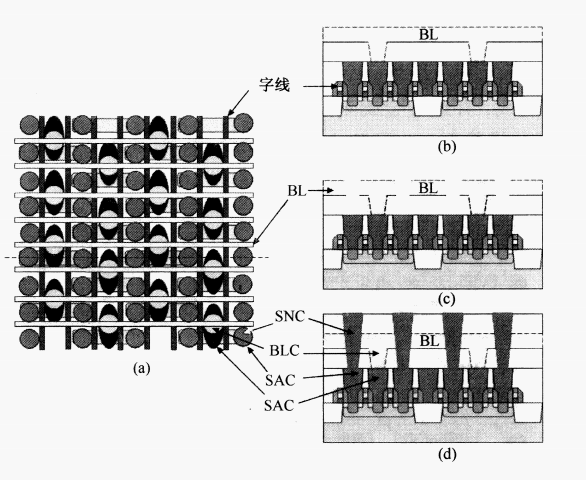

在下面的图中显示了堆叠式DRAM存储节点相关部分的结构图。下图(a)显示了堆叠式DRAM存储节点接触(SNC)结构。在图中我们可以较为清楚的看出来,SNC孔通过SAC栓塞与AA阵列的两个侧面连接。导电的栓塞可以通过多晶硅或钨形成,这哥形成的技术选择与技术节点有关。

通常在导电层沉积前,需要沉积一层氮化硅并回刻蚀在SNC孔的侧壁上形成衬垫,采用了这种方式之后,从而可以防止位线到导电栓塞的短路。

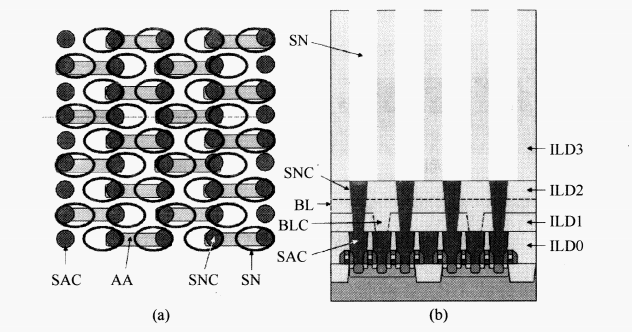

下图(a)显示了存储节点的版图设计图纸,这里需要进行一些细致的说明,下图(b)为沿下图(a)所示虚线的SN孔横截面图。可以看出,SN孔与SNC栓塞连接,其中SNC栓塞是通过在SAC之上的方式来与AA阵列的两个侧面连接,而不是直接进行连接。

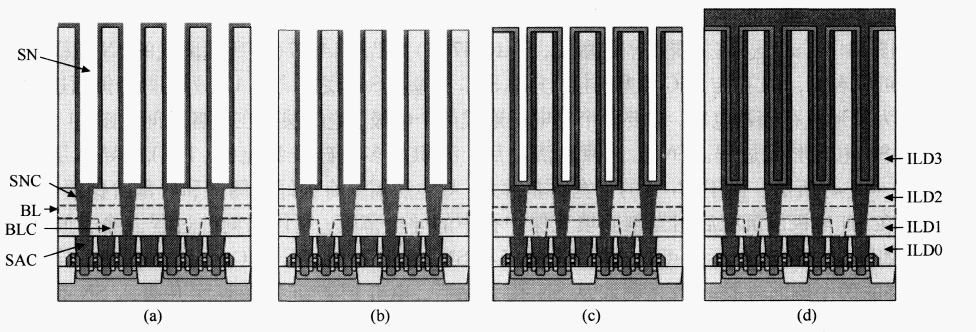

为了形成存储器电容,首先需要两个导电层作为电容的上下极板,然后通过在两个导电层上面分别接上电源的正负极形成两个电极,绝缘层夹在两者之间,以作为电容的填充电容。下图显示了SN电容形成过程。SN孔刻蚀和清洗后,沉积如多晶硅或氮化钛(TiN)的导体层,如下图(a)所示。由于SN孔的长宽比非常大,导电层需要有很好的侧壁和底部阶梯覆盖性。

通常在SN电极层沉积后用光刻胶填充保护孔中的导电薄膜,利用回刻蚀过程去除表面导电膜,如下图(b)所示。可以看出SN电极与SNC栓塞连接,而SNC栓塞通过SAC栓塞与AA层的两个侧面连接。当光刻胶从SN孔去除后,电介层被沉积在表面并进入SN孔,如下图(c)所示。

为了形成具有这种特性的电容的电介质,需要侧壁和底部的阶梯覆盖具有统一性,因而这两者必须采用一定的工艺来保证统一性。。下图(d)为导体沉积形成SN电容的接地电极。该导电层将在下一次光刻过程中从外围区域去除,从而就完成了DRAM器件的一部分工艺,并开始BEoL互连后端工艺。

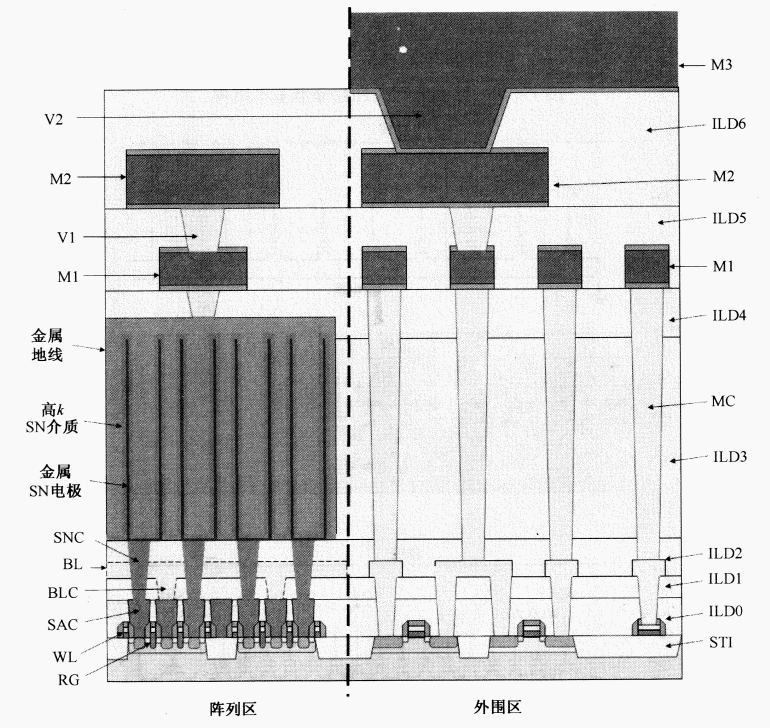

随着技术节点的缩小,SN孔的尺寸变得更小。为了获得30pFSN电容以保存足够的电荷存储数据,当电容结构和介质材料不变的情况下,必须增加SN孔的深宽比。为了减小SN孔的深宽比,人们已经开发了许多技术。使用高电介质可以减少SN孔的高度和深宽比。之前使用二氧化硅、氮化硅和氧化硅叠层。如氧化铝(A12O3)、二氧化合(HfO2)和二氧锆^(ZrO2)等高k材料已经用于SN电容。

其他减小SN孔高度的方法是减少SN电极形成后的ILD3,这样可以在SN电极的两边形成接地电极。之前多晶硅作为电极材料被广泛使用,而先进的DRAM芯片开始使用TiN作为SN电极。下图显示了新型堆叠式DRAM结构,其中晶体管阵列具有凹栅(RG)结构,使用TiN作为SN电极,凹型ILD3,高电介质层,三层金属互连接地电极。凹栅(RG)结构用于降低NMOS晶体管阵列的短通道效应(SCE),因为当特征尺寸缩小时这种效应变得严重。

审核编辑:刘清

-

堆叠式DRAM单元STI和阱区形成工艺介绍2023-09-04 7033

-

浅析动态随机存储器DRAM集成工艺2023-02-08 1598

-

美光出货全球最先进的1β技术节点DRAM2022-11-02 1773

-

DRAM原理 - 1.存储单元阵列#DRAMEE_Voky 2022-06-28

-

DRAM芯片中的记忆单元分析2022-03-02 2538

-

嵌入式系统存储的相关资料推荐2021-12-22 672

-

存储器的层次结构及其分类2021-07-29 1428

-

DRAM、NAND和嵌入式存储器技术的观察与分析2020-12-24 1923

-

DRAM存储原理和特点2020-12-10 5342

-

元器件堆叠封装结构2018-09-07 2924

-

配备DRAM的三层堆叠式CMOS影像传感器介绍2018-04-28 13489

-

FPGA读写DRAM存储器的代码2018-01-14 8511

-

基于再生码的分布式存储节点修复优化2017-12-26 1317

-

基于当代DRAM结构的存储器控制器设计2009-12-31 1095

全部0条评论

快来发表一下你的评论吧 !