同轴线互连传感器CS抗扰度布置分析

MEMS/传感技术

描述

0. 引言

某工业用便携式流速检测仪在进行CS(传导抗扰度)实验时,电流表检测读数超允许误差范围,电流表检测精度为uA级,为整改带来了难度,以下为实际案例经验分享,希望对大家有帮助和启发。

1. 组网与测试配置

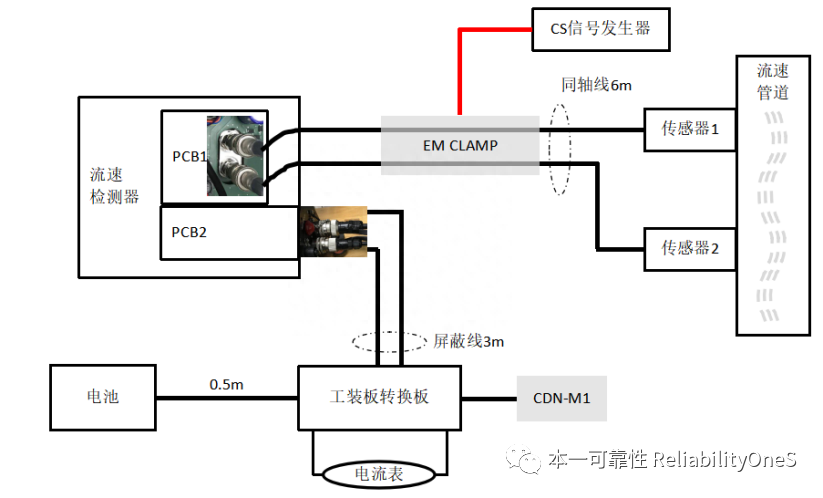

流速检测仪为两通道输入输出,传感器输入采用同轴线,输出线缆为屏蔽线缆,供电DC15V ,传感器同轴线长度约为6m,输出屏蔽线长度约为3m,详见图1组网测试配置图。

图1 组网测试配置图

2. CS测试问题描述

- 测试等级:3V,150KHz-80MHZ;

- 测试线缆:传感器同轴线缆;

- 测试问题:10MHZ-20MHz左右频点实验时,电流表读数出现飘偏,允许误差±30uA,测试时偏差达到了上飘到50uA。

3. CS测试布置

3.1 测试波形

测试等级为3V,是指Urms为3V,实际测试波形为1KHz正玄波,80%调制后的Upp达到了15.27V。调制前后波形参见图2.

3.2 测试原理与布局

根据IEC 61000-4-6标准要求,测试应该尽量保证被测对象处于300Ω阻抗环路中,以保证测试合规性与一致性。测试原理参见图3。

标准推荐布局应该参照图4进行。与流速测试仪的实际组网图1对比可知,实验测试只有一个CDN,缺少对被测线缆路径的300Ω控制。

流速测试仪的测试布局严格来讲是不满足标准要求,在此不进行过多的讲述,后续实验在当前的测试布局下进行分析。图5中为标准对测试阻抗要求说明。

4. 问题分析

CS测试实际上是电场和磁场的耦合,但电磁场的分析过于复杂,将场转化成路的分析比较简单和高效。

4.1 噪声路径分析

CS信号发生器将干扰信号注入到EM clamp中,EM clamp通过电场和磁场耦合到被测线缆中。同轴线缆耦合的干扰,通过同轴线及分布电容回流。噪声回路参见图6所示。

4.2 敏感设备

经过排查分析,确认敏感设备为传感器,CS注入的干扰,使得传感器信号受到了干扰而产生了波动,特别是经过了经过长距离传输后,PCB1板中接受的信号质量很差,导致超过允差范围。

工程师整改方法:

- 在传感器侧加滤波电容,使得传感器信号质量得到保证,但无法落地;

- 在PCB1侧加滤波电容,没有效果,主要受干扰的信号经过长线传输后,传输线效应削弱了滤波效果;

- 在PCB1侧加共模电感,无效果;

- 在PCB1侧加磁环,有效果;

以上四中方法中1)和2),原因分析比较常见,后续针对3)和4)进行机理分析。

4.3 同轴线抗扰性能

同轴线或屏蔽线的EMS性能可以通过屏蔽效率来表征,包括屏蔽效能和转移阻抗两方面评估,GB/T117738.1标准中评价同轴线的屏蔽效率的测试方法参见图7所示。同轴线的CS测试从这个角度来看也是考量同轴线线缆的屏蔽效率特性。

4.3.1 屏蔽效能

(1)传输线等效电路分析

CS的干扰注入同轴线屏蔽层的等效电路图参见图8所示,其中Z1为流量检测仪内阻、Z2位传感器内阻、Vnoise为CS信号发生器通过EM clamp耦合到屏蔽层的干扰电压、VCSG为CS发生器的注入噪声电压、Z3和Z4为clamp EM阻抗、 Z5为EM clamp与同轴线屏蔽层的耦合阻抗、Z6和Z7为同轴线屏蔽层阻抗、ZCSG为CS发生器内阻、ZCS为耦合夹侧负载阻抗、Zc1为流量检测仪对地分布电容阻抗、Zc2为传感器侧对地分布电容阻抗。为进行量化分析,本文在20MHz下将同轴线的参数评估约为:Z1为 95Ω,Z2为95Ω,Z5为95Ω,Z3、Z4、Z6和Z7为0.1Ω,Zc1和Zc2为1nF。

由图8(b)可计算出屏蔽层耦合的噪声Vnoise:

Z5可表征EM clamp与同轴线屏蔽层的耦合效率阻抗,Z6和Z7可表征同轴线屏蔽层的屏蔽效能。当理想情况下Z6和Z7的阻抗为0,则Vnoise=0。Z5为0时,EM clamp的耦合效率最高。Z5为∞时,EM clamp的耦合效率最低。

实际的同轴线在使用过程中,需要选用屏蔽效能好的电缆,同时注意现场噪声源和线缆间的耦合阻抗,阻抗越大越好,即等效距离越大越好。

(2)EM clamp耦合效率分析

EM clamp在干扰耦合时,其耦合效率随着频率变化而变化,标准中EM clamp的耦合效率测试布局参见图9,测试结果参见图10。

EM clamp的测试电路是在300欧姆回路阻抗的前提下,进行2端口s参数测量,S21即表示耦合因数。由图10可知10MHz的耦合因数为-3db(150Ω两端电压约为0.69Vcsg),20MHz的数耦合因数为-1.5db(150Ω两端电压约为0.84Vcsg)。

当测试3V等级Upp达到了15.27V时,Vnoise≈15.27mV,可见传感器的敏感度很高,很小的电压就会被干扰,设计需要重点考虑。

4.3.2 转移阻抗

转移阻抗是指在屏蔽层上流过的电流I,在屏蔽层与芯线间产生的电压V,即Zt=V/I。屏蔽层上流过的电流I,在屏蔽层阻抗上产生干扰电压Vnoise,PCB1端的干扰为Vnoise在Z1上产生的电压,来评估Z1两端的干扰强弱。

Z1为流量检测仪内阻、Z2位传感器内阻、Z3-Z7位同轴线的传输阻抗、Zpe为同轴线两端对地的分布阻抗:

Z5表征转移阻抗,Z5为0时,Vz1的转移效率最高。Z5为∞时,Vz1的转移效率最低。同轴线线缆选型时注意转移阻抗参数。

4.4 抑制措施分析

同规格不同厂家的同轴线的屏蔽效能是不同的,但因同轴线线不可更换,下面重点对转移阻抗结合滤波措施进行分析。

4.4.1 共模电感滤波

如图12所示,共模电感加在PCB1侧,其100MHz阻抗为共模200Ω左右,差模阻抗仅仅10Ω(2*Zdm)。

经分析对共模电感的加入对Z1两端的电压分压影响较小,这也是加入共模电感后,没有效果的原因。

4.4.2磁环滤波

屏蔽线缆加磁环参见图13所示,因屏蔽层的屏蔽作用,同轴线内部芯线内电流产生的磁场被屏蔽层中产生的涡流抵消,使得同轴线芯线产生的磁场无法链过磁环,内部芯线不会产生阻抗。

整改加入的磁环在20MHz约有300Ω(1匝),可计算出Vz1=0.21Vnoise;两匝阻抗约1200Ω,可计算出Vz1=0.07Vnoise,噪声被很好的衰减了。

5. 设计落地

设计落地方案三种:

- 同轴线外加磁环方案

- BNC和磁环一体结构件方案

- 同轴线和磁环一体线缆方案

方案(1)最简单方便,但涉及磁环如何固定,需要结合震动实验进行权衡设计;方案(2)的一体结构件设计,可作为选配件应用到同类产品中,适应场景灵活性高,但成本较高;方案(3)做成了标配线缆,但实际客户应用时的线缆长度不定,从方案落实困难,需要限定客户应用线缆长度。最终采取方案(1)进行落地。

6. 思考与启示

- 传感器类器件较敏感,一般容易受到干扰,设计时需要考虑实际的应用场景和测试要求,在设计端预留滤波措施;

- 同轴线为噪声的耦合传输路径,屏蔽效能和转移阻抗很好的评定同轴线的性能,设计时尽量选择转移阻抗小屏蔽效能高的线缆;

- 同轴线加磁环后,内部芯线因同轴线屏蔽层屏蔽效应,使得内部芯线电流产生的磁场无法链过磁环,因此加磁环前后内部芯线阻抗无变化。

- 同轴线应用场合下,注意差共模的转化机理,本文中的共模电流主要从屏蔽层中流过,通过转移阻抗转化为差模影响敏感设备;

- 共模电感在同轴线抗扰抑制方法中不是最优选择,需要结噪声和路径机理分析,选择合适的滤波器件。

-

极细同轴线与传统射频同轴线区别有哪些?2025-09-18 2301

-

75欧姆同轴线缆解析2024-09-09 3836

-

BNC同轴线在直流信号测量中的应用2024-08-01 1648

-

同轴线缆与三同轴线缆的结构与应用的差异2024-05-11 3644

-

LMI宣布正式发布Gocator® 4000系列智能3D同轴线共焦传感器2024-04-18 1825

-

同轴线测电源噪声的测试方法2024-01-11 2178

-

射频同轴线缆失效的3大原因2023-11-28 2537

-

射频工程师必备知识-同轴线2020-10-30 7135

-

同轴线变换器怎么分析?2019-08-19 2810

-

电子系统EMC设计中的同轴线接地方法研究2018-01-09 1778

-

同轴线的结构及分类2017-09-07 5015

-

圆波导和同轴线的分析 PPT下载2009-11-02 2817

-

π-TM610模同轴双间隙腔耦合同轴线输出电路2009-10-29 836

全部0条评论

快来发表一下你的评论吧 !