聊聊寄存器被优化的2种情况

电子说

描述

在项目初期,在使用FPGA工具quartus或者vivado生成版本烧入开发板进行调试时(DC开启优化选项后同样会优化掉寄存器),我们有时会发现部分寄存器被优化掉了,今天简单聊聊被优化的几种情况。

1、寄存器被优化的原因

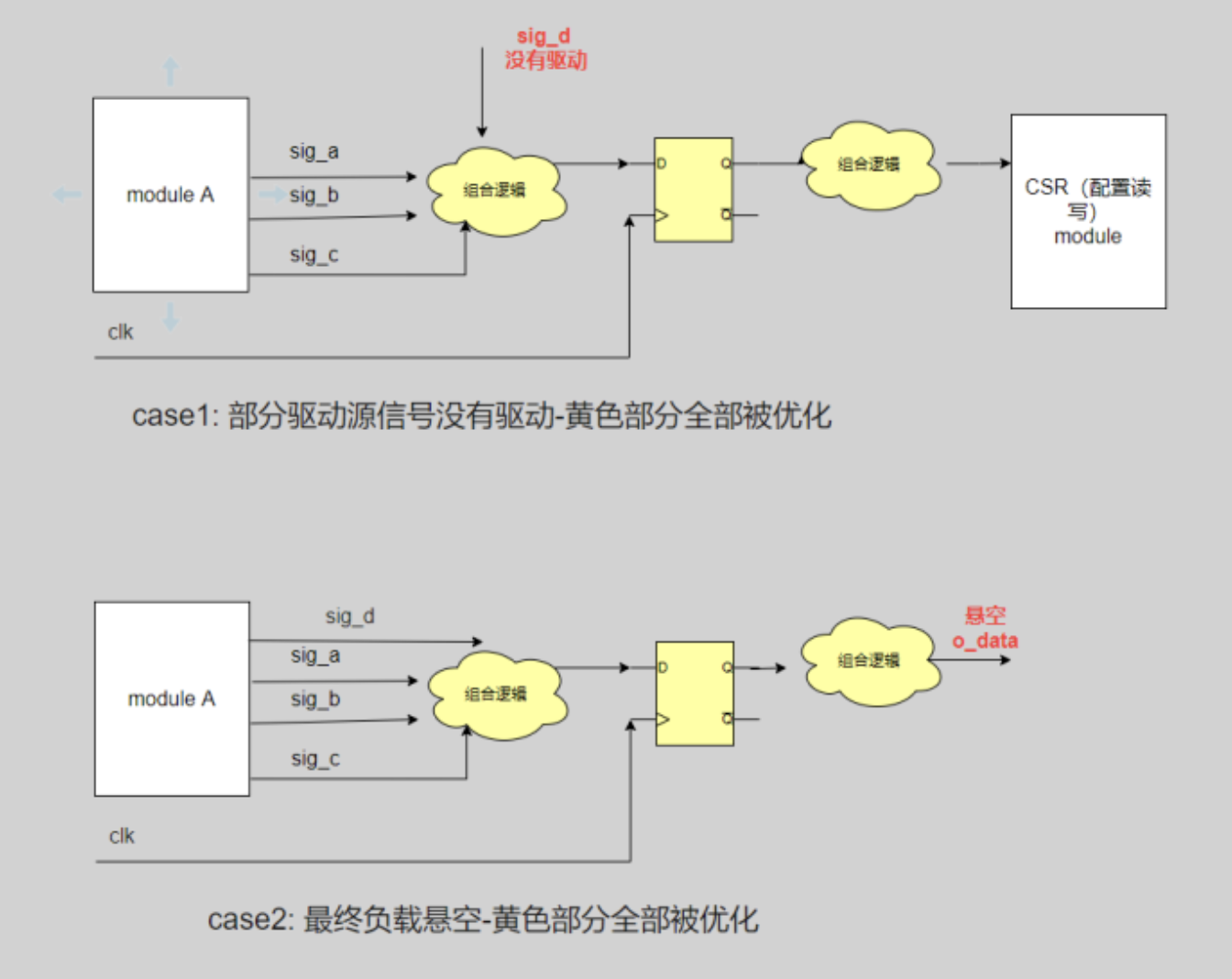

目前鸽子发现寄存器被优化的原因主要有两种:

1)驱动寄存器的信号没有驱动源

a. 至少有一个信号没有驱动源,也可能是多个

2)寄存器负载是悬空的,包含如下场景

a. 寄存器的唯一负载时悬空

b. 寄存器的所有负载均悬空

部分场景下被优化的问题很好排查,有些场景排查会比较麻烦,仅仅从信号连线上看都是正常的,无法通过肉眼快速发现问题,这时候需要去看综合报告,找到问题的源头。

2、案例--大量寄存器被优化

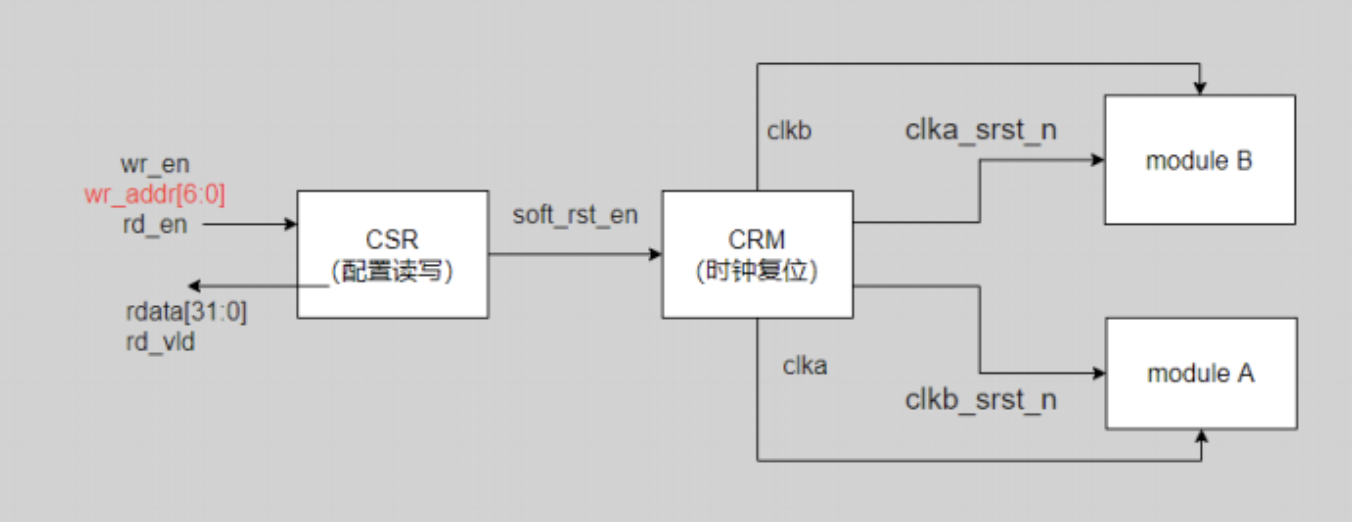

如下图所示,crm是复制产生时钟复位的模块,其中输出clka/clka_rst_n给模块a,其中输出clkb/clkb_rst_n给模块b。Soft_reset_n是clka_rst_n和clkb_rst_n的源头之一。Soft_reset_n为0,则clka_rst_n/clkb_rst_n为0,处于复制状态。Soft_reset_n是配置读写模块CSR的一个可配置寄存器,其内部偏移地址为0x60。

通过quartus/vivado查看网表结构和资源利用率,我们发现模块A和模块B大量资源被优化,不符合常理。经过检测发现,所有信号连接均正常,没有悬空,所有信号均存在负载。

经过反复排查后发现,CSR模块被手动添加的Soft_reset_n寄存器地址分配在0x60,而CSR入口wr_addr[5:0]只有6bit,只能访问0x40以内的地址范围,因此Soft_reset_n在实际网表中是不存在的,导致clka_rst_n/clkb_rst_n都没有驱动源,因此模块A和模块B大量资源被优化。

3、推荐检查方法

在进行FPGA版本调试之前,首先进行spyglass lint检查 或者检查quartus/vivado产生的综合报告,检查是否存在如下warning:

- 信号没有驱动

- 信号悬空

把这些warning确认完后再进行版本调试。

4、简单的规律

大量模块逻辑被优化,重点看时钟复位

少量模块逻辑被优化,重点看资源独享的驱动信号。

-

寄存器分为基本寄存器和什么两种2024-07-12 3278

-

浅谈寄存器被优化的原因2023-09-26 2523

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5493

-

ARM通用寄存器及状态寄存器详解2023-01-06 10004

-

ARM开发中几个常见的寄存器详解2022-11-22 5792

-

配置STM32寄存器控制GPIO点亮LED2022-01-13 1150

-

STM32学习笔记(2)——寄存器2021-12-08 1302

-

基于FPGA的可变长度移位寄存器优化设计2011-07-23 6093

-

寄存器与移位寄存器2010-03-12 988

-

寄存器,寄存器是什么意思2010-03-08 22423

全部0条评论

快来发表一下你的评论吧 !