serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

电子说

1.4w人已加入

描述

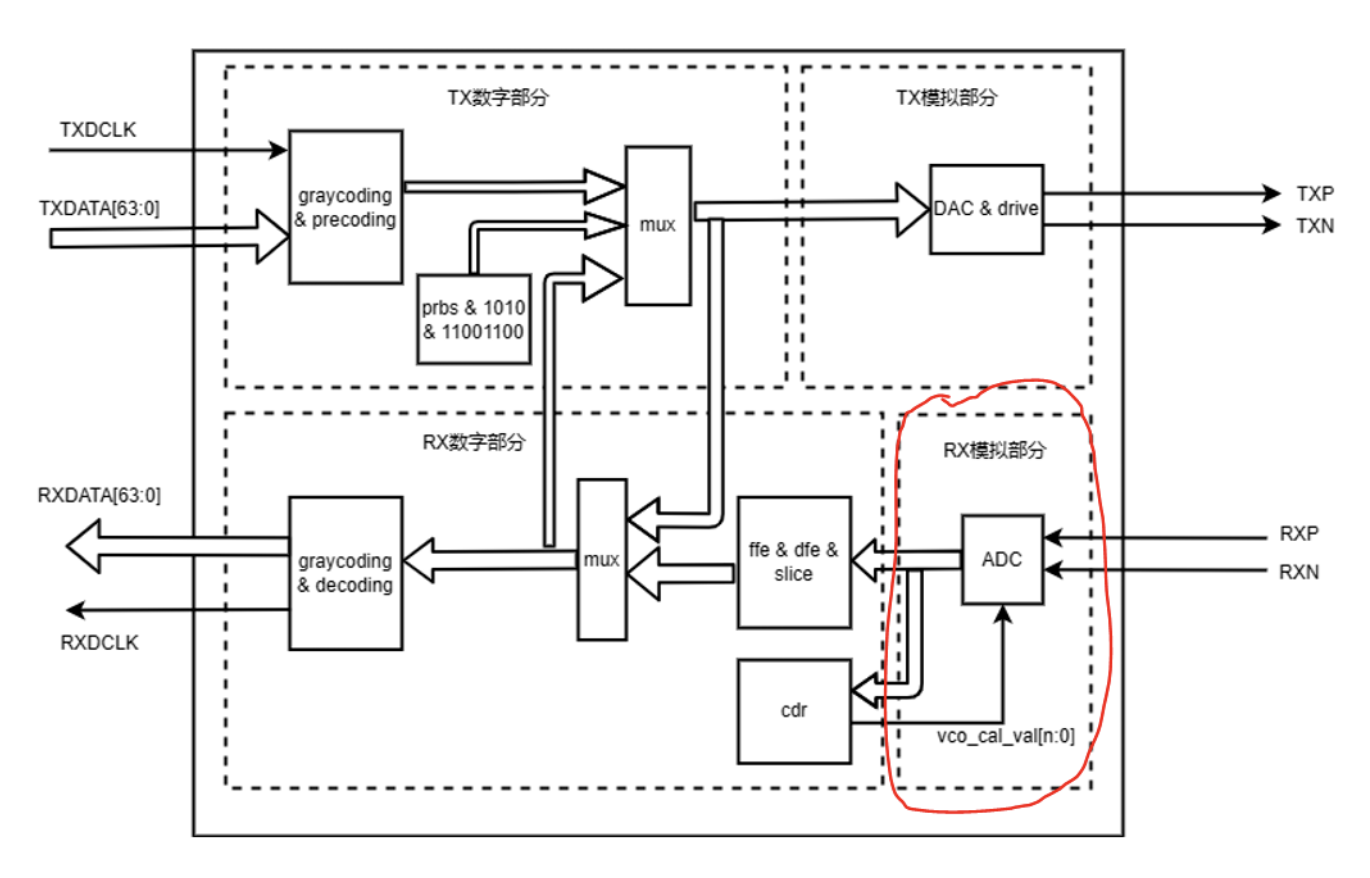

对于图1所示TX/RX模拟部分的实现方式,大家是不是一直有这样的疑问: Serdes在将并行data通过DAC串行发出去的时候,或者在接收端通过ADC进行串行data采样的时候,是怎么实现的?比如56G的serdes就是用56G的ADC和DAC吗?

答案是肯定不是,没有那么高频的ADC和DAC,通常ADC和DAC最大可以工作在1G频率左右,再大的频率无法实现精度的。所以采用多个ADC/DAC分时工作的模式。

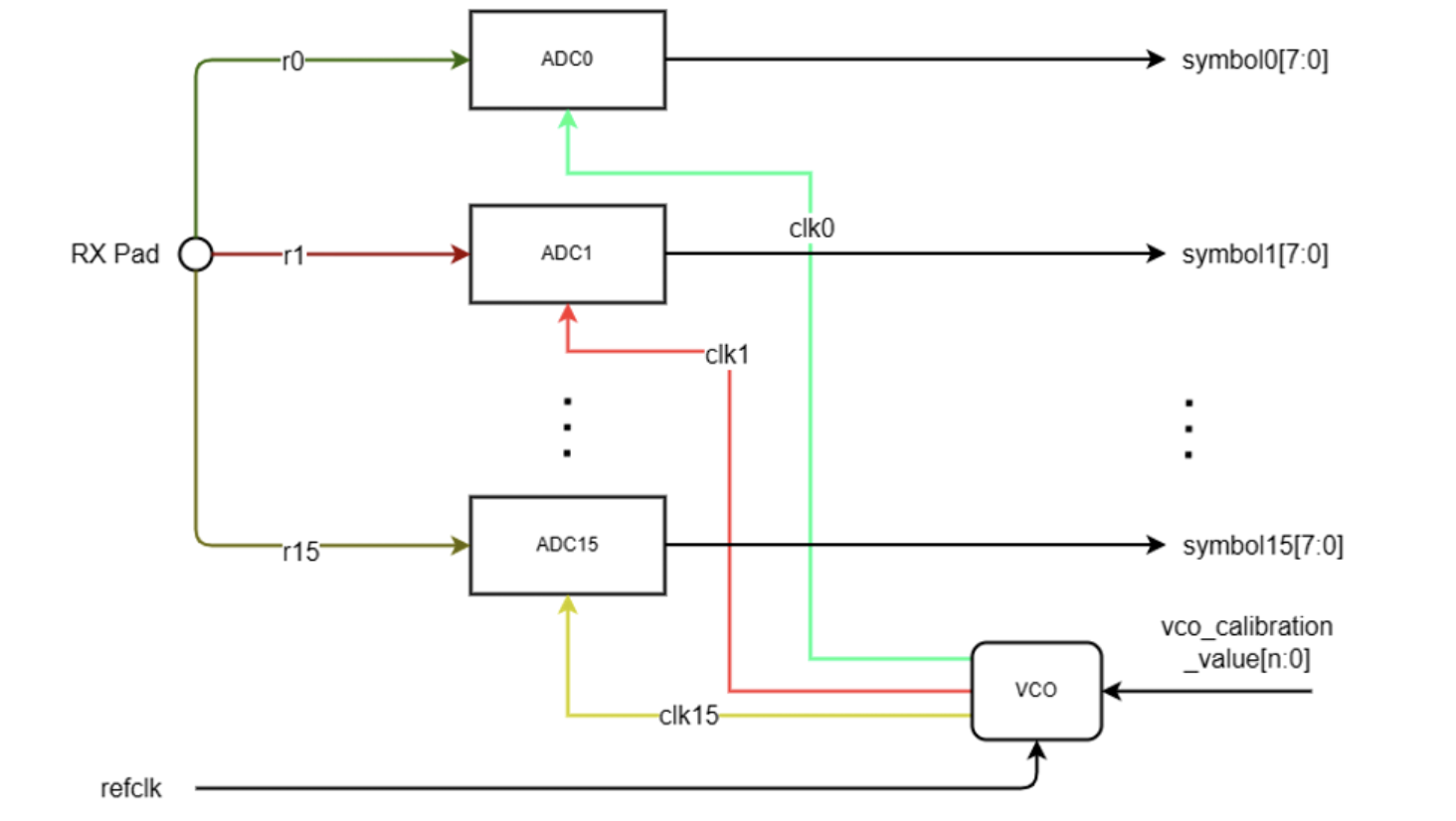

RX接收端采样方式如下图2,RX Pad连接到16个ADC上,后端要严格约束Pad到不同ADC之间的走线一样长,可以通过绕线方式实现。

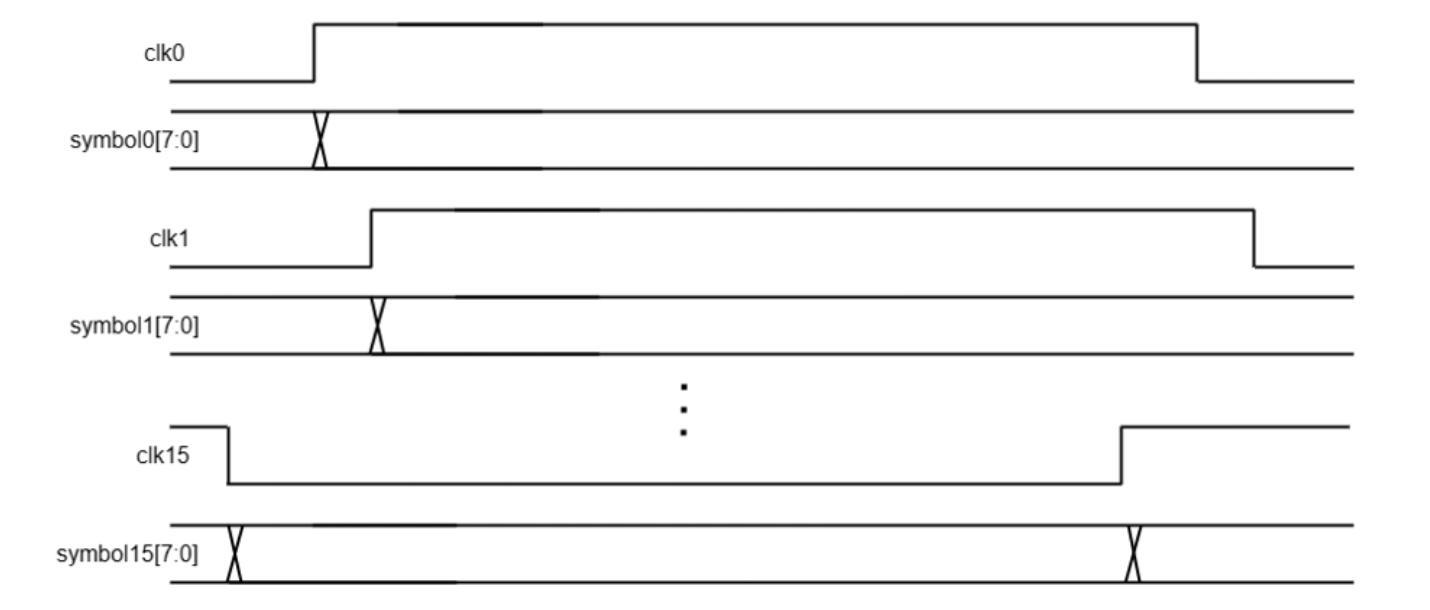

CDR的数字逻辑输出vco_calibration_value[n:0]到模拟VCO实现相位调整。VCO输出多路时钟到多个ADC,如图3所示,比如通过16个ADC分时采样,VCO输出的相邻时钟差90°/16。

ADC在时钟上升沿进行采样,然后模拟通过clk15将16个采样symbol[7:0] pipe到数字逻辑,然后进行均衡判决。TX端的DAC发送端是相同的方式进行的。

图1:serdes架构框图

图2:RX ADC采样框图

图3:RX ADC采样时钟图示

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SERDES的作用 SerDes基础知识详解2024-01-04 9334

-

从SerDes到SoC,全场景适配的FCom差分晶振设计全解2025-05-30 1108

-

SERDES接口电路设计2019-05-29 3774

-

FPGA SERDES接口电路怎么实现?2019-10-23 2426

-

SERDES传输和引脚关联2020-03-17 2222

-

SerDes的发送端TX的均衡原理是什么?2021-06-17 2235

-

SerDes是怎么工作的2021-07-28 2153

-

基于SERDES时钟的频率跟随的设计2017-11-18 8293

-

如何使用FPGA实现SERDES协议2020-10-09 2268

-

单通道56G的SERDES,参考时钟如何选取?2020-11-12 6176

-

SERDES的优势 SERDES演变的看法2021-07-23 5554

-

56G QSFP+DAC无源高速线缆的详细介绍2022-04-25 3627

-

什么是SerDes?SerDes的应用场景又是什么呢?2023-06-06 14374

-

SerDes:串行和并行通信有何区别?2023-10-20 3096

-

了解高速56G PAM-4串行链路的时钟需求2024-09-23 447

全部0条评论

快来发表一下你的评论吧 !