FPGA学习-异步复位,同步释放

描述

点击上方蓝字关注我们

系统的复位对于系统稳定工作至关重要,最佳的复位方式为:异步复位,同步释放。以下是转载博客,原文标题及链接如下:复位最佳方式:异步复位,同步释放

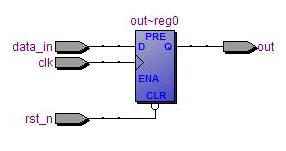

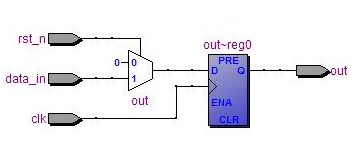

异步复位;

异步:

always @(posedge clk or negedge rst_n )

if(!rst_n)

(优点:占用较少逻辑单元

缺点:可能会产生竞争冒险)

同步:always @(posege clk or posedge rst_n)

If(!rst_n)

(优点:可以尽量点少竞争冒险的可能

缺点:会占用更多的逻辑单元)

Altera 最佳解决办法:异步复位,同步释放

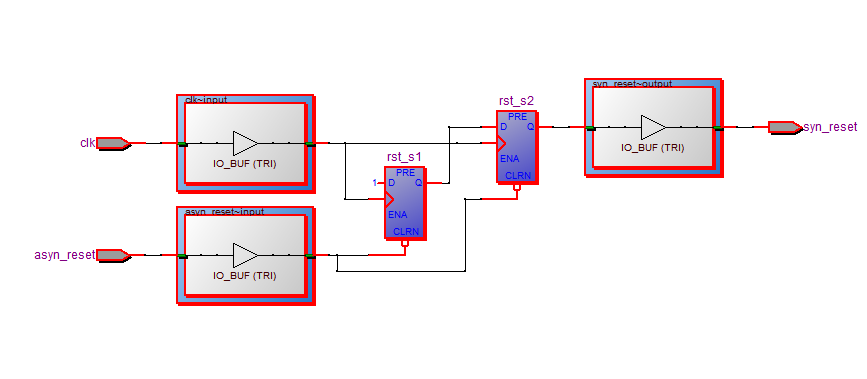

//异步复位 同步释放rtl视图

原理:

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

下面说明一下如何实现异步复位和同步释放的。

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件(在始终上升沿附近rst置1,这时候建立时间还不够长,数据可能还未打入寄存器,导致输出不确定)。但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器次clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

代码实现:(Altera 官方资料)

module reset_best(clk,asyn_reset,syn_reset);

input clk;

input asyn_reset;

output syn_reset;

reg rst_s1;

reg rst_s2;

always @( posedge clk ,posedge asyn_reset)

begin

if(asyn_reset)

begin

rst_s1<=1'b0;

rst_s2<=1'b0;

end

else

begin

rst_s1<=1'b1;

rst_s2<=rst_s1;

end

end

assign syn_reset=rst_s2;

endmodule

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、9月23号北京中心开课、欢迎咨询! FPGA学习:精简指令集RISC_CPU 至芯FPGA初级课程之 FIFO

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-异步复位,同步释放

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

verilog 异步复位同步释放2013-05-28 3395

-

同步复位与异步复位,同步释放的对比疑问2014-04-16 2854

-

关于异步复位同步释放理解与分析2017-11-30 25533

-

FPGA设计中的异步复位同步释放问题2018-06-07 2649

-

Xilinx FPGA的同步复位和异步复位2018-07-13 7722

-

异步复位同步释放的基本原理与代码举例2019-11-20 4948

-

利用FPGA异步复位端口实现同步复位功能,释放本性2020-08-18 1825

-

详细讲解同步后的复位是同步复位还是异步复位?2021-04-27 5976

-

【FPGA】异步复位,同步释放的理解2022-01-17 746

-

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?2023-06-21 2399

-

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略2023-07-20 2973

-

同步复位与异步复位的区别2023-08-14 8975

-

浅析异步复位同步释放与同步复位打拍模块2023-08-21 1968

-

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?2024-01-24 2961

-

FPGA同步复位和异步复位2024-07-17 3721

全部0条评论

快来发表一下你的评论吧 !