为什么使用CubeMx配置NVIC时不见子优先级选项

描述

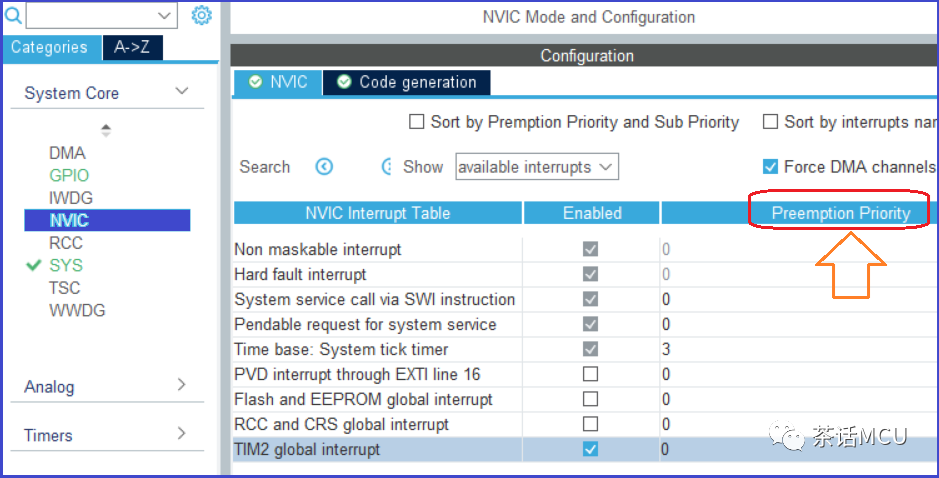

有些STM32用户,尤其是那些用过基于ARM Cortx-M3/M4/M7内核的STM32 MCU的用户,在使用基于M0/M0+内核的STM32系列并通过STM32CubeMx进行NVIC配置时,不难发现一个问题,那就是怎么没有中断子优先级【或称响应优先级、副优先级等】的配置?!【当然,很多时候我们或许没有关注子优先级】如下图所示,只看到抢占优先级的配置,看不到子优先级的配置项。

上图是我基于STM32L0系列芯片的配置,该系列芯片是基于ARM Cortex-M0+内核的。我们再看看下图的NVIC配置页面,显然可以看到抢占优先级【Preemption Priority】和子优先级【Sub

Priority】的配置项及相关信息。

上图是我基于STM32G4系列芯片的NVIC配置页面。该系列的内核是ARM Cortex-M4。

当我们使用STM32系列芯片并通过CubeMx图形化工具进行NVIC配置时,相应界面有无子优先级的配置,取决于该系列芯片所用的ARM Cortex内核。如果说所用STM32系列是基于ARM Cortex-M0或M0+内核的,在进行NVIC配置时是没有子优先级可以配置的。

ARM Cortex-M0或M0+内核的中断优先级控制寄存器实际有效位就是2位,全部用来对各个中断/异常做抢占优先级配置,不额外划分子优先级的配置。

也就是说,基于ARM Cortex-M0或M0+内核的STM32 MCU的NVIC配置不会有子优先级的概念和配置,对于优先级可配置的中断而言,总共就4个可抢占优先级。下图是基于ARM Cortex-M0或M0+内核的STM32系列展示。当然,STM32系列涉及的内核很多,远不止下面这些,还有M4/M7/M33等。

而ARM Cortex-M3、M4、M7内核的中断优先级配置寄存器的有效位为4位,同时还可以基于该4位做优先级的分组,进而引出抢占优先级和子优先级。

-

抢占优先级和子优先级2025-12-03 155

-

STM32F103的寄存器NVIC_IPRx抢占优先级和子优先级是怎么设置的?2024-03-27 462

-

STM32中断没有子优先级?2023-10-17 1846

-

STM32 MCU通过STM32CubeMx配置NVIC怎么没有中断子优先级选项2023-09-09 3295

-

关于STM32H725 NVIC优先级和次优先级问题求解2022-12-12 530

-

STM32 NVIC中断优先级设置的步骤有哪些2022-01-14 1825

-

2021-04-16 NVIC中断优先级管理2021-12-04 861

-

NVIC中断优先级管理简介2021-10-27 1988

-

stm32配置中断的优先级问题2021-08-13 1253

-

中断优先级配置的函数2021-08-04 1040

-

UCOS3的串口优先级配置问题如何解决2020-05-29 1904

-

NVIC中断优先级分组2017-03-26 1538

全部0条评论

快来发表一下你的评论吧 !